STM32F103没有提供标准的地址、数据和控制总线,但提供了极为丰富的GPIO资源,硬件电路设计的基本原理就是将GPIO映射为PC104的地址、数据和控制总线。另一方面,STM32F103为3.3 V供电的系统,尽管大部分GPIO可以接受5VTTL电平输入,但是,其输出驱动最高高电平小于3.3 V,难以完全保证可靠驱动5VTTL的设备,因此,要进行电平转换。下面以PC104总线IO操作为例,分别予以介绍。

6.1.2.1 地址、数据和控制总线的产生

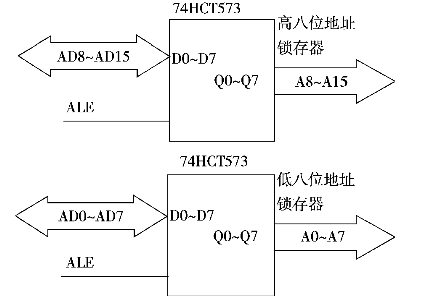

设计中利用两组16位GPIO端口PD与PE构建PC104总线,PD作为控制总线,PE作为地址/数据复用总线。地址、数据的分离是通过控制总线中的ALE(PD4)和两片锁存器74HCT573实现的。当ALE为高电平时,PE上输出地址;当ALE为低电平时,PE上传输数据,如图6-1所示。

图6-1 地址数据总线及地址锁存原理方框图

PC104控制总线信号有三十多条,但常用的只有几条,因此,设计中只选取其中常用的信号,如果实际中需要更多的控制总线信号,可以再增加GPIO端口,例如,将PA端口纳入其中。下面介绍PC104总线IO操作常用的控制总线信号产生及应用。

AEN是总线使能信号,AEN为低,由CPU接管总线控制权,否则,DMA控制器接管总线控制权。

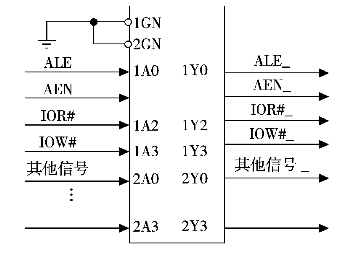

ALE为地址锁存信号,高电平有效,其高电平将地址总线上的地址锁存到设备地址缓冲区。IOW#为端口写信号,低电平有效,其上升沿将数据总线上的数据锁存到设备数据缓冲区。IOR#为端口读信号,低电平有效,其上升沿将数据总线上的数据锁存到CPU数据缓冲区。IOCS16#,低电平有效,该信号产生于IO端口设备,通知CPU设备将接受一次16位总线操作,如图6-2所示。(https://www.daowen.com)

图6-2 控制总线的电平转换

6.1.2.2 电平转换

由于STM32F103采用3.3 V供电,尽管大部分GPIO可以接收最高5V逻辑电平,但是,在输出驱动时其最高高电平不超过3.3 V,因此,直接将GPIO端口作为PC104总线使用,不完全符合PC104总线的规范。设备板卡中若有采用5 V CMOS集成电路时,会导致高电平驱动不可靠。为了解决这一问题,需要进行电平转换。

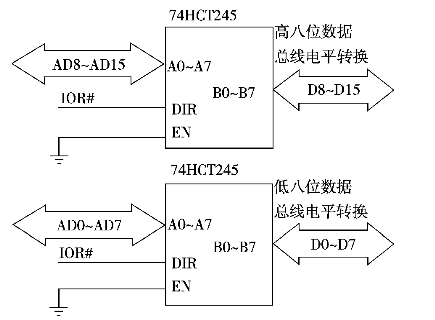

由于74HCT系列是5VTTL兼容的CMOS集成电路,而STM32F103的GPIO端口大部分也是5VTTL兼容端口,所以,采用图1所示的74HCT573锁存器,就实现了地址总线的电平转换。控制总线的电平转换可以采用74HCT244或74HCT541等数据缓冲器实现,如图6-2所示。数据总线的电平转换则采用八总线收发器74HCT245实现,其方向控制DIR引脚由IOR#控制,使能端接低电平(即总是有效),如图6-3所示。由于IOCS16#信号是由设备产生的,且选用的是STM32F103的5V兼容GPIO,可以承受5V的逻辑电平,因此不需要电平转换。

图6-3 数据总线的电平转换

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。