1.装载(LD)、装载非(LDNOT)和输出(OUT)、输出非(OUTNOT)指令

(1)装载指令(LD)

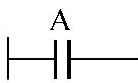

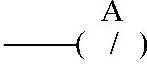

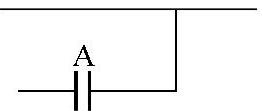

格式:LD A 符号:

A位的操作数区域:CIO,W,H,A,T,C,TK或TR等。

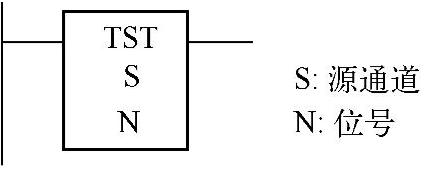

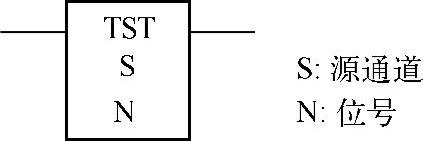

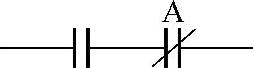

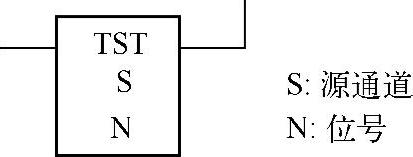

装载指令的功能是将某一常开触点与母线连接,或作为电路块的起点。而LD型位测试指令LDTST(350)与LD指令功能相同,其符号如下:

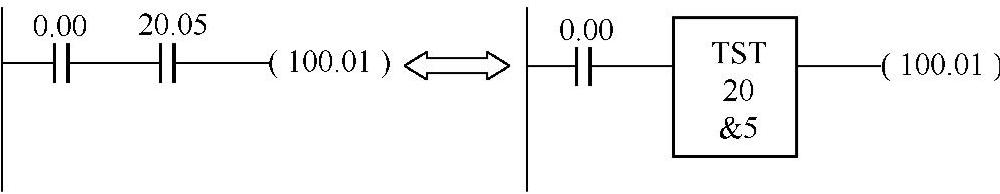

与LD等价的LDTST梯形图如图3-3所示。

图3-3 LDTST梯形图示例

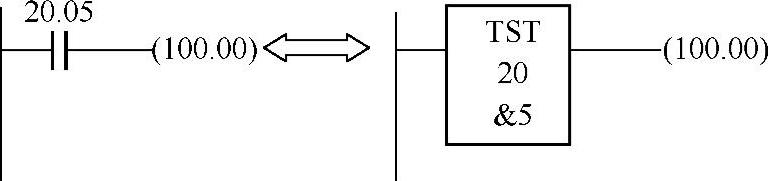

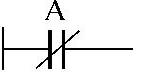

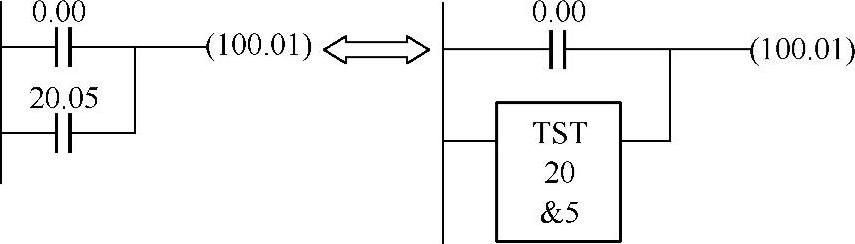

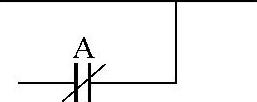

(2)装载非指令(LD NOT)

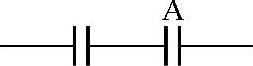

格式:LD NOT A 符号:

A位的操作数区域:CIO,W,H,A,T,C或TK等。

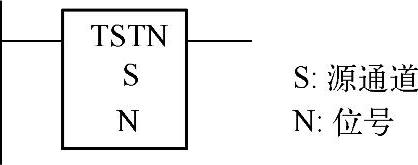

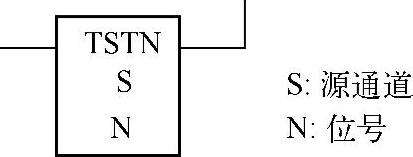

装载非指令的功能是将某一常闭触点与母线连接,或作为电路块的起点。而LD型位测试非指令LDTSTN(351)与LD NOT指令功能相同,其符号如下:

与LD NOT等价的LDTSTN梯形图如图3-4所示。

图3-4 LDTSTN梯形图示例

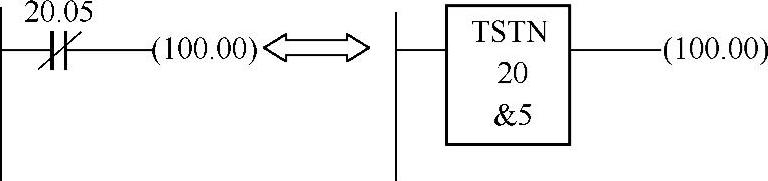

(3)输出指令(OUT)

格式:OUT A 符号:

A位的操作数区域:CIO(输入卡占用的位不能使用),W,H,TR或A44800~A95915。

输出指令的功能是将逻辑运算结果(输入条件)输出到指定线圈。需要说明的是:

1)在一条逻辑行的起始处均要使用LD或LD NOT指令,当逻辑行的开始为常开触点时,使用LD指令;反之使用LDNOT指令。

2)OUT指令不能用于驱动输入继电器。

3)OUT指令可以同时并联驱动多个继电器线圈,示例见例3-1。

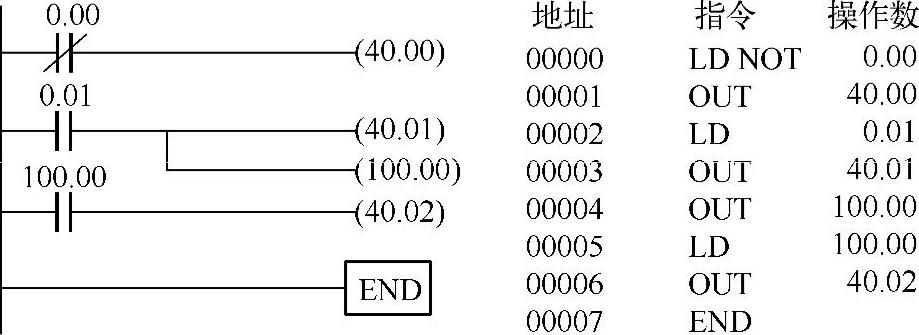

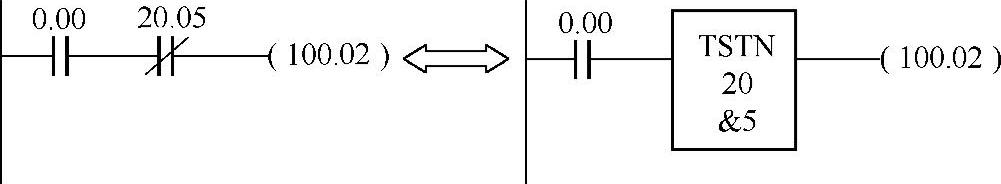

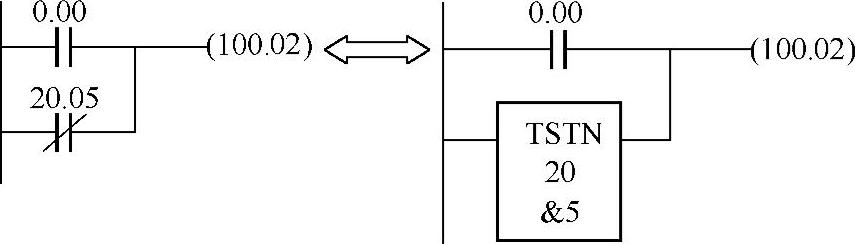

【例3-1】 LD,LD NOT,OUT指令的梯形图与助记符示例如图3-5所示。

图3-5 LD,LD NOT,OUT梯形图和助记符示例

(4)输出非指令(OUT NOT)

格式:OUT NOT A 符号:

A位的操作数区域:CIO(输入卡占用的位不能使用),W,H,TR或A44800~A95915。

输出非指令的功能是将逻辑运算结果(输入条件)取反并输出到指定线圈。

2.与(AND)和与非(AND NOT)指令

(1)与指令(AND)

格式:AND A 符号:

A位的操作数区域:CIO,W,H,A,T,C或TK等。

与指令的功能是串联一个常开触点。AND型位测试指令ANDTST(350)与AND指令功能相同,其符号如下:

与AND等价的ANDTST梯形图如图3-6所示。

图3-6 ANDTST梯形图示例

(2)与非指令(AND NOT)

格式:AND NOT A 符号:

A位的操作数区域:CIO,W,H,A,T,C或TK等。

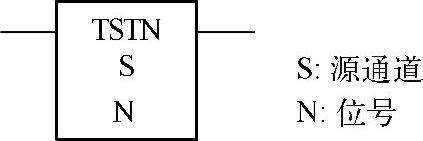

与非指令的功能是串联一个常闭触点。AND型位测试非指令ANDTSTN(351)与AND NOT指令功能相同,其符号如下:

与AND NOT等价的ANDTSTN梯形图如图3-7所示。

图3-7 ANDTSTN梯形图示例

需要说明的是:

1)AND和AND NOT指令是只用于串联一个触点的指令。串联触点的数量不限,即可多次使用AND或AND NOT。

2)“连续输出”是指在执行OUT指令后,通过与继电器触点的串联可驱动其他线圈执行OUT指令。连续输出只要电路设计顺序正确,可连续驱动多个线圈输出。示例见例3-2。

【例3-2】 AND,AND NOT指令的梯形图与助记符示例如图3-8所示。

图3-8 AND,AND NOT梯形图和助记符示例

3.或(OR)、或非(ORNOT)指令

(1)或指令(OR)

格式:OR A 符号:

A位的操作数区域:CIO,W,H,A,T,C或TK。

或指令的功能是并联一个常开触点。OR型位测试指令ORTST(350)的功能相同,其符号如下:

与OR等价的ORTST梯形图如图3-9所示。

图3-9 ORTST梯形图示例

(2)或非指令(OR NOT)

格式:OR NOT A 符号:

A位的操作数区域:CIO,W,H,A,T,C或TK。

或非指令的功能是并联一个常闭触点。OR型位测试非指令ORTSTN(351)的功能相同,其符号如下:

与OR NOT等价的ORTSTN梯形图如图3-10所示。

图3-10 ORTSTN梯形图示例

需要说明的是:

1)OR、OR NOT是只用于并联一个触点的指令。并联多个串联触点不能使用此类指令。

2)OR、OR NOT指令引起的并联,是从OR或OR NOT一直并联到前面最近的LD或LDNOT指令上,并联的数量不受限制。示例见例3-3。

【例3-3】 OR,OR NOT指令的梯形图与助记符示例如图3-11所示。

(https://www.daowen.com)

(https://www.daowen.com)

图3-11 OR,OR NOT梯形图和助记符示例

4.逻辑块或指令(ORLD)

格式:OR LD符号:

两个或两个以上的触点串联构成的逻辑电路称为“串联逻辑块”。

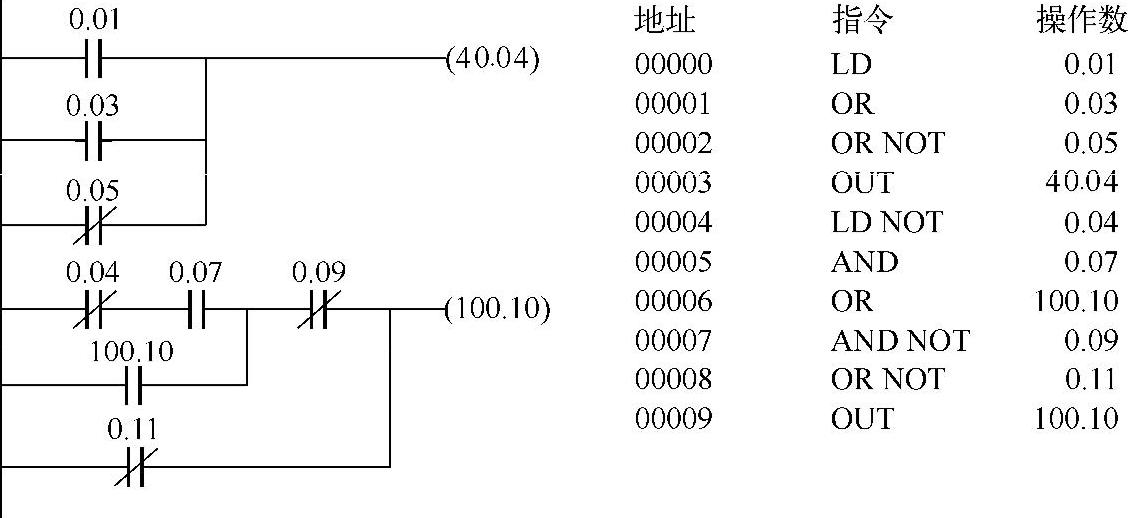

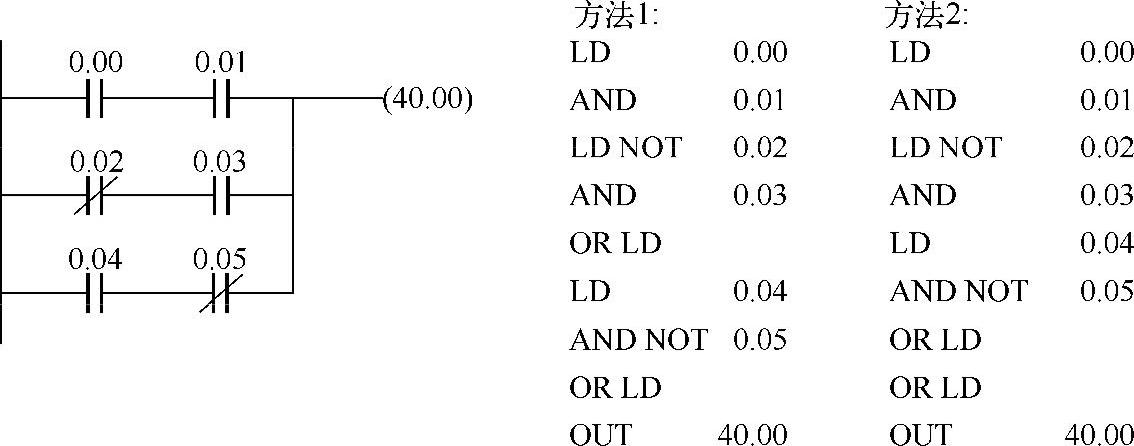

逻辑块或指令的功能是在并联串联逻辑块时,在支路起点要用LD或LD NOT指令,而在该支路终点要用OR LD指令。采用该指令编程有两种不同的方法,见例3-4。

【例3-4】 OR LD的梯形图与助记符示例如图3-12所示。

图3-12 OR LD梯形图和助记符示例

需要说明的是:

1)第一种方法是并联每一个串联逻辑块后加OR LD指令;第二种方法是将OR LD指令集中起来使用,但这样做串联逻辑块的个数不能超过8个,而第一种则没有限制。

2)OR LD指令是一条独立指令,它不带任何操作数。

5.逻辑块与指令(ANDLD)

格式:AND LD 符号:

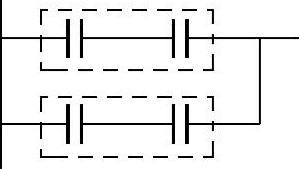

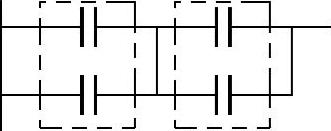

两个或两个以上触点并联构成的逻辑电路称为“并联逻辑块”。

逻辑块与指令的功能是当并联逻辑块与前面电路串联连接时用AND LD指令,并联逻辑块的起点用LD或LD NOT指令,在用AND LD指令将并联逻辑块与前面电路串联连接前,应先完成并联逻辑块内的编程。示例见例3-5。

【例3-5】 AND LD的梯形图与助记符示例如图3-13所示。

图3-13 AND LD梯形图和助记符示例

需要说明的是:

1)若有多个并联逻辑块顺次用AND LD指令与前面电路连接,则其使用次数可不受限制;但若将AND LD集中起来使用,如同OR LD指令一样,这种并联逻辑块的个数不能超过8个。

2)AND LD指令也是一条独立指令,它不带任何操作数。

以上指令均采用常用指令的用法,由第2章PLC的工作流程可知,这些常用指令是将前次I/O刷新的数据带到下一个扫描周期运行程序后,再将结果在I/O刷新阶段输出。这里所说的I/O刷新是指CPU的内部存储器与CPU单元内置的输入/输出端子及CPM1A系列扩展(I/O)单元之间的数据交换。

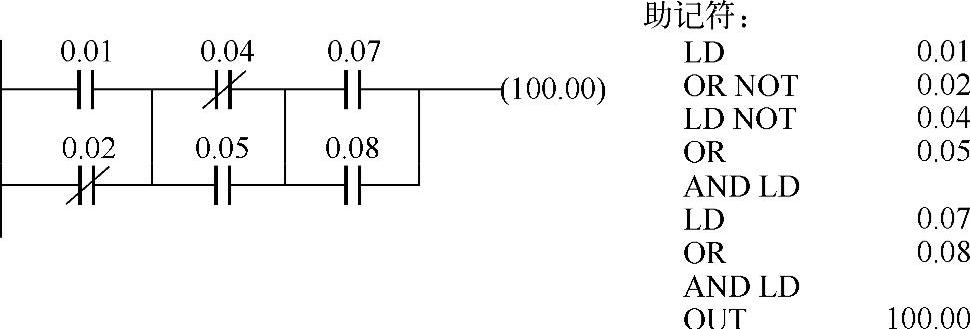

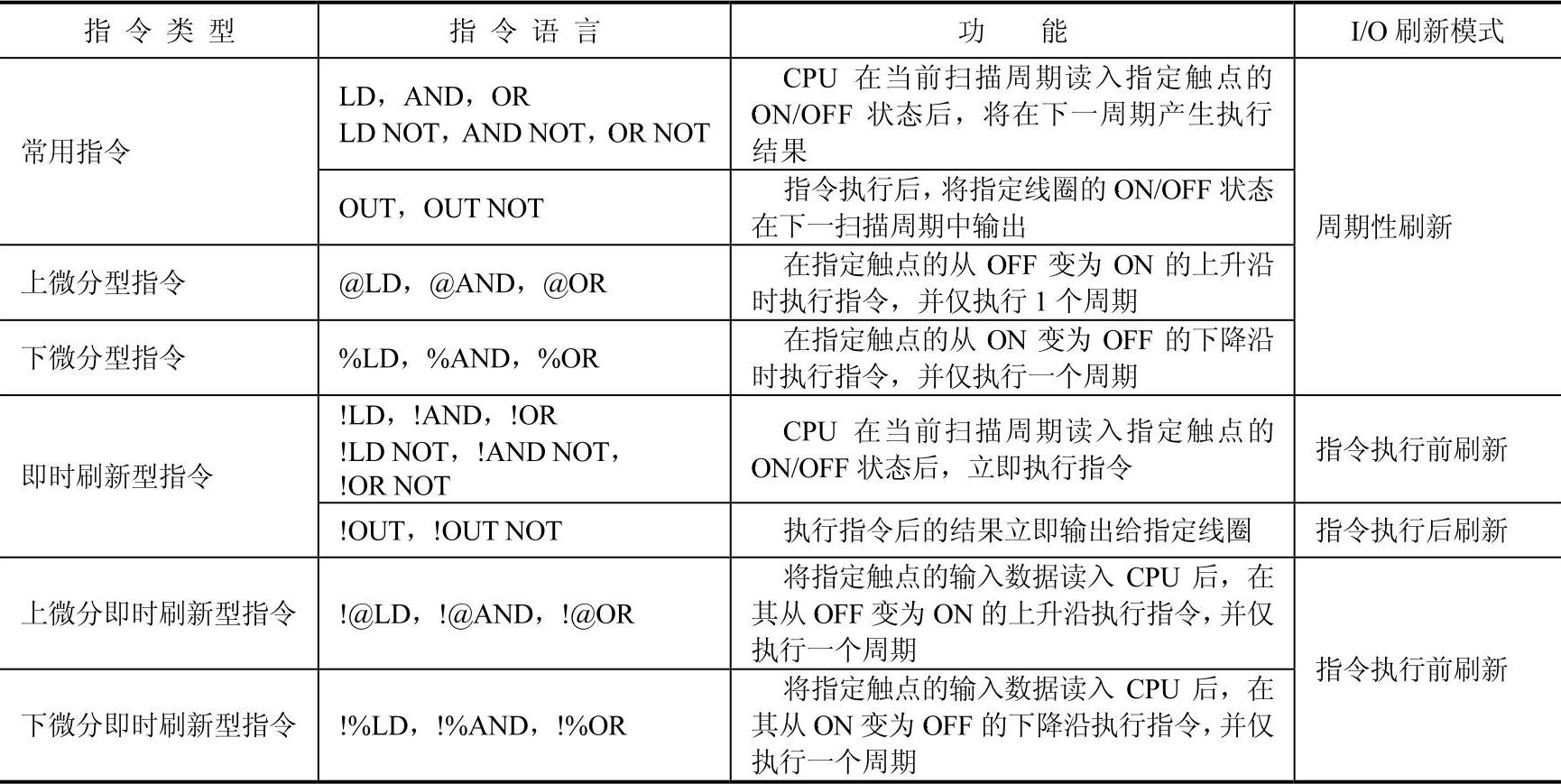

除常用指令用法外,还有微分型指令和即时刷新型指令(符号为“!”)以及二者组合型指令等三种用法,其中微分型指令又分为上微分型指令(符号为“@”)和下微分型指令(符号为“%”)。这三种用法与常用指令用法的最大区别在于指令所处理的数据的输入/输出时序不同,如图3-14所示。表3-1列举了不同指令用法的功能和区别。

图3-14 常用指令、微分型指令与即时刷新指令对比示例

表3-1 微分型与即时刷新型指令表

注:即时刷新指令仅适用于CPU单元内置的输入/输出点,不能用于CPM1A系列的扩展I/O单元,后者可以使用IORF指令实现即时刷新功能。

图3-14中,输入点2.00在第一个I/O刷新段后为ON,经过了两个扫描周期后为OFF,因此运行梯形图中0#逻辑行时将在第二个I/O刷新段采集到2.00为ON的状态并执行常用输出指令,100.00在第三个I/O刷新段置位;而在采集到2.00为OFF的状态后的下一个周期使100.00复位。

当输入点2.00具有上微分型(1#逻辑行)或下微分型(2#逻辑行)时,将在第二个I/O刷新段采集到上升沿或在第5个I/O刷新段采集到下降沿,输出点100.01或100.02将在下一个I/O刷新段置位一个扫描周期。

当输入点2.00是即时刷新型时,运行3#逻辑行时立即采集到2.00为ON的状态并执行常用输出指令,使100.03在当前扫描周期内产生置位;当采集到2.00为OFF时立即在当前扫描周期将100.03复位。对比100.00的波形可见,100.03要早反应一个扫描周期。同理,运行4#逻辑行时输出刷新型指令使100.04在输入采样的同一扫描周期内产生置位或复位。

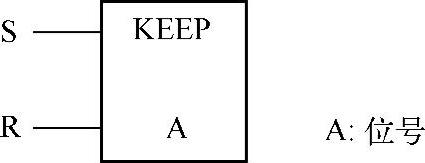

6.保持指令KEEP(011)

格式:

符号:

KEEP指令具有即时刷新型指令的特性,如!KEEP。

A位的操作数区域:CIO(I/O区中输入卡占用的位不能使用),W,H,A44800~A95915。

保持指令的功能相当于R-S触发器,它有两个输入端——置位输入端S和复位输入端R,当置位端条件从OFF变为ON时,KEEP将使被保持的位置位(ON)并一直保持,直到复位端条件从OFF变为ON时,才使被锁存的位复位(OFF)。置位和复位输入同时为ON时,复位端优先。示例见例3-6。

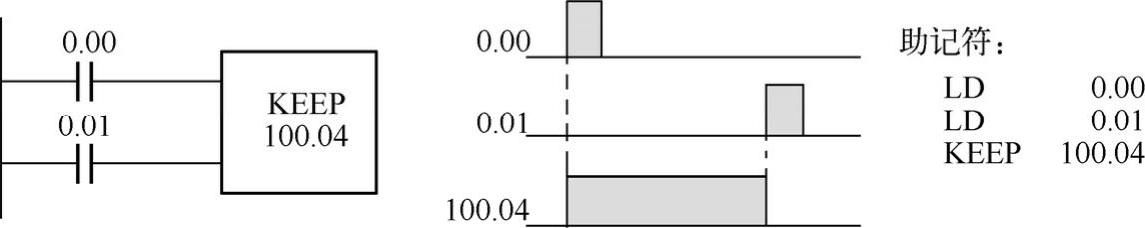

【例3-6】 KEEP指令的梯形图与助记符示例如图3-15所示。

图3-15 KEEP梯形图及波形图示例

上例中,当置位输入0.00闭合时,输出继电器100.04即导通(0.00上升沿触发)并自保持,只有当0.01闭合时,100.04才复位(0.01上升沿触发)。

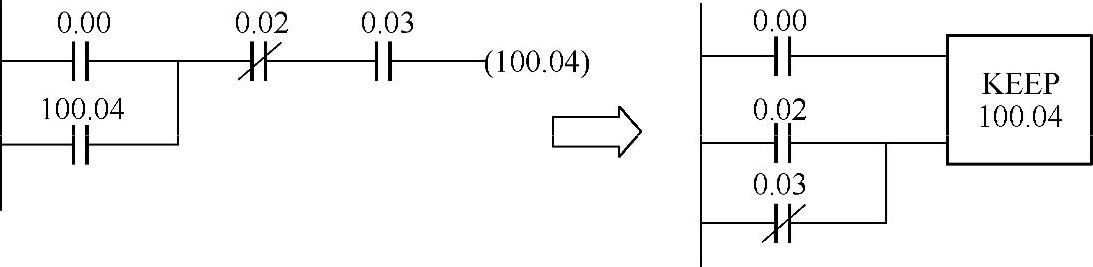

【例3-7】 自保持电路可以用KEEP指令代替,如图3-16所示。对比可以发现,自保持电路中的置位触点直接引用到KEEP指令的置位端;而两个复位触点取逻辑反后,串并联关系互换才能引用到KEEP指令的复位端。

图3-16 用KEEP代替自保持电路

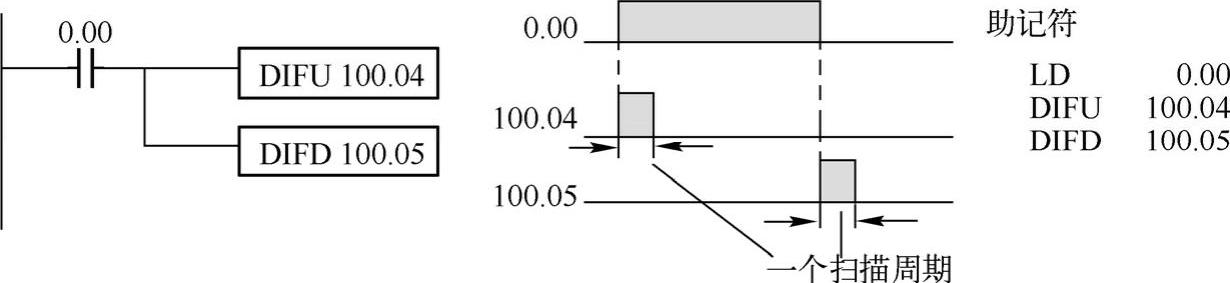

7.上微分指令DIFU(013)和下微分指令DIFD(014)

格式:

符号:

上微分与下微分指令具有即时刷新型指令的特性,如!DIFU,!DIFD等。

A位的操作数区域:CIO(I/O区中输入卡占用的位不能使用),W,H,A44800~A95915。

上微分指令DIFU(13)的功能是输入脉冲的上升沿使指定继电器闭合一个扫描周期,然后复位。下微分指令DIFD(14)的功能是输入脉冲的下降沿使指定继电器闭合一个扫描周期,然后复位。示例见例3-8。

【例3-8】 DIFU,DIFD的梯形图与助记符示例如图3-17所示。

图3-17 DIFU,DIFD梯形图及波形图示例

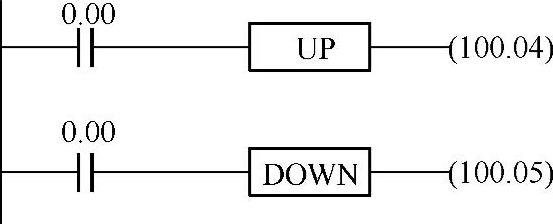

上例中,当0.00闭合时,其上升沿使100.04闭合一个扫描周期,而后断开;当0.00断开时,其下降沿使100.05闭合一个扫描周期,而后断开。DIFU和DIFD可以分别由条件ON指令UP(521)和条件OFF指令DOWN(522)替代,功能完全相同。示例见例3-9。

【例3-9】 UP,DOWN的梯形图与助记符示例如图3-18所示。

图3-18 UP,DOWN梯形图及波形图示例

在CP1H的指令系统中,某些高级指令也具有微分特性,指令前加@表示上微分型指令;加%表示下微分型指令。这类微分型指令将在执行条件满足后的第一个扫描周期内执行一次。

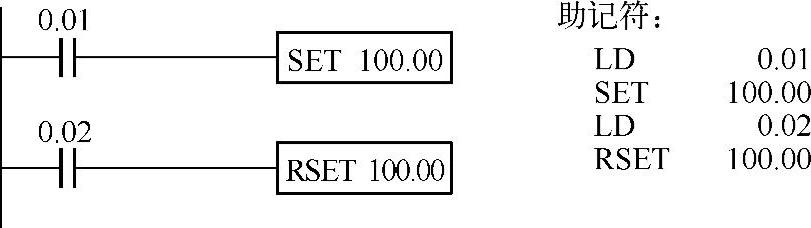

8.置位指令(SET)和复位指令(RSET)

格式:

符号:

置位与复位指令具有微分型和即时刷新型指令的特性。如@SET,%SET,!SET,!@SET,!%SET,@RSET,%RSET,!RSET,!@RSET,!%RSET等。

A位的操作数区域:CIO(I/O区中输入卡占用的位不能使用),W,H,A44800~A95915。

置位指令SET的功能是当执行条件为ON时,将指定位置位(ON);当执行条件由ON变为OFF时,指定位仍保持为ON,直至RSET指令将其复位。

复位指令RSET的功能是当执行条件为ON时,将指定位复位(OFF);当执行条件由ON变为OFF时,指定位仍保持为OFF,直至SET指令将其置位。示例见例3-10。

【例3-10】 SET,RSET的梯形图与助记符示例如图3-19所示。

图3-19 SET,RSET梯形图及助记符示例

注意:

1)SET和RSET指令不适用于定时器和计数器指令。

2)SET和RSET指令编在IL和ILC或JMP和JME指令间,当连锁或跳转条件符合(即IL或JMP指令处于OFF执行条件)时,SET和RSET指令控制的位不变。

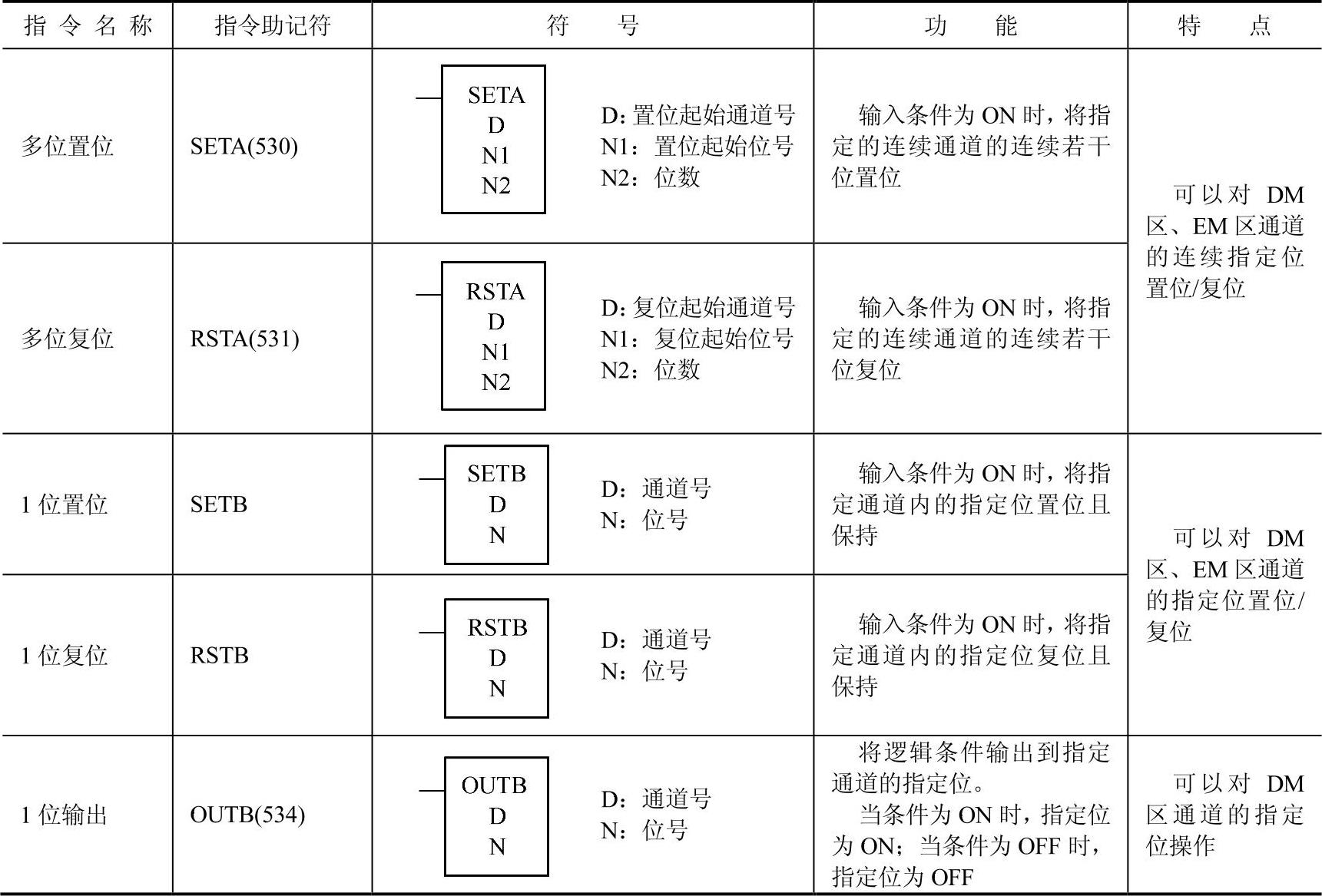

CP1H的其他顺序输出指令见表3-2,具体用法参见相关手册,本书不赘述。

表3-2 其他顺序输出指令功能表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。