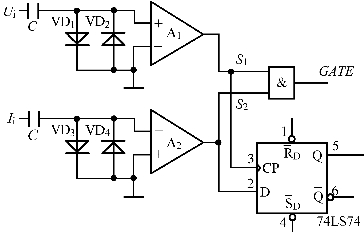

1)波形转换电路

时间间隔波形转换电路见图6.65。电压信号和电流信号分别接入两个比较器,其中电压信号由同相端输入,电流信号由反相端输入,两个比较器的输出为矩形脉冲S1和S2,由于比较器的灵敏度较好,矩形脉冲的上升沿仅仅决定于输入信号的过零点,两个脉冲经过与门处理即可合成待测信号GATE,GATE脉冲信号的宽度即为tp。波形转换图见图6.63所示。

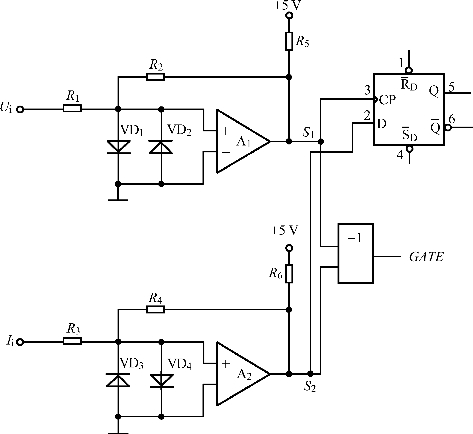

图6.65中触发器的作用是判断相位是超前还是滞后,当Q输出为低电平时呈感性,Q为高电平时呈容性。图6.65能完成相应的功能,但当被测信号在过零点有干扰时,就有可能出现多个脉冲。为了有效地解决干扰问题,过零比较器可以改为滞回比较器,改进后的电路如图6.66所示。用同相端作为输入端的目的是增加输入电阻,以满足设计题目的要求。R5、R6是上拉电阻。

图6.65 波形转换电路

图6.66 改进后的波形转换电路(https://www.daowen.com)

2)计时电路

单片机应用系统的时钟频率一般在6~12 MHz左右,执行一条指令至少需要一个机器周期,而完成任何一项工作,至少需要若干条指令,这就是说,单片机操作比数字逻辑电路(无论是组合电路还是时序电路)都慢得多。根据题目的精度要求,相位差绝对误差≤2°,最高频率为20 kHz,如果将异或门输出的方波直接送给单片机计时,由于单片机系统的速度较慢,执行单字节指令至少需要1 μs,无法达到精度的要求,所以可以经过数字逻辑电路计数后(当然最好能用CPLD/FPGA完成计数功能,但成本也相应提高了),再送给单片机处理。数字逻辑电路(TTL型)的最高工作时钟频率可以达到25 MHz,即周期为0.04 μs,这样精度可以得到保证。计数电路可以由普通计数器74LS191构成,用异或门输出的方波控制计数器计数,计数脉冲为高频信号(如20 MHz),用4个74LS191构成16位的计数器,计数值送入单片机处理。16位计数器的连线较简单,读者可自行画出。

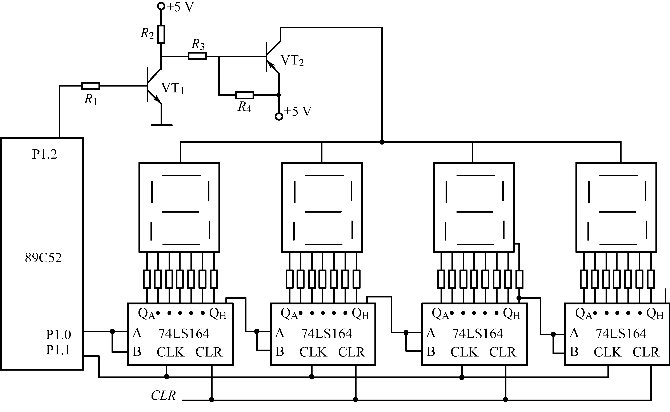

3)数据处理与显示电路

数据处理与显示电路如图6.67所示。该电路的作用是,把测得的时间间隔τ转换为相位差并且显示出来。相位差的转换用单片机来完成是很容易办到的。显示电路采用移位寄存器具有占用单片机的资源少的优点。

图6.67 数据处理与显示电路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。