用于PIE功能控制的寄存器包括PIE控制寄存器PIECRL、PIE应答寄存器PIEACK、INTx组使能寄存器PIEIERx(x=1~12)和INTx组标志寄存器PIEIFRx(x=1~12),见表2-28。注意:PIE配置和控制寄存器不受EALLOW保护,但PIE向量表受EALLOW保护。

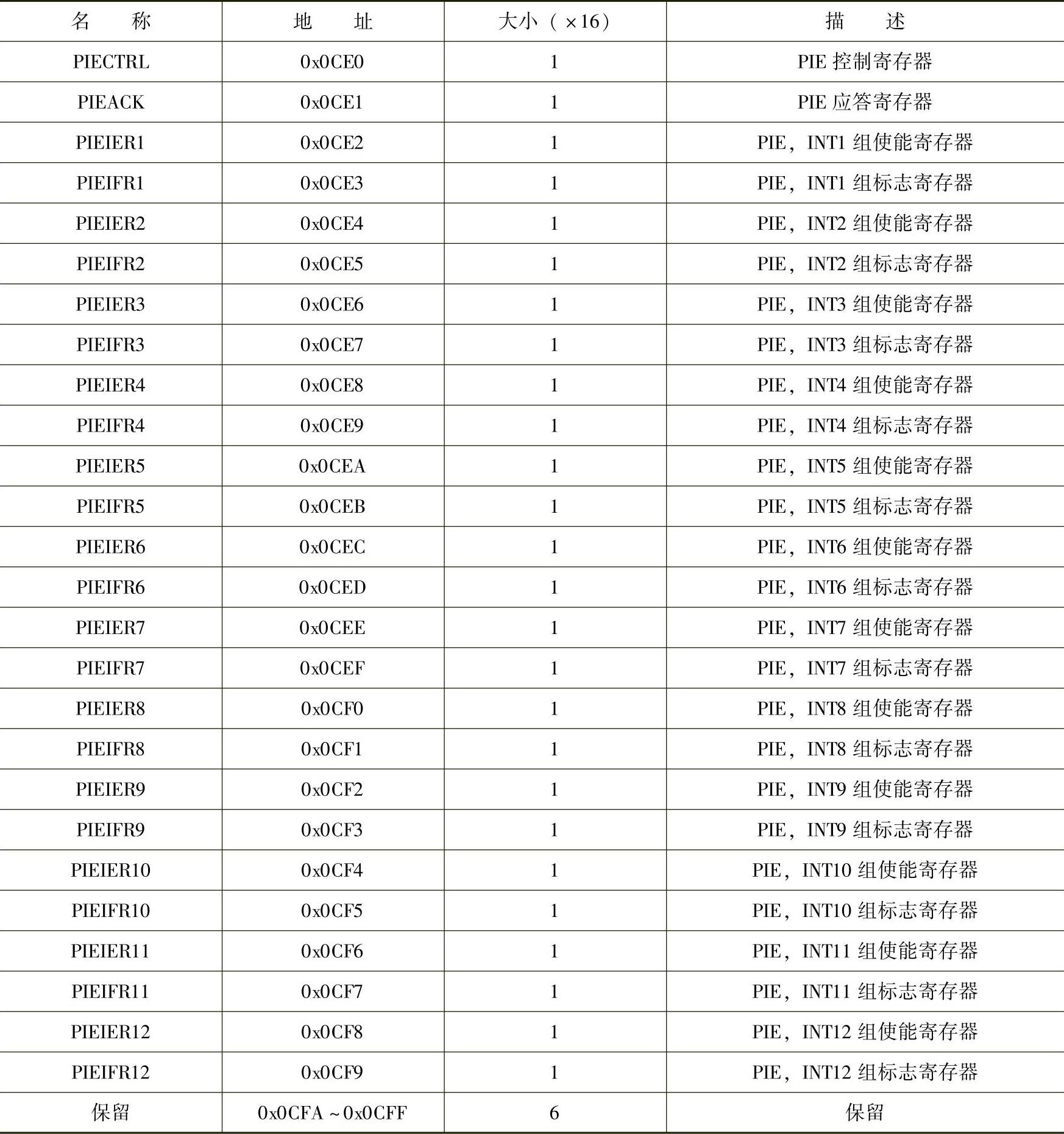

表2-28 PIE配置和控制寄存器

(1)PIE控制寄存器PIECRL

位15~1,PIEVECT:表示从向量表中取出的向量地址。这些位保留从PIE向量表中读取的中断向量地址。忽略了地址的最低有效位,只用到位15~1。用户可以读取该向量值,以确定是哪一个中断。例如,如果PIECTRL=0x0D27,则从地址0x0D26(非法操作中断入口)处读取回入口向量。

位0,ENPIE:使能向量获取位。当该位置1时,所有向量从PIE向量表中取;如果该位为0,禁止PIE,向量从Boot ROM中的CPU向量表中取。即使禁止PIE,所有的PIE寄存器(PIEACK、PIEIFR、PIEIER)都是可以访问的。

注:不会从PIE读取复位向量,即使PIE是使能的。复位向量总是从BootROM中读取。

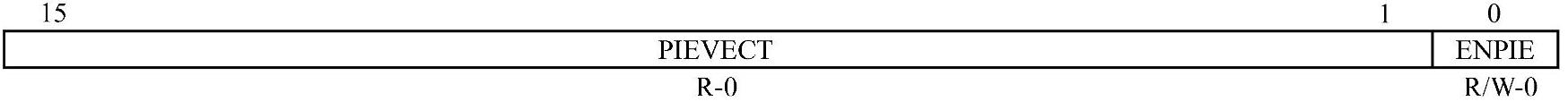

(2)PIE应答寄存器PIEACK

位15~12,保留位。

位11~0,PIEACK:写入1到对应的中断应答位可以清除该位,清除后当该组的中断申请到来时,允许PIE向CPU申请中断。读该寄存器可以查看各个中断组中是否有中断挂起。位0对应于INT1,……,位11对应于INT12。注:写入0无效。

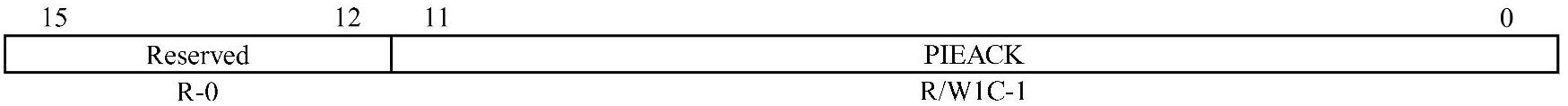

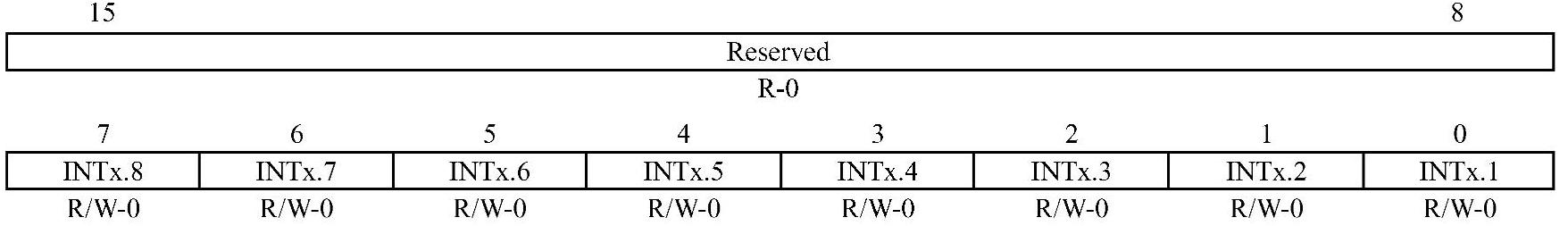

(3)PIE中断标志寄存器PIEIFRx(x=1~12)

CPU的每一个中断对应12个PIEIFR寄存器的一个。

位15~0,保留位。

位7~0,INTx.8~INTx.1:这些寄存器位表示当前是否有中断。它们的作用与CPU内核中断标志寄存器类似。当一个中断有效时,对应的寄存器位置1。当响应中断或向寄存器中的对应位写入0可以清零该位。读这些寄存器位也可以确定哪一个中断有效或挂起着。INTx对应于CPU的INT1~INT12。

注:1)上述所有寄存器的复位值在复位时被设置。

2)CPU访问PIEIFR寄存器时,有硬件优先级。

3)在读取中断向量时,硬件自动清零PIEIFR寄存器位。

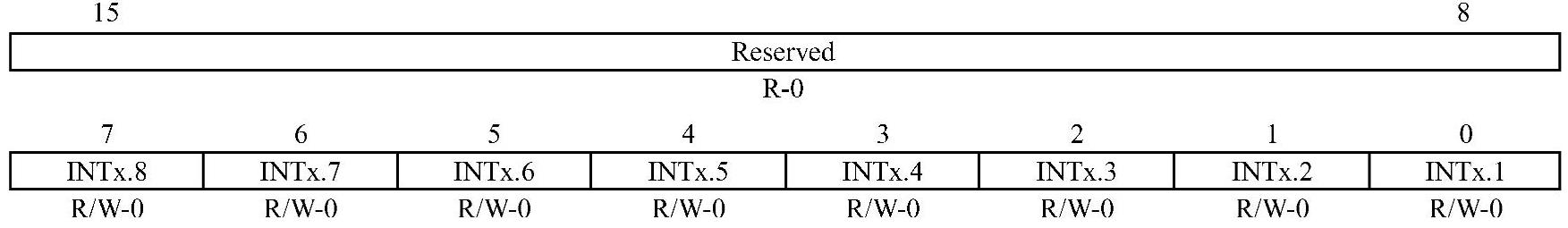

(4)PIE中断使能寄存器PIEIERx(x=1~12)

位15~0,保留位。

位7~0,INTx.8~INTx.1:这些寄存器位分别使能中断组中的一个中断,与CPU内核中断使能寄存器作用相似。写入1则对应的中断使能;写入0将禁止对应的中断。INTx对应于CPU的INT1~INT12。

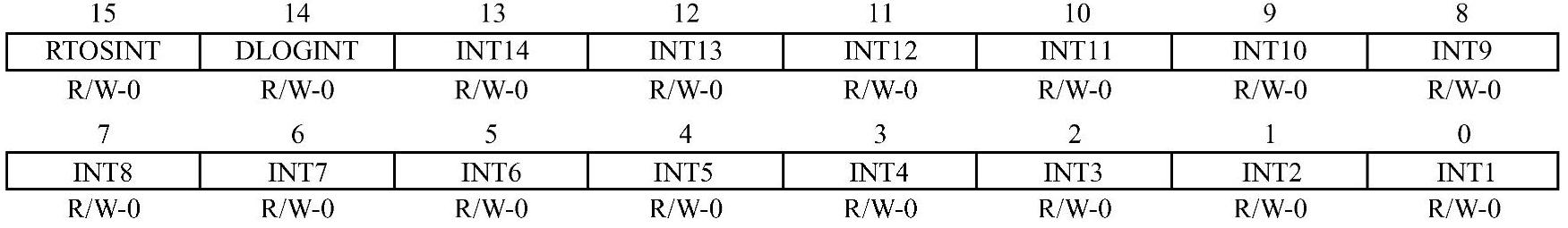

(5)CPU中断标志寄存器IFR

CPU中断标志寄存器(Interrupt Flag Register,IFR)是16位的CPU寄存器,地址为0006H,它用来识别和清除挂起的中断。IFR包含CPU级的所有可屏蔽中断(INT1~INT14,DLOGINT和RTOSINT)的标志位。当PIE使能时,PIE模块组合中断到INT1~INT12。

当请求一个可屏蔽中断时,对应的外设模块控制寄存器的标志位置1。如果对应的屏蔽位也为1,则向CPU发出中断请求,设置IFR中的相应标志。这表示中断正被挂起或等待应答。(https://www.daowen.com)

为了识别正挂起的中断,用PUSH IFR指令,然后测试堆栈值。用OR IFR指令可以置位IFR。用AND IFR指令用户程序可以清除挂起的中断。用指令AND IFR,#0或通过硬件复位可以清除所有正挂起的中断。

CPU应答中断或器件复位也可以清除IFR标志。

注:1)为了清除IFR位,必须向其写入0,而不是1。

2)当应答一个可屏蔽中断时,CPU自动清零IFR位。对应的外设模块控制寄存器中的标志位不清零。如果需要清零控制寄存器,则必须通过软件实现。

3)当中断是通过INTR指令请求且相应的IFR位置1时,CPU不会自动清零该位。如果需要清零IFR位,则必须通过软件实现。

4)IER和IFR寄存器适用于CPU内核级中断。所有外设模块在其各自的控制/配置寄存器中都有自己的中断屏蔽和标志位。

5)一个内核级中断对应一组外设中断。

CPU中断标志寄存器IFR的格式为

位15,RTOSINT:实时操作系统(RTOS)中断的标志。为0时,无RTOS中断挂起;为1时,至少有一个RTOS中断正在挂起。向其写入1将清零该位和清除中断请求。

位14,DLOGINT:数据记录中断的标志位。为0时,无DLOGINT中断挂起;为1时,至少有一个DLOGINT中断正在挂起。向其写入1将清零该位和清除中断请求。

位13~0,INT14~INT1中断的申请标志。某位为0时,该位无中断挂起;该位为1时,该位有中断挂起。向其写入1将清零该位和清除中断请求。

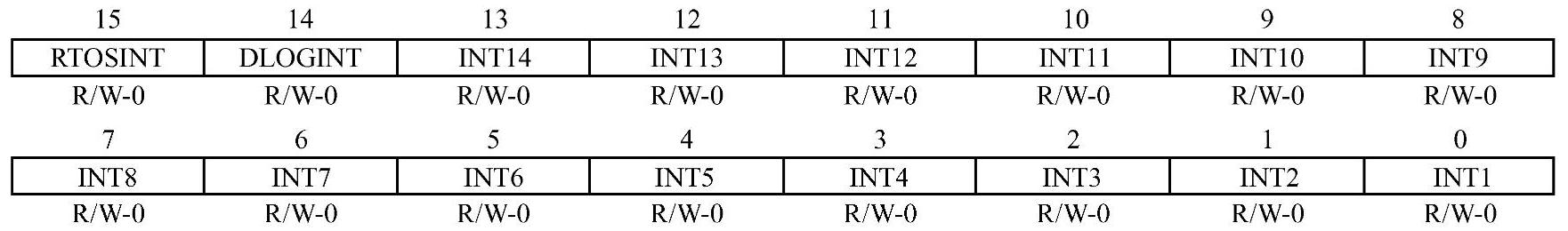

(6)CPU中断使能寄存器IER

IER(Interrupt Enable Register)是一个16位的CPU寄存器,地址为0004H。IER包含所有可屏蔽的CPU中断(INT1~INT14,RTOSINT和DLOGINT)的使能位。NMI(非屏蔽中断)和XRS(复位中断)都不包括在IER中,因此IER对它们无效。用户可以读IER去识别已使能或禁止的中断,也可以写IER来使能或禁止中断。为了使能一个中断,可以用ORIER指令把对应的IER位置1。为了禁止一个中断,可以用ANDIER指令把对应的IER位清零。当禁止一个中断时,不论INTM位的值是什么,都不响应它。当使能一个中断时,如果对应的IFR位为1和INTM位为0,则中断会得到应答。

当使用OR IER和AND IER指令修改IER位时,要确定不修改位15(RTOSINT)的状态,除非当前是处于实时操作系统模式。

当执行一个硬件中断或执行INTR指令时,会自动清零对应的IER位。当响应TRAP指令发出的中断请求时,IER位不会自动清零。在TRAP指令产生中断的情况中,如果对应的IER位需要清零,则必须在中断服务程序中由用户程序完成。

复位时,IER=0,禁止所有可屏蔽的CPU级中断。

CPU中断使能寄存器IER的格式为

位15,RTOSINT:实时操作系统(RTOS)中断使能位。该位可以使能或禁止CPU RTOS中断。设置为0时,禁止RTOS中断;为1时,使能RTOS中断。

位14,DLOGINT:数据记录中断的使能位。该位可以使能或禁止CPU数据记录中断。设置为0时,禁止DLOGINT中断;为1时,使能该中断。

位13~0,INT14~INT1中断的使能位。可以使能或禁止相应的中断。某位设置为0时,禁止对应的中断;为1时,使能该中断。

(7)CPU中断仿真使能寄存器DBGIER

仿真中断使能寄存器DBGIER(Debug Interrupt Enable Register)只有在CPU处于实时仿真模式中停止时才有效。在DBGIER中使能的中断被定义为时间敏感(Time-critical)中断。在实时模式下,当CPU停止时,只有在IER中使能的时间敏感中断才进入仿真服务程序。如果CPU运行在实时仿真模式,则使用标准的中断处理过程,而忽略DBGIER。

DBGIER的16个位代表的中断与IER一样。用户也可以通过读DBGIER去识别中断是否使能或禁止,或写DBGIER以使能或禁止中断。对对应的位置1,则使能中断;对对应的位置0,则禁止中断。用PUSH DBGIER指令可以读取DBGIER的值,POP DBGIER指令可以向DBGIER寄存器写数据。复位时,所有DBGIER位都为0。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。