1.组合逻辑设计的基本情况

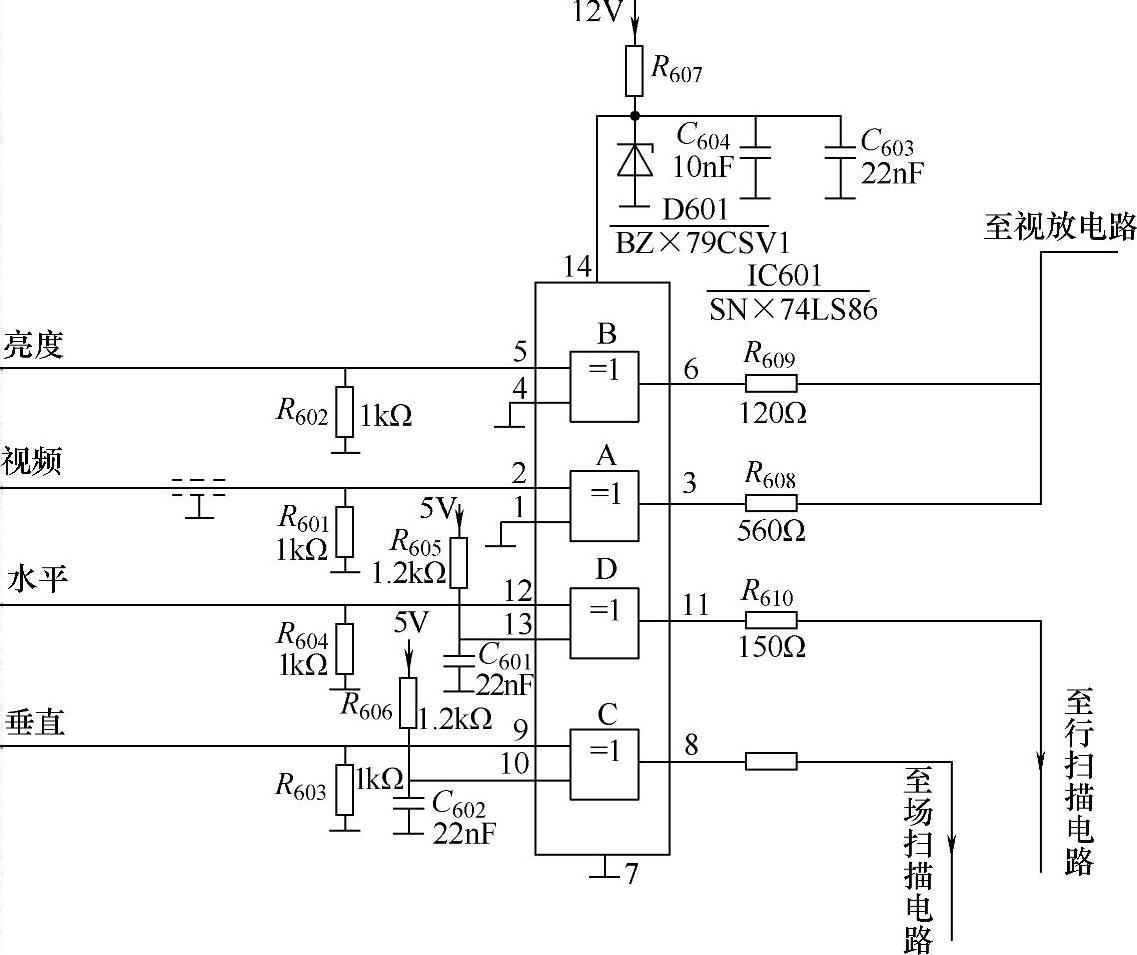

图4-74 7486典型应用实例

实用数字逻辑电路设计是利用基本逻辑运算去实现生活、工作、娱乐所需要的各种具有数字逻辑特点的实际功能,只要能够确定电路输入信号、输出信号的数量及其状态间的对应关系,就能构造出具有相应功能的数字逻辑电路。

在数字集成电路系列中,有多种组合逻辑电路的定型产品可直接选用,如加法器、比较器、编码器、译码器、数据选择器、分配器等(见附录C)。

需要制作者设计的多是成品电路之间实现信号匹配的辅助电路。这类组合电路的结构都比较简单,首先是按命题所述条件(输入信号)与结果(输出信号)之间的全部逻辑对应关系得出最简逻辑表达式,再按选用的逻辑门种类变换表达式,画出逻辑电路图,最后按图制作实际电路。

2.成品组合逻辑电路的设计

了解成品组合逻辑电路核心结构的设计过程,有助于提高实际设计能力和丰富设计思路。

(1)一位全加器的逻辑设计

能够对数值进行加法运算的电路称为加法器。一位加法器是能计算一位二进制数加法的简单电路,多位加法器用一位加法器组合而成。不考虑低位进位的叫半加器,半加器只用在多位加法器的最低位。考虑低位进位的叫全加器,具有通用性。

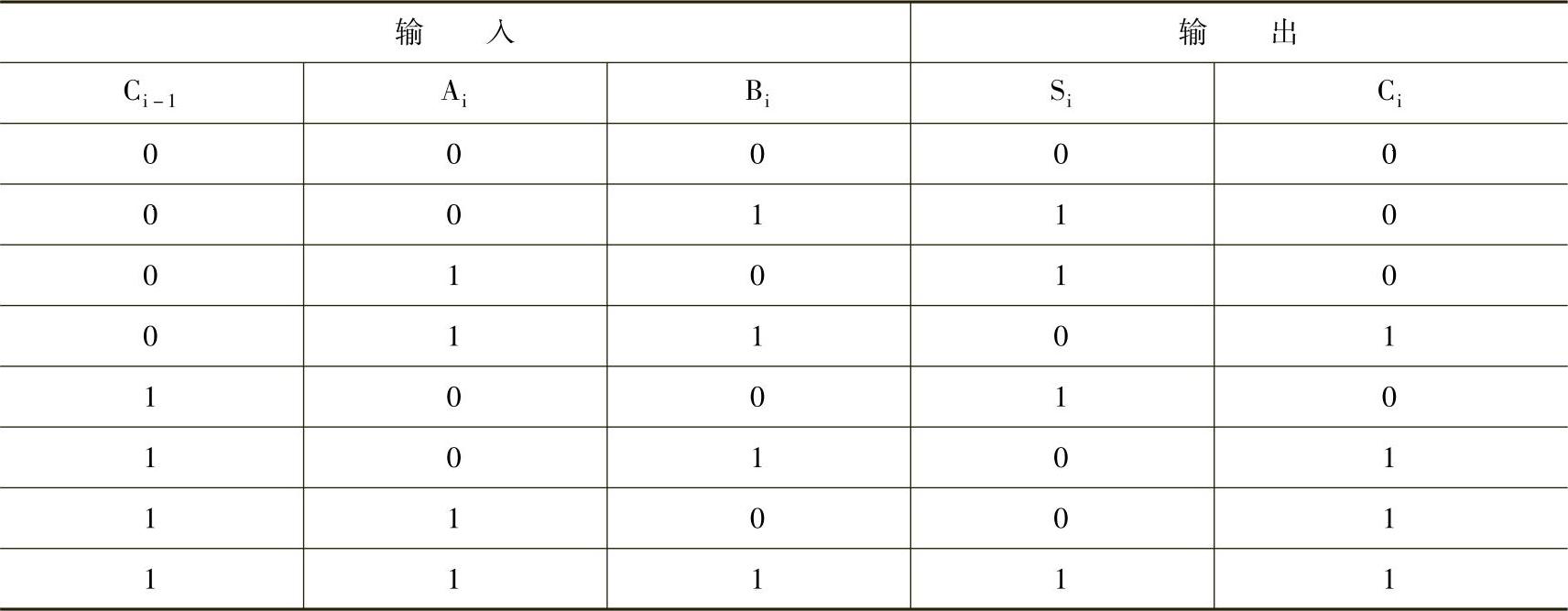

一个一位全加器有两个输出信号:Si为本位和;Ci为向高位的进位,3个共同的输入信号:设Ai、Bi为本位加数;Ci-1为低位进位。它们之间的逻辑关系列成真值表见表4-29。

表4-29 一位全加器真值表

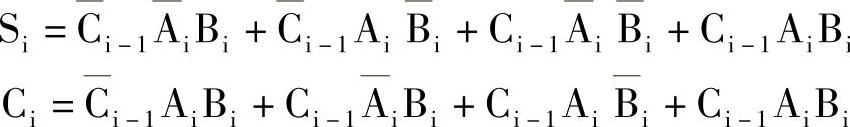

根据真值表写出两个函数的表达式:

Si函数显然不能化简(可填入卡诺图检验),但符合异或逻辑关系,可简化为异或表达式:

Ci函数式部分能化简,另一部分也是异或逻辑:

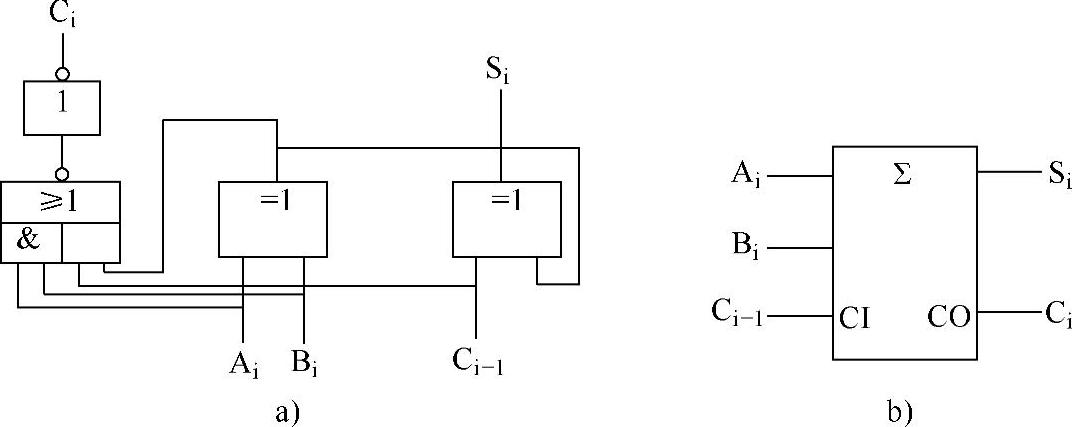

两个电路输入信号是共同的,并都包含(Ai⊕Bi),为了充分利用成品门电路而简化电路结构,选用两个异或门、一个与或非门和一个非门组成电路。图4-75所示为全加器电路。

图4-75 全加器电路

这个全加器的输入、输出信号都是高电平有效,没有需用负逻辑符号的部位。

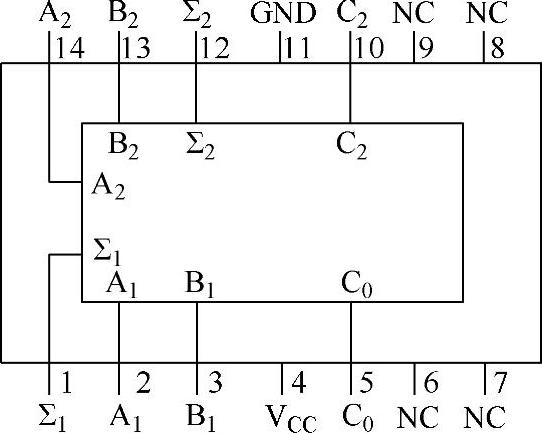

7482是TTL系列的两位二进制全加器,电路的引脚功能如图4-76所示。

图中A2、A1和B2、B1为两个两位二进制数输入,C0为低位进位输入,∑1与∑2为两位本位和输出,C2为高位进位输出,NC为空引脚。

(2)比较器的逻辑设计

数据比较是一种常用的数据处理形式,电路由相等、大、小3种比较电路复合构成。

两个一位二进制数的比较称为一位比较器,它是多位比较器的基本单元。

1)一位同比较器设计。

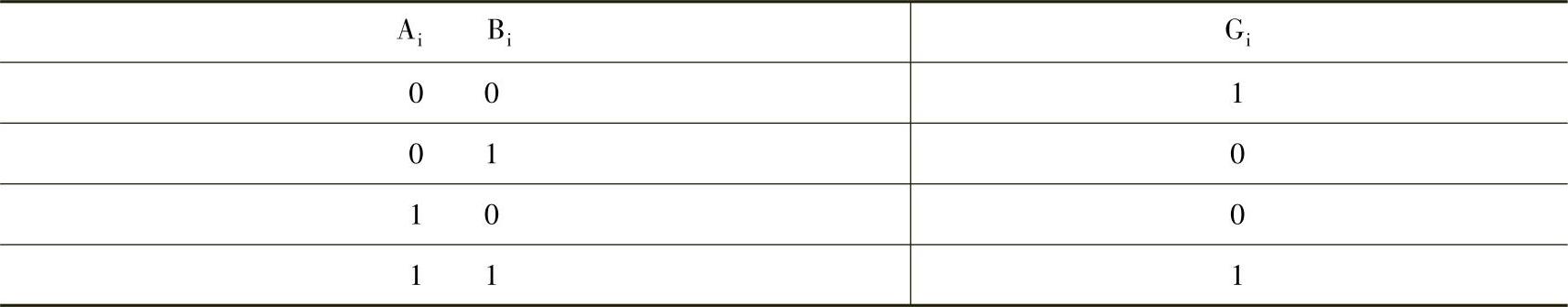

设:被比较的两个数为A i与B i,比较结果为Gi。依据同比较器的功能,列出一位同比较器的逻辑真值表(见表4-30)。

图4-76 7482的电路结构和引脚功能

表4-30 一位同比较器真值表

写出一位同比较器的逻辑函数表达式为

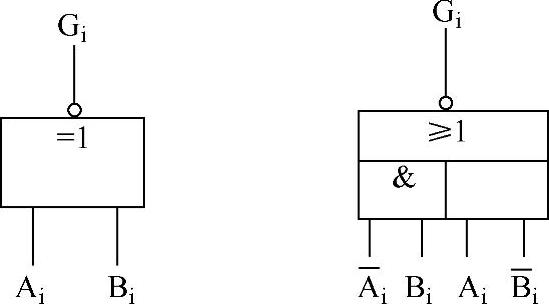

一位同比较器的逻辑电路实际就是个异或非门,可直接用74266(二输入四异或非门),也可用与或非门构成。不同结构的一位同比较器如图4-77所示。

图4-77 一位同比较器电路

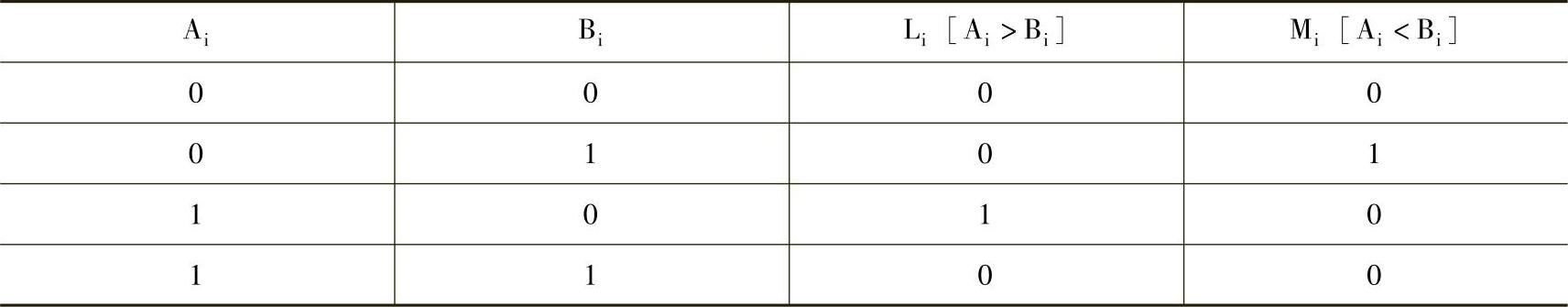

2)一位大小比较器设计。

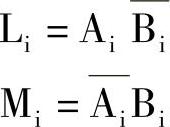

设:被比较的两个一位二进制数Ai与Bi;两个输出信号,Mi表示Ai<Bi,Li表示Ai>Bi。由比较器应具备的功能可列出一位大小比较真值表(见表4-31)。

表4-31 一位大小比较真值表

由真值表得两个输出信号的函数表达式为

一位大小比较器的电路如图4-78所示。

图4-78 一位大小比较器电路

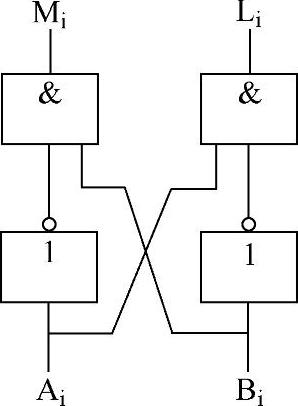

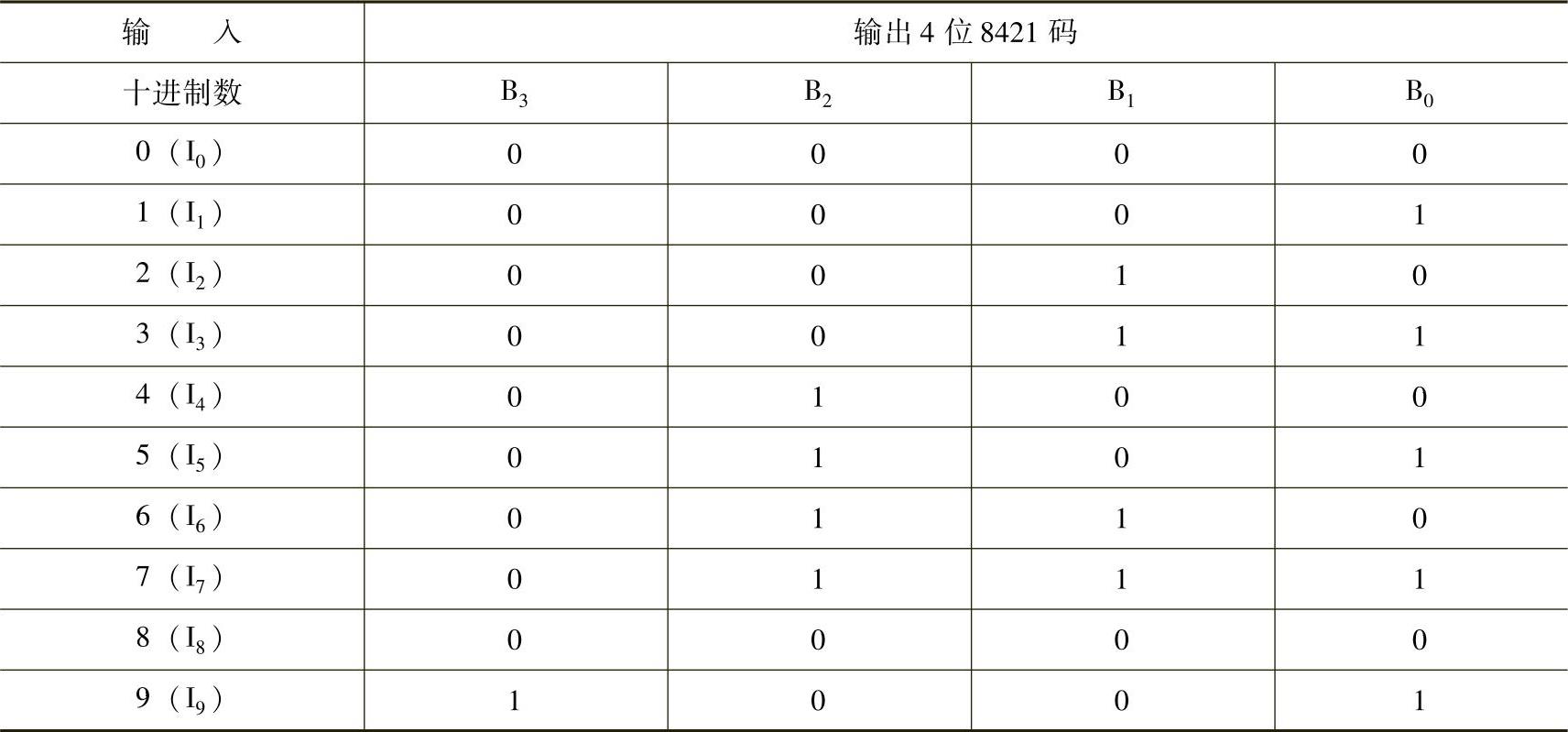

多位比较器有串行和并行两种输入方式,并行输入结构简单。7485为TTL系列产品中的四位数值比较器,该电路的内部结构与引脚功能如图4-79所示。

图4-79 7485的内部结构与引脚功能

7485可执行四位二进制码(或一位8421 BCD码)的数值比较,A3、A2、A1、A0和B3、B2、B1、B0为两个四位二进制数并行输入端;有FA>B(大于)、FA=B(等于)和FA<B(小于)3种比较结果输出。

电路还为级连成更长字的比较器备有级连信号输入端,A>B、A=B和A<B为3个级连输入,级连时把3个引脚与低四位比较电路的输出对应连接,并把最低级的A=B端加高电平即可。

(3)编码器的逻辑设计

任何信息送入数字系统处理都要先转换为与二进制码相对应的电信号,能实现这种功能的电路称为编码器。把离散信号转换为二进制码时,首先要依据离散信号的个数N确定二进制码的位数n,其关系为:2n-1<N≤2n。

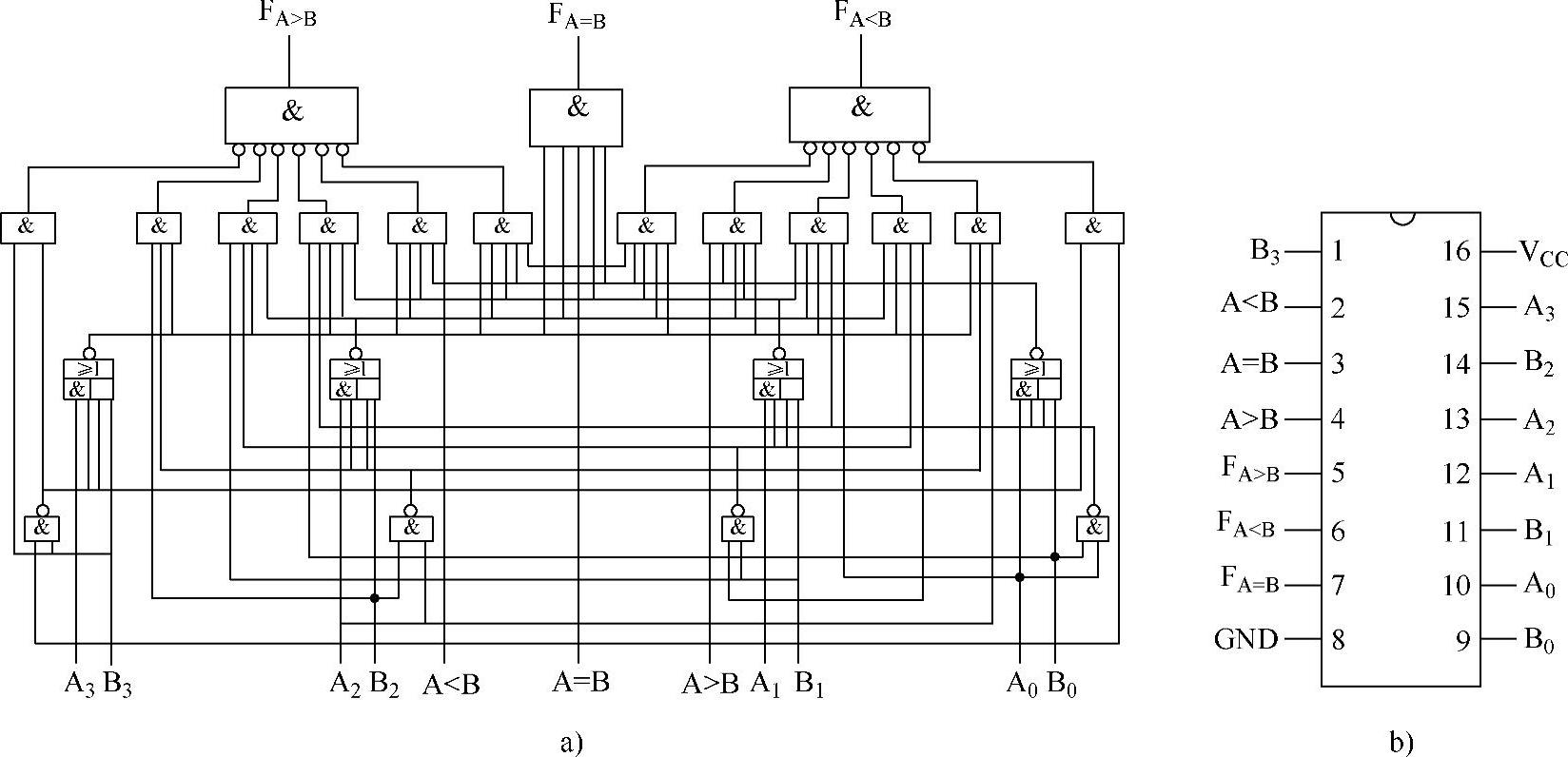

用二进制码表示十进制数称作BCD码。0~910个数字需用4位二进制码才能满足表示方法需要,4位二进制数有16种不同组合状态,表示0~910个数字只用10个组合,而且编码对原信息只是一种表示关系,没有量值关系约束,在4位二进制数的16种组合状态中任选10组就可以实现对十进制数的编码。因此,十进制数的BCD码有多种形式。能将10个数字转换8421权码的电路称为8421编码器。8421码是有权码,4位二进制码从高位至低位,每位的位权值分别为23、22、21、20,即8、4、2、1。用8421码表示十进制的0~9数是最常用的方式。

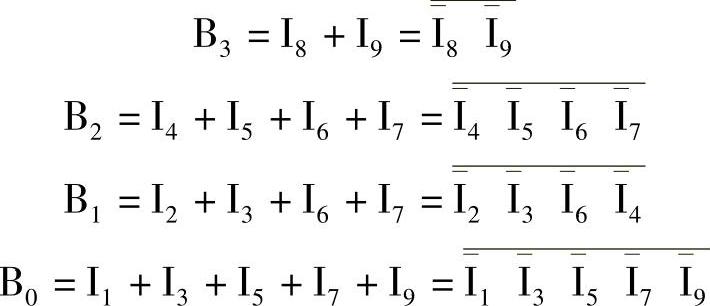

表4-32为8421BCD编码真值表,其中I0、I1、I2、I3、I4、I5、I6、I7、I8、I9分别为0~910个数字输入端,B3、B2、B1、B0为4位编码输出端。

表4-32 8421BCD编码真值表(https://www.daowen.com)

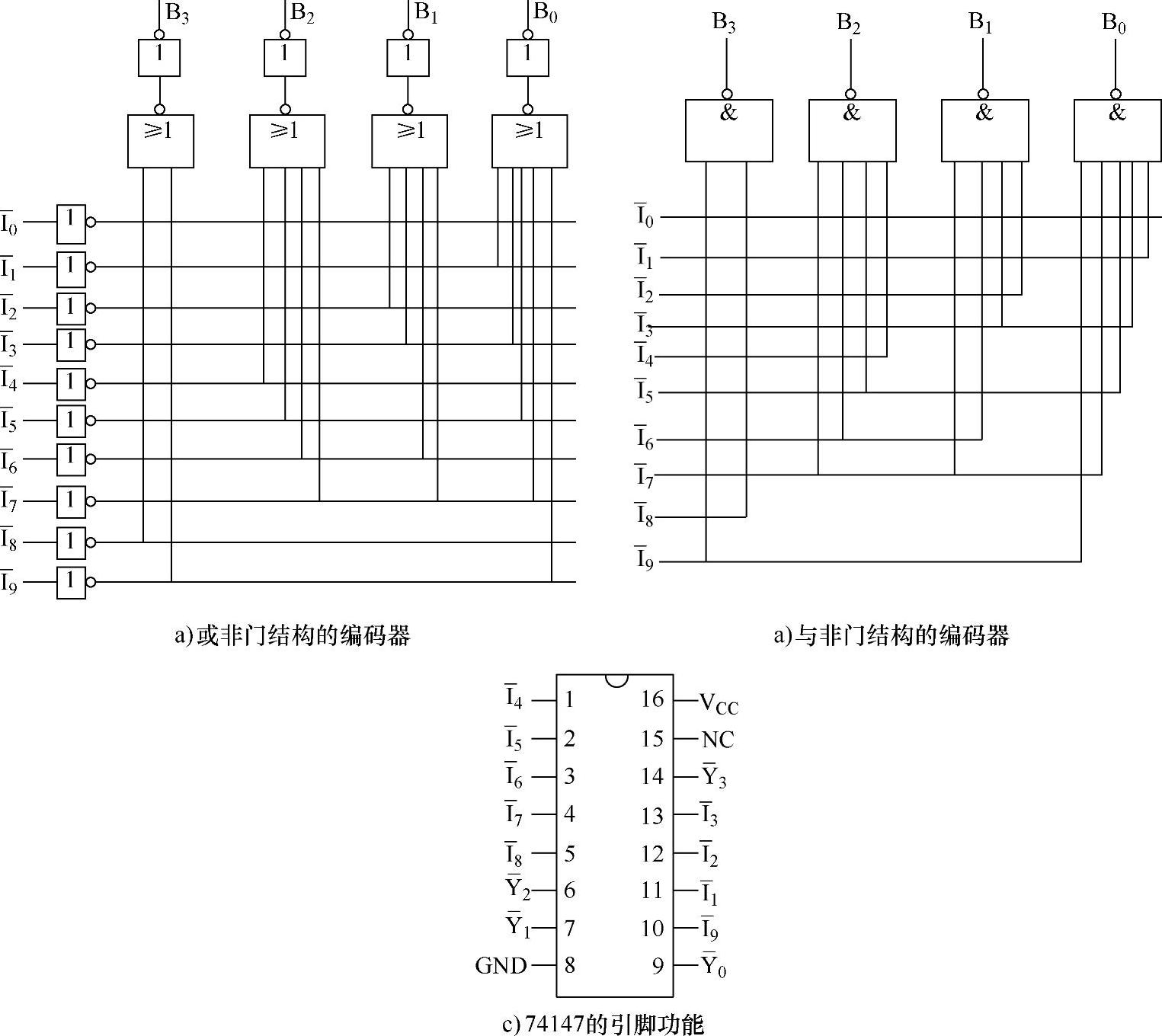

编码器的表达式:

编码器电路可用或非门组成,也可用与非门组成。TTL系列中的实际产品74147为功能较高的10线-4线优先编码器,如图4-80所示。对10线编码,实际只需输入9个信号: 、

、 、

、 、

、 、

、 、

、 、

、 、

、 、

、 ,均为低电平有效。

,均为低电平有效。 、

、 、

、 、

、 为4位编码输出,也是低电平有效。

为4位编码输出,也是低电平有效。

(4)译码器的逻辑设计

把二进制码按编码时所赋予的含意进行还原的过程称为译码,能实现译码的电路称为译码器。译码是编码的逆过程。数字系统常用的译码器有二进制译码器、二—十进制译码器、数码显示译码器等。

图4-80 8421BCD码编码器电路

1)二进制译码器设计。按二进制数大小把二进制码译成有序的对应状态输出的电路称为二进制译码器。二进制译码器是各类译码器的基本电路。

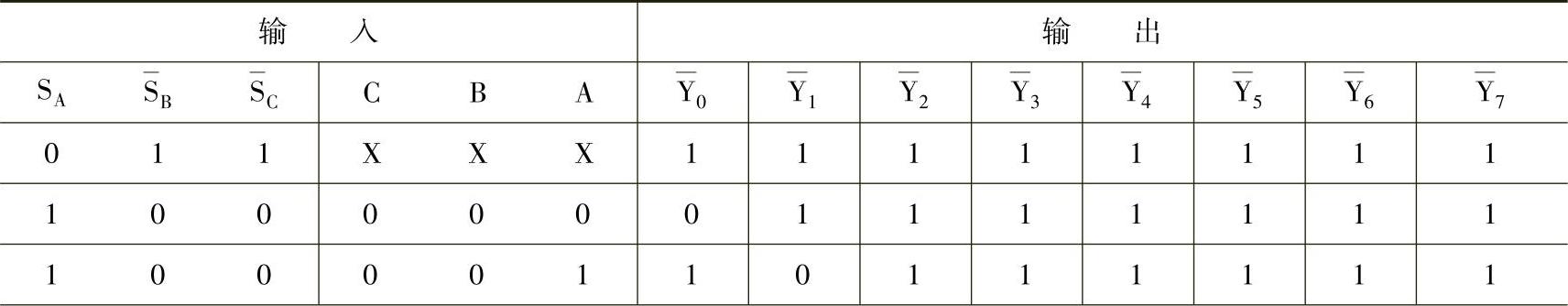

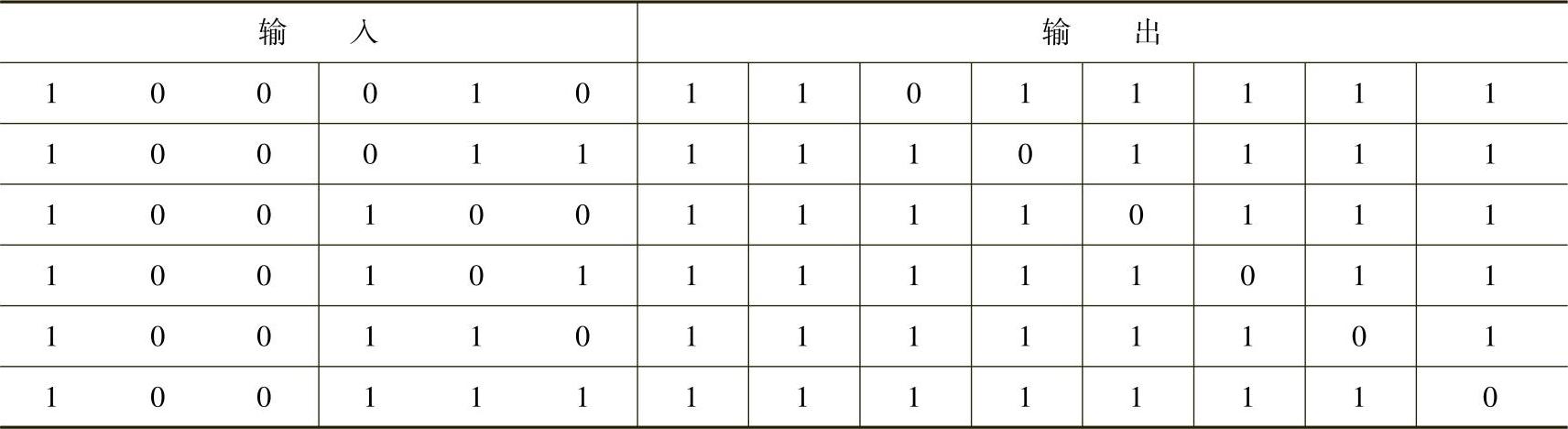

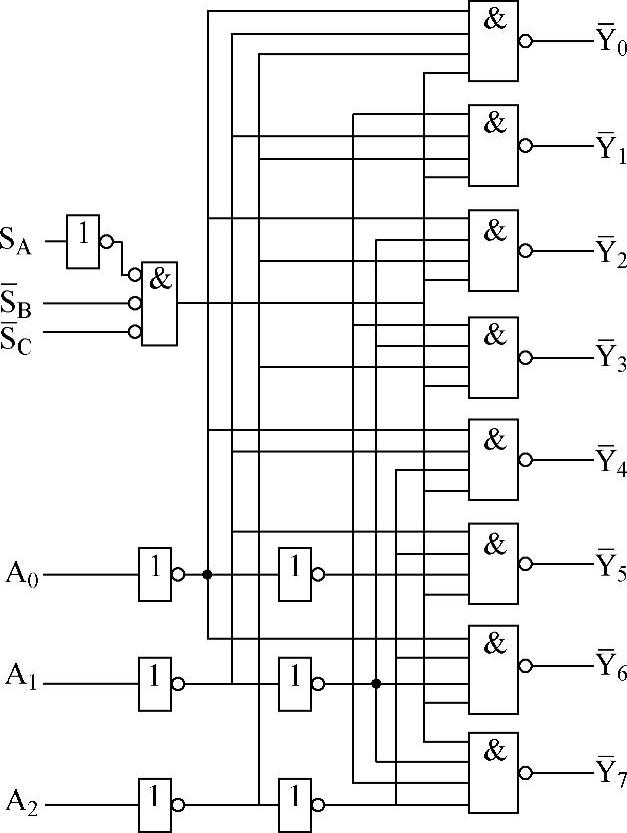

TTL系列的成品集成电路74138就是计算机电路常用的地址译码器。该电路共6个输入信号,其中SA、 、

、 3个是使能控制信号,有一个处于无效状态,译码器输出则全部为无效状态;A2、A1、A0为3个译码输入信号。

3个是使能控制信号,有一个处于无效状态,译码器输出则全部为无效状态;A2、A1、A0为3个译码输入信号。 ~

~ 是8个低电平有效的译码输出信号。当SA为高电平,

是8个低电平有效的译码输出信号。当SA为高电平, 与

与 为低电平时,电路为使能状态,其逻辑真值表见表4-33,为便于表述,用C、B、A代替A2,A1,A0。

为低电平时,电路为使能状态,其逻辑真值表见表4-33,为便于表述,用C、B、A代替A2,A1,A0。

表4-33 74138真值表

(续)

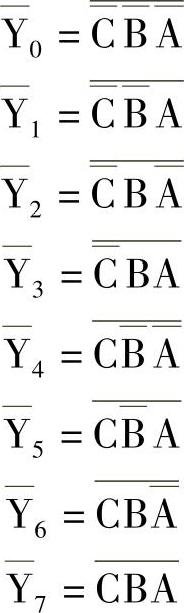

依据真值表可写出在使能状态下每个输出信号的逻辑表达式:

3线—8线译码器(74138的核心电路)如图4-81所示。

图4-81 3线—8线译码器

74138引脚功能如图4-82所示。

译码器的输入信号的一个组合状态对应一个输出端有效,所以也被叫做线路选择器或数据选择器。

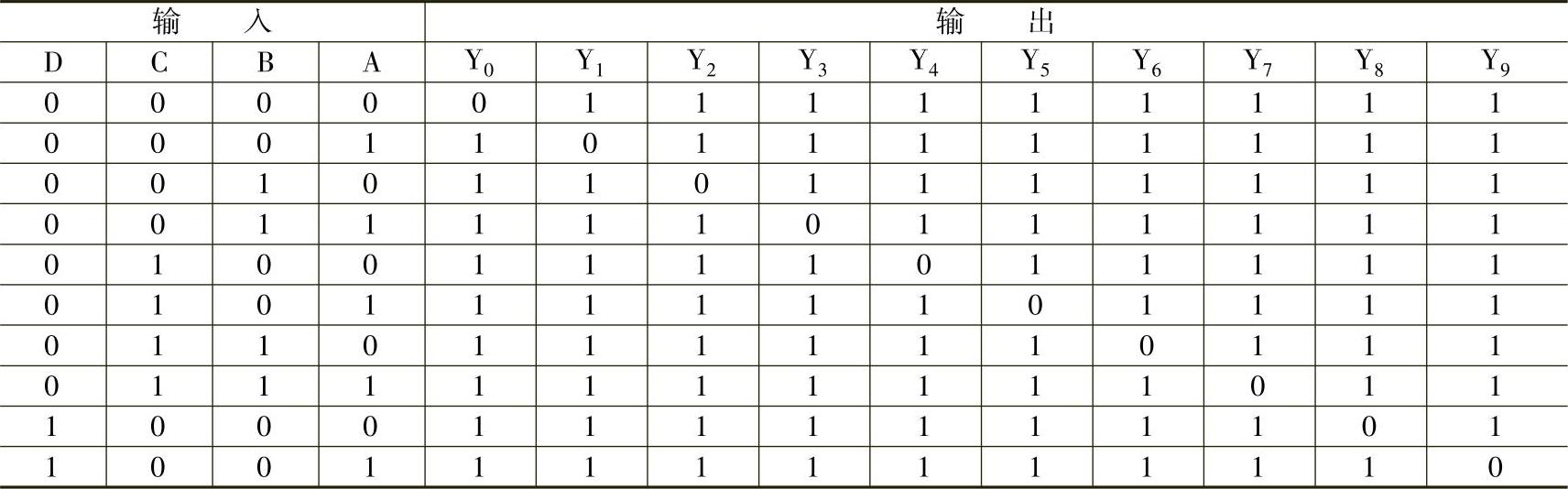

2)二—十进制译码器。将二—十进制码译成10个十进制数的电路称为二—十进制译码器。译码器的输入信号为4位二进制码,输出是与十进制10个数字相对应的独立信号。表4-34为8421BCD译码器真值表。

图4-82 74138的引脚功能

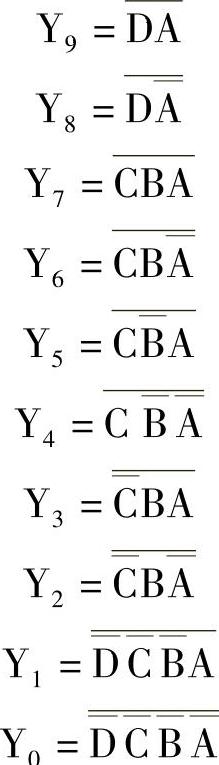

表4-34 8421BCD译码器真值表

用卡诺图对10个输出函数进行化简,如图4-83所示。

图4-83 Y0~Y9的化简

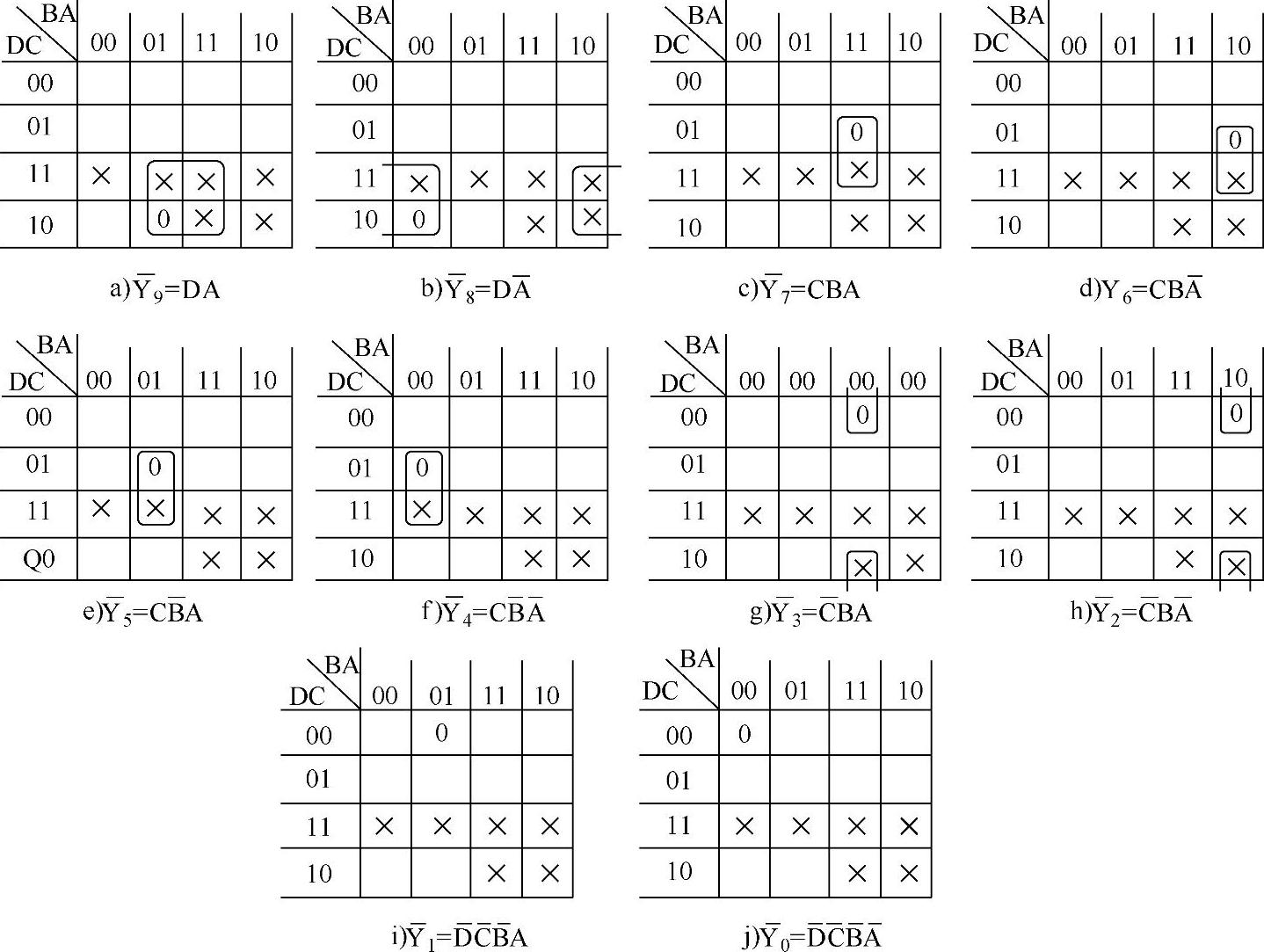

再把化简结果转换为与非式:

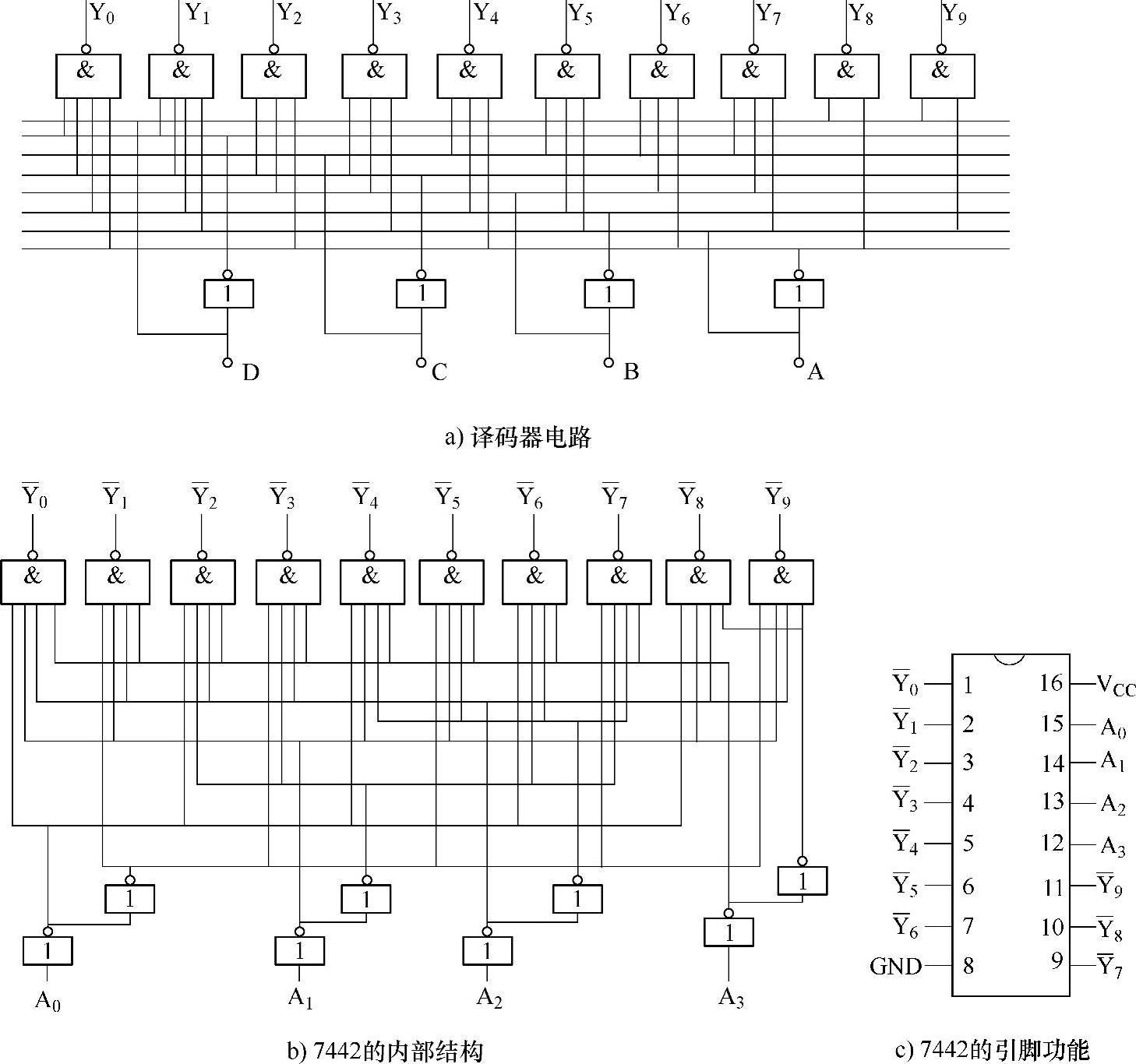

按以上10个表达式,绘出译码电路,如图4-84所示。

图4-84 二—十进制译码器

TTL系列的7442是8421BCD码的译码器,有10个独立输出端,对应十进制的10个数。输入4位8421BCD码,输出1位十进制数,也叫4线—10线译码器。

【边学边练】

1)取一片7442集成电路插在数字实验板上,并在旁边搭接4组输入逻辑。

2)接通地线和5V电源。

3)在7442的A3、A2、Al、A04个引脚,按4位二进制数0000~1111分16组输入,并检测各输出端的信号电平。

3)数码显示译码器。能直接驱动数码显示器的译码电路称为数码显示译码器。数码显示器有半导体发光二极管(LED)、荧光管、液晶数码显示屏等多种类型,显示译码器要与显示器类型对应,并有较大输出功率的驱动功能。

LED数码管的结构如图2-52所示。

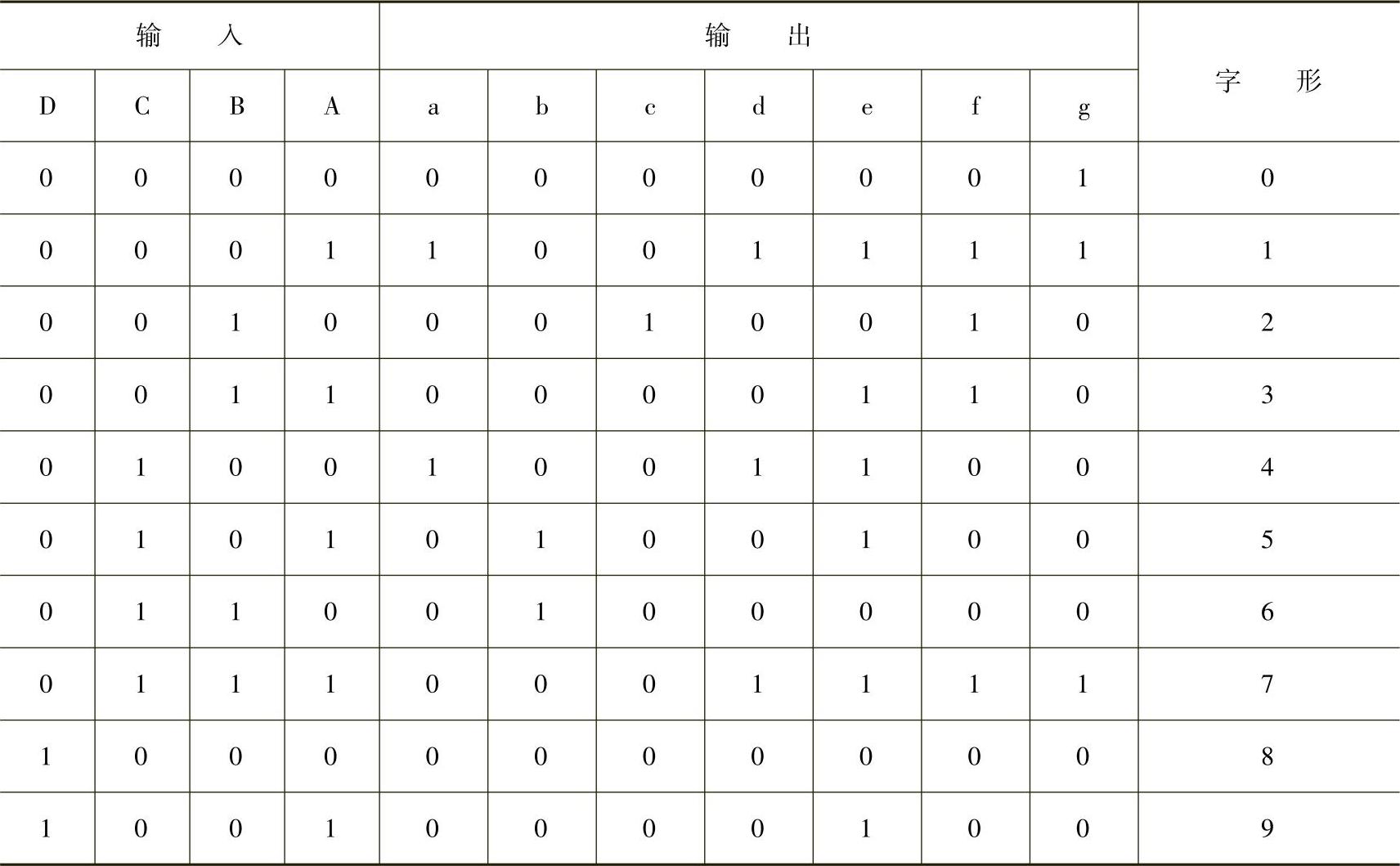

显示驱动电路对共阳极数码管输出低电平时笔画段LED点亮,组成对应数码字形。表4-35为共阳极数码管的显示译码器真值表。

表4-35 共阳极数码管的显示译码器真值表

若是驱动共阴极数码管,显示电路需输出高电平点亮LED笔画段,将表4-35中输出信号的0、1互换,就成为共阴极数码管的显示译码器真值表。

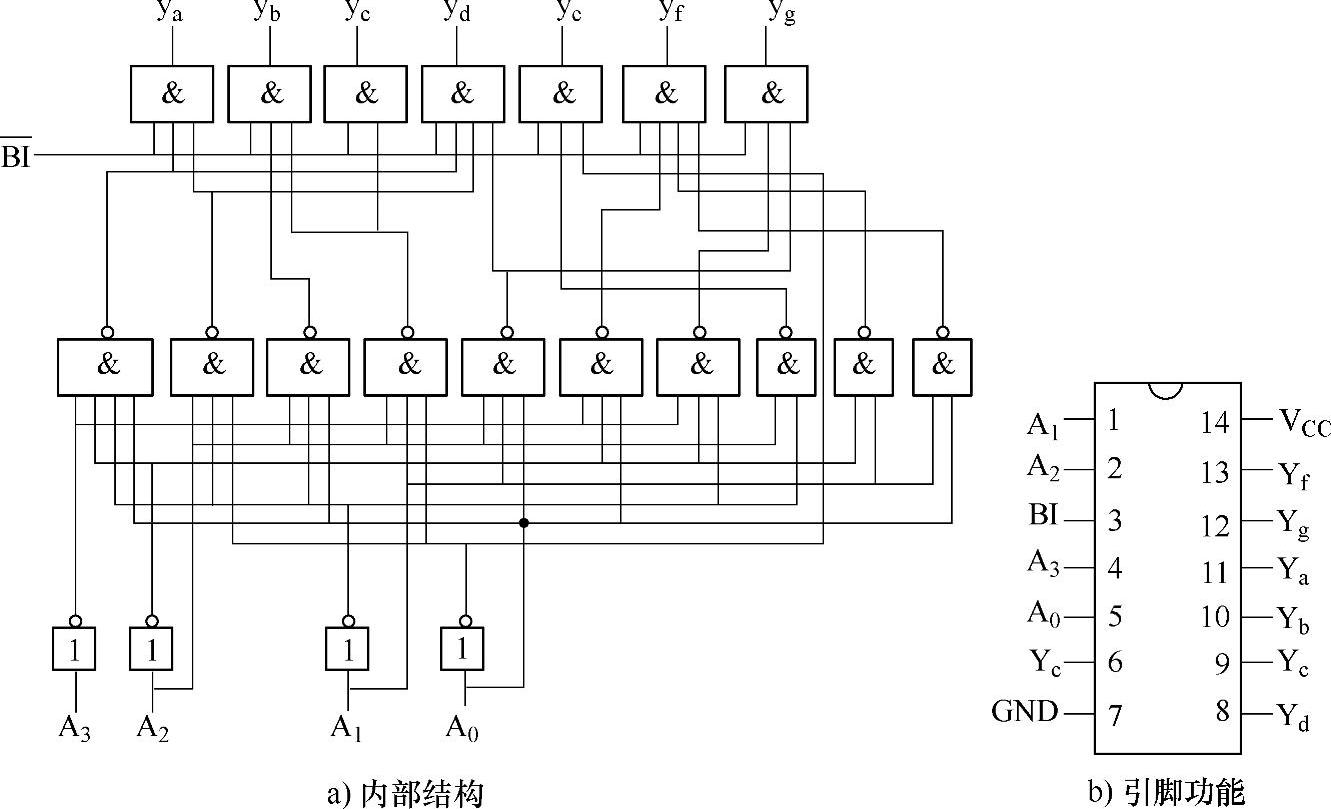

TTL系列的7449(4线—7段译码器/驱动器)是与共阴极LED数码管配合使用的显示驱动电路,其内部电路和引脚功能如图4-85所示。

图4-85 7449的内部电路和引脚功能

A3、A2、A1、A0为译码器输入端,Ya、Yb、Yc、Yd、Ye、Yf、Yg为驱动共阴极LED数码管输出端,BI为灭灯信号输入。

【边学边练】

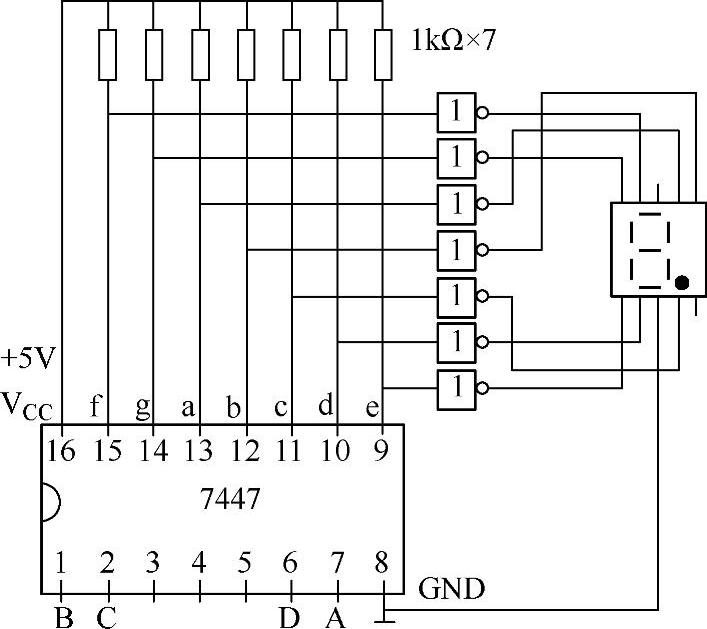

1)准备7447(7段显示译码器)1片、7404(六非门)2片、lkΩ(1/8W或1/16W)电阻7只,半导体发光数码管(共阴极)1只。

2)按图4-86所示在数字实验板上搭接电路,并在适合位置安排4组输入逻辑。

图4-86 显示码译码器电路实验接线

3)给电路接通地线和5V电源。

4)在7447的⑥、②、①、⑦4个引脚,按4位二进制数0000~1001分10组输入,观看数码管显示的字形。

5)用直接接地的方式,分别给③、④、⑤接入低电平,观察数码管的变化。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。