数字集成电路定型产品中没有的时序电路需要制作者自己设计,用成品电路加辅助电路进行功能转换和用触发器以及逻辑门按所需功能连接是常用的两种设计方法。

1.用成品时序电路改制

选用与所需功能相关的成品时序电路,配加适当的辅助电路就可以方便地实现设计目的。

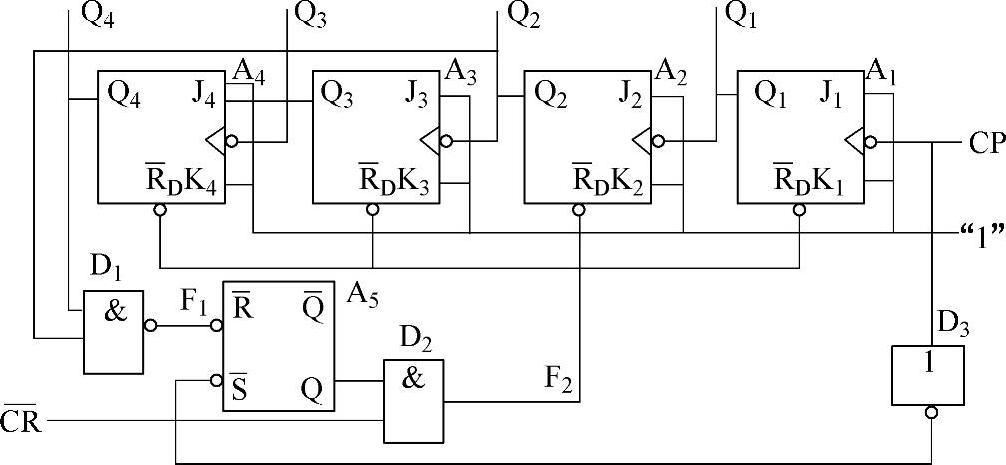

图4-130 复位式8421码十进制计数器电路

(1)任意进制计数器

利用二进制计数器改制任意进制计数器是简单、有效的方法,改制原理是把进位信号引回计数电路,用其控制计数器跳回到计数的初始态,称作脉冲反馈法。

制作初始态为0的计数器,可将进位信号引回到触发器的异步置0端强制电路复位,称为强制复位法。图4-130所示为4位二进制计数器改作十进制加法计数器的逻辑图。电路中增设一个锁存器用以清除复位时的尖峰脉冲。

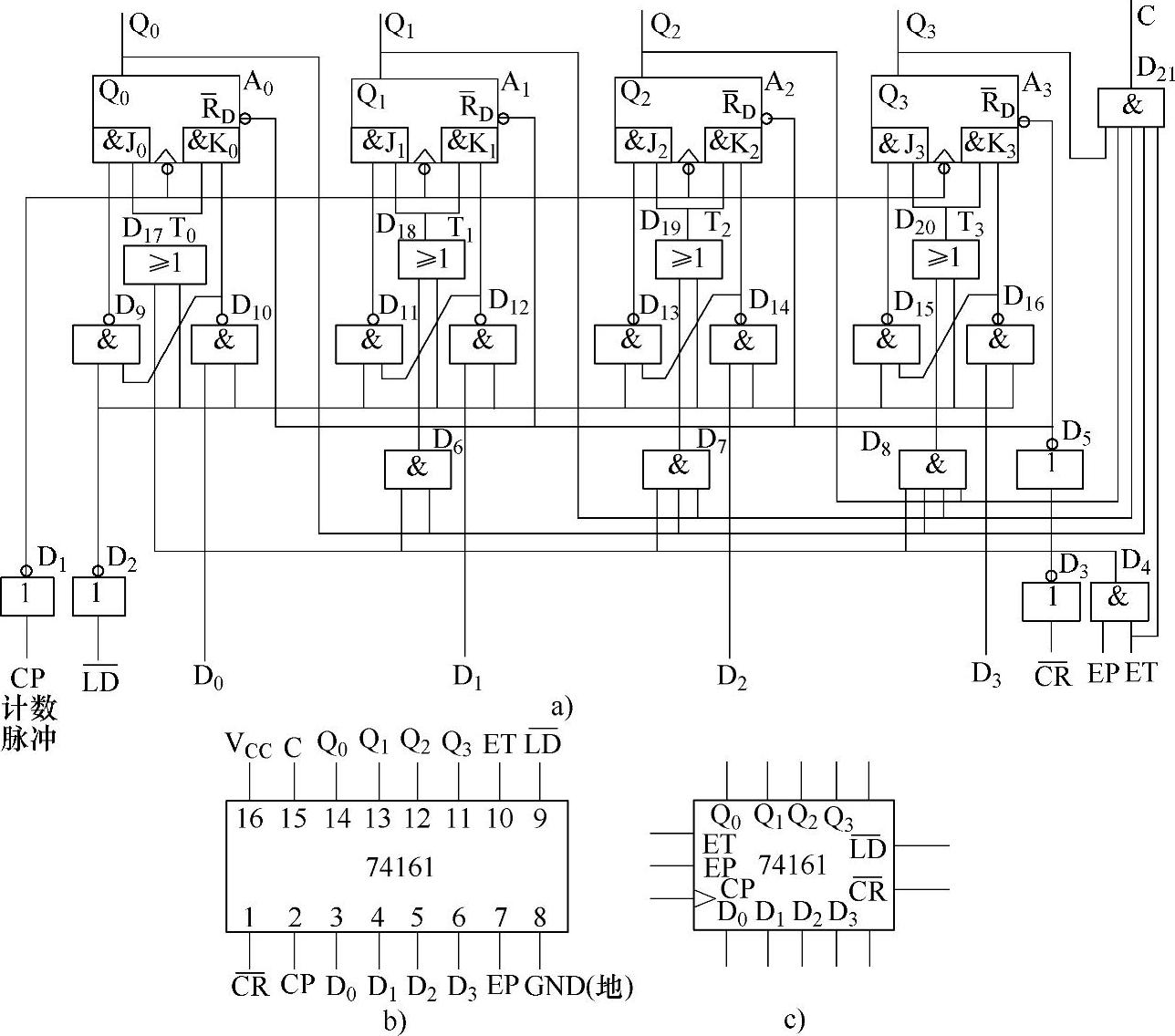

实际应用中,对计数器输出的状态序列常不以0为初态(起始值),这时可用预置法改制,为此许多计数器的定型产品设有预置输入端和预置控制信号。TTL系列的74161为4位同步二进制可预置计数器,其内部结构和引脚功能如图4-131所示,表4-53为74161的逻辑功能表。

图4-131 74161的内部结构和引脚功能

表4-53 74161逻辑功能表

Q3、Q2、Q1、Q0为计数状态输出端,C是进位输出端, 为置数控制信号,低电平置数、高电平计数,D3、D2、D1、D0为预置数据的输入端。

为置数控制信号,低电平置数、高电平计数,D3、D2、D1、D0为预置数据的输入端。 为低电平有效的异步清零端,EP与ET为触发器输入电路工作状态控制信号,其中ET兼作进位信号C的输出控制。

为低电平有效的异步清零端,EP与ET为触发器输入电路工作状态控制信号,其中ET兼作进位信号C的输出控制。

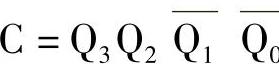

74161的进位逻辑设定为C=Q3Q2Q1Q0,当改变计数进制时必须用设置不同的初始实现。若需改变进位逻辑则应另加进位电路。

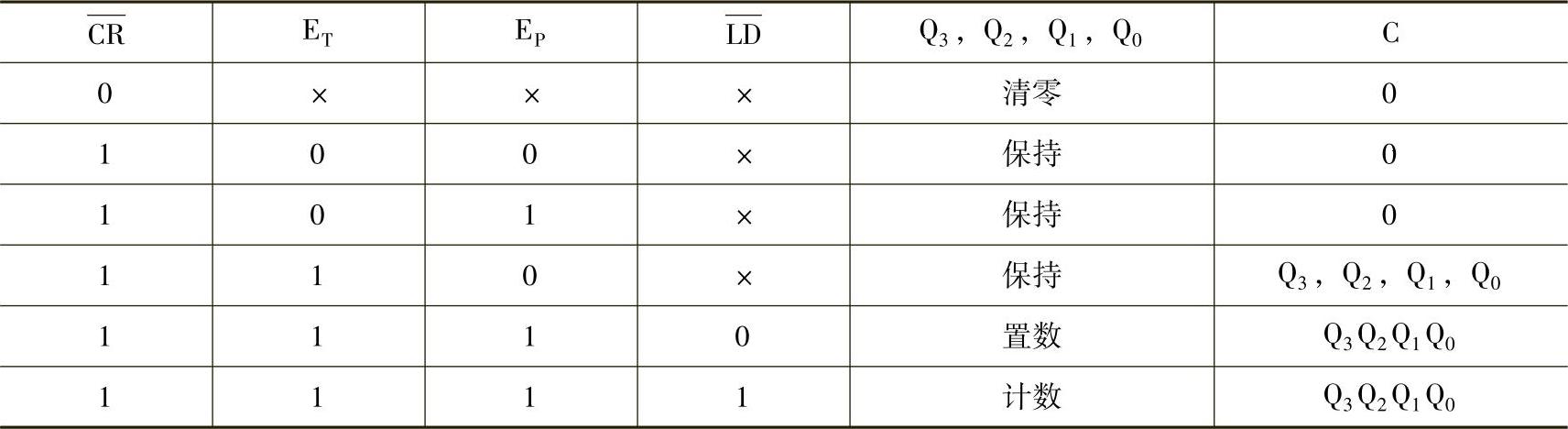

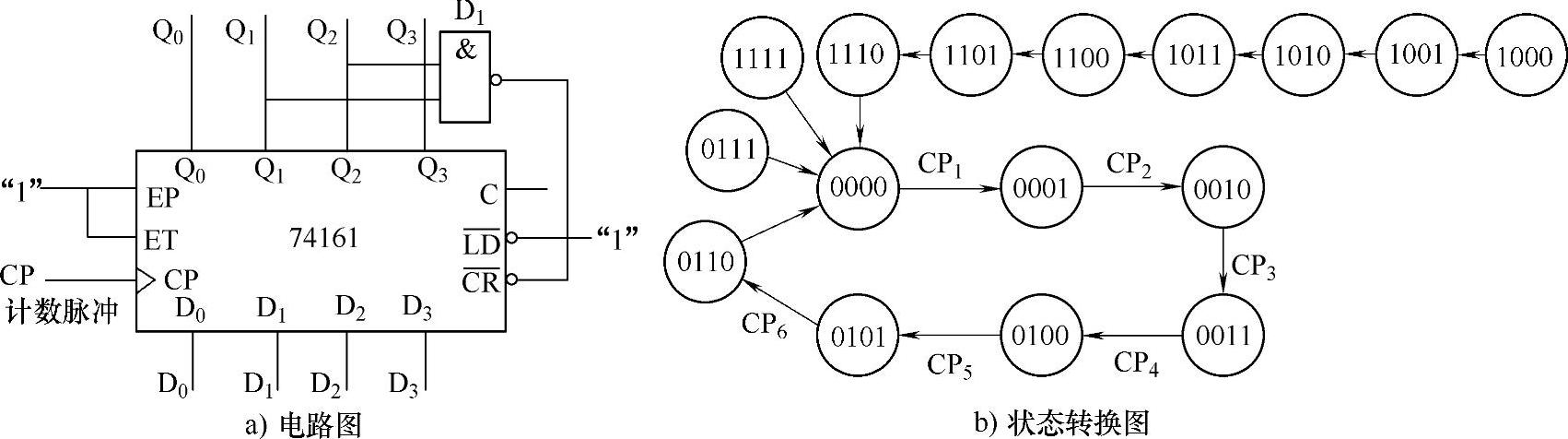

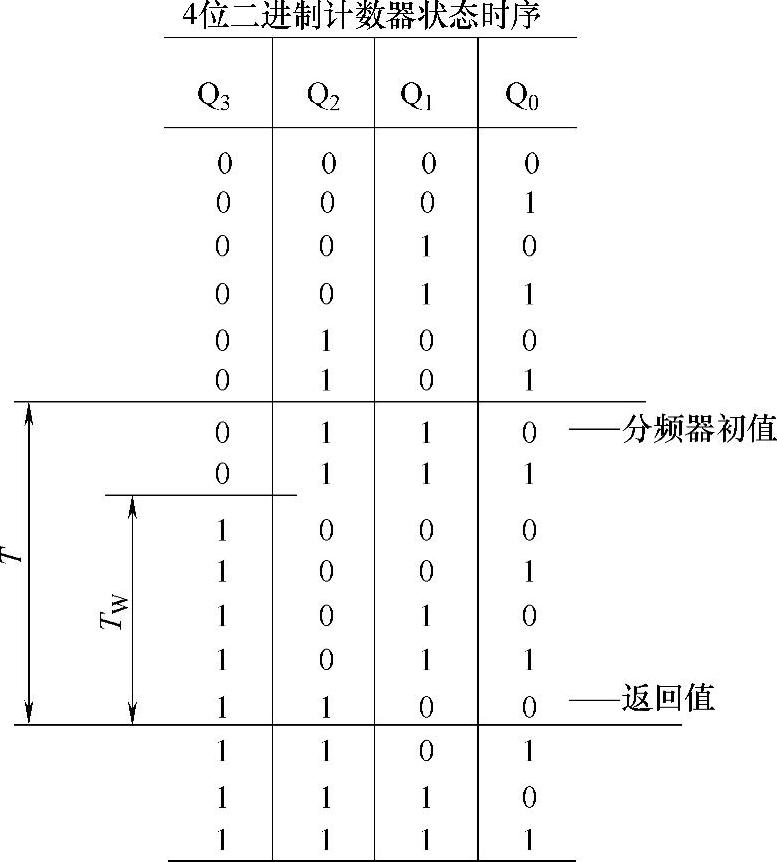

用74161构成十进制计数器,其电路连接和状态转换图如图4-132所示,电路的起始值预置为D3D2D1D0=0110。

图4-132 用置入最小值法将74161接成十进制计数器

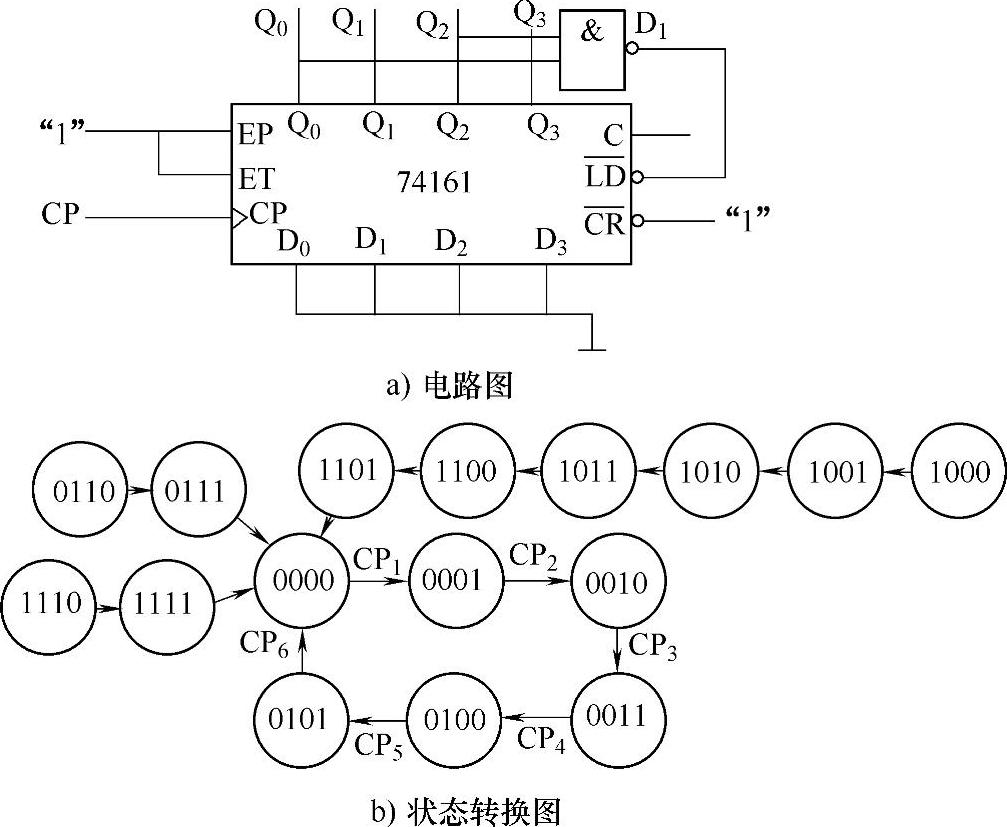

使用强制复位法并另设进位电路,用74161也可构成初始值为0的任意进制加法计数器,图4-133所示为一个六进制计数器。

图4-133 用复位法将74161接成六进制计数器

当然,用复位法不如预置法简单,图4-134所示为用预置法改制的六进制计数器电路和状态转换图。

图4-134 用置位法将74161接成六进制计数器

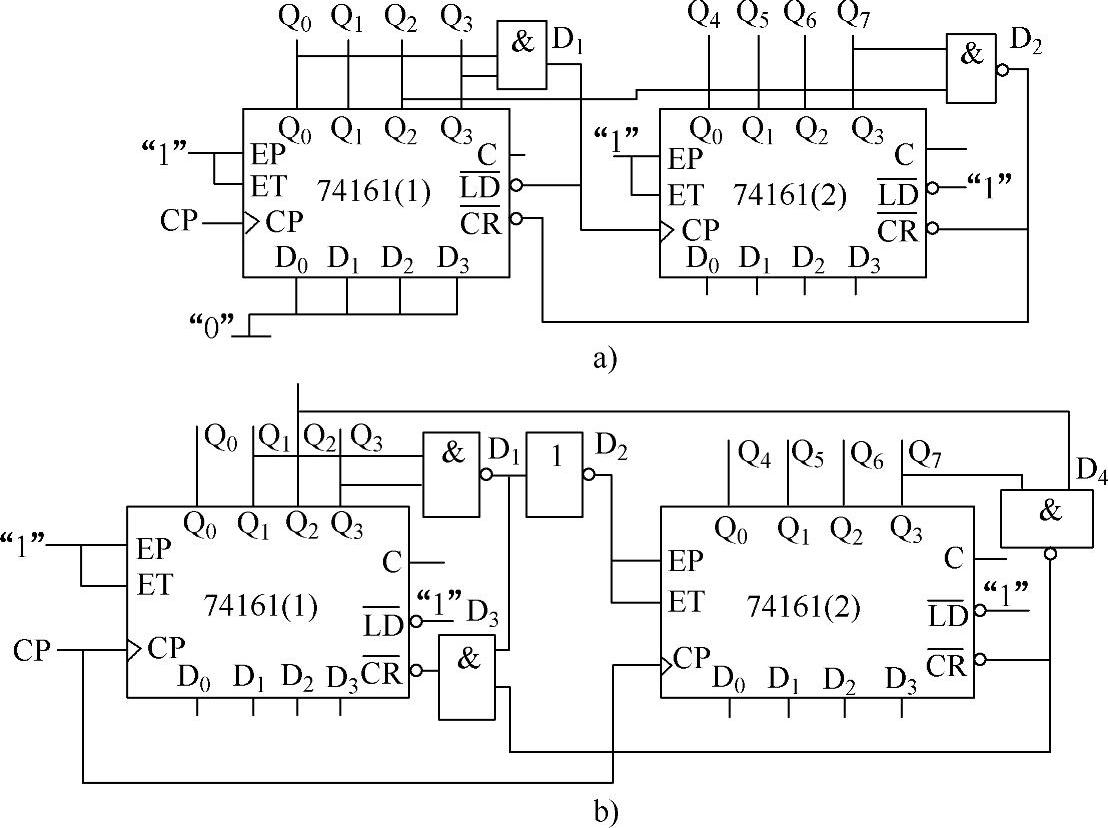

成品集成电路计数器可以通过级联构成更多位计数器,图4-135所示为用两片74161构成的八十四进制计数器。

图4-135 八十四进制计数器

该电路用低位74161的进位信号C与高位74161的EP与ET信号实现级联构成8位二进制计数器(二百五十六进制),并用复位法改变为八十四进制的计数器。

(2)分频器

计数器有分频功能,这在前面已介绍过。在实用中,对分频器的要求并不局限于分频,还有脉冲占空比和输出位置等问题。

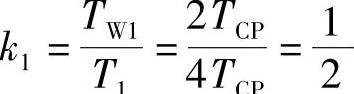

在脉冲电路中,脉冲宽度TW与信号周期T之比称为信号的占空比k:

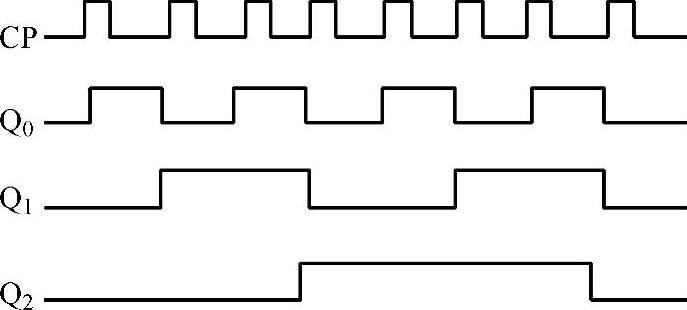

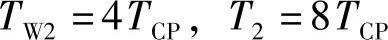

1)二进制计数器的分频效果。图4-136所示为3位二进制同步计数器的输出波形。

图4-136 3位二进制同步计数器输出波形图

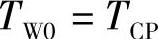

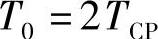

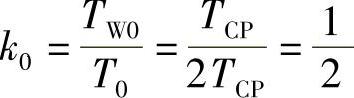

Q0端信号为时钟信号的二分频,脉冲宽度为

信号周期:

式中 TCP——时钟信号周期。

Q0信号的占空比为

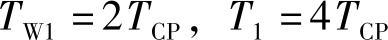

Q1端信号为时钟信号的四分频:

占空比为

Q,端信号为时钟信号的八分频:

占空比为

占空比为1/2的分频器称为对称分频,二进制计数器就是对称分频器。

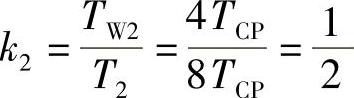

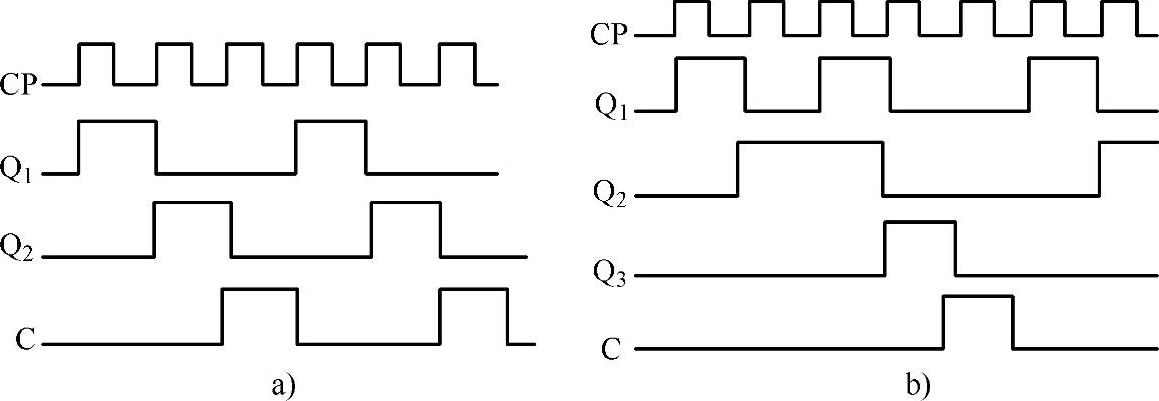

2)任意分频器。计数器具有分频器功能,而且计数器的进制类型就是分频器的分频率。图4-137所示的三进制和五进制计数器的工作波形即可说明。

分析三进制计数器的输入、输出波形,Q1、Q2、C 3个信号都是时钟信号CP的三分频,占空比都是1/3,但脉冲输出时间不同。

分析五进制计数器的输入、输出波形,Q0信号的波形特殊,Q2、Q3、C 3个信号都是时钟信号CP的五分频,Q1的占空比为2/5,Q2、C的占空比都是1/5,出现不同占空比的分频信号。

3)分频器的占空比设计。一个N分频的分频器就是一个N进制计数器。用多位二进制计数器改为N进制计数器,也是N分频的分频器。在设计过程中同时考虑占空比,就可得到占空比符合要求的N分频器。

图4-137 三进制、五进制计数器工作波形图

设计任意占空比的分频器常用另设法或截取法。

以设计一个占空比为5/7的分频器为例说明两种方法。

另设法是指在N进制计数器电路中按占空比要求另设分频信号,此法简单、灵活,二进制计数器的状态应用充分。设计过程如下:

①按2n-1<7<2n确定n=3,七分频器可用3位二进制计数器改制。

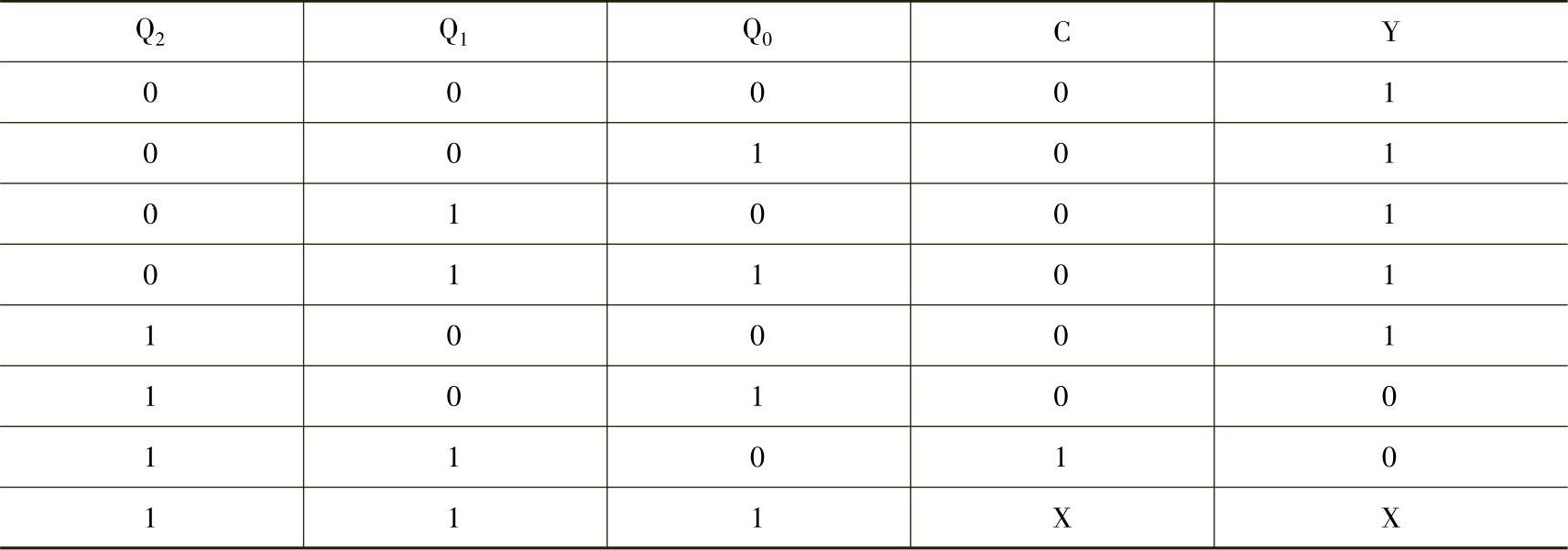

②设定改制信号C和分频信号Y,列出二进制计数器的状态真值表,见表4-54。

表4-54 二进制计数器状态真值表

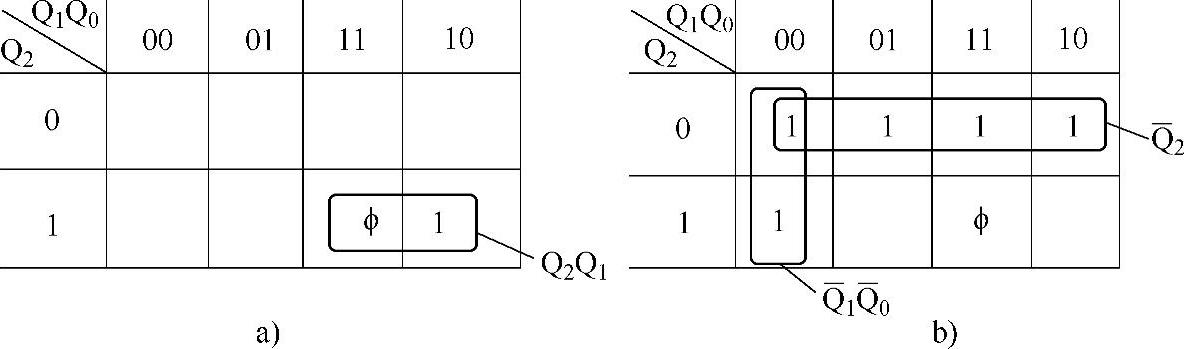

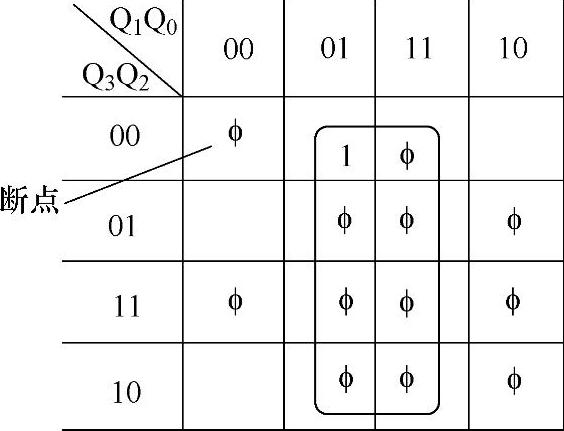

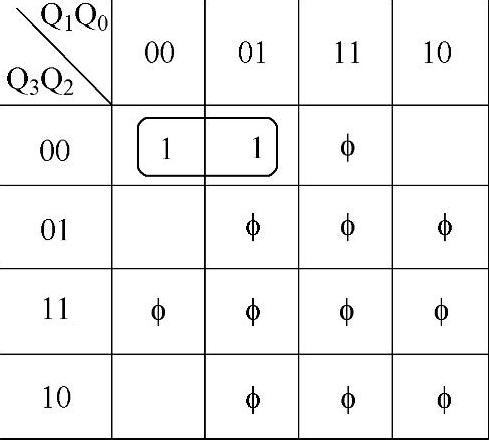

对C、Y两信号的逻辑进行化简,如图4-138所示。

图4-138 C、Y化简

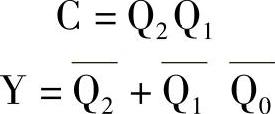

C、Y两信号的逻辑表达式:

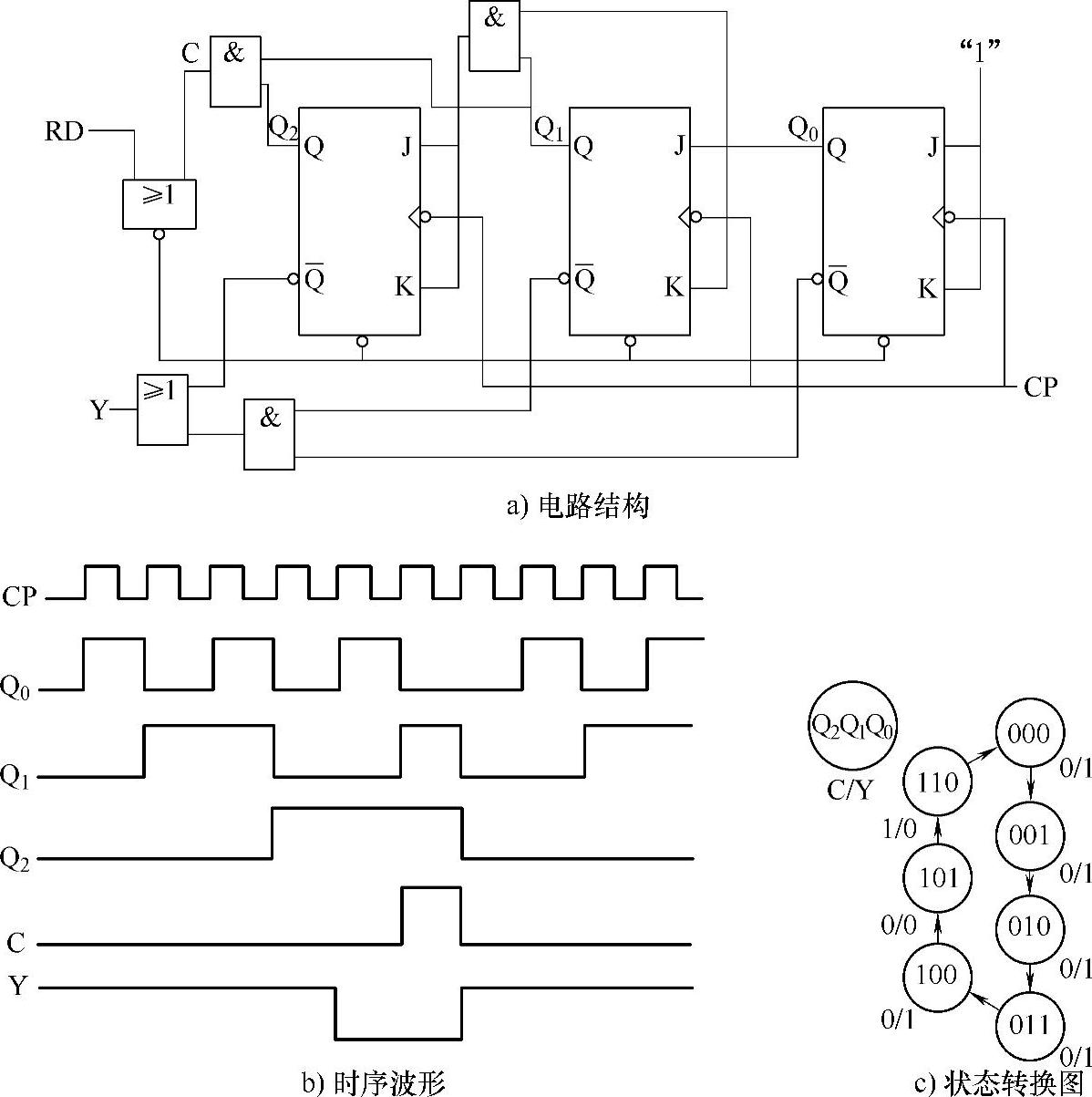

③画出电路结构、电路的时序波形和状态转换图(见图4-139),其中Y信号即占空比为5/7的七分频信号。

图4-139 七分频(5/7占空比)电路结构、时序波形、状态转换图

截取法是选择相应二进制计数器,按占空比和分频参数选用计数器的输出信号,并在计数器的状态真值表中截取符合要求的状态组作为分频器的状态转换时序。

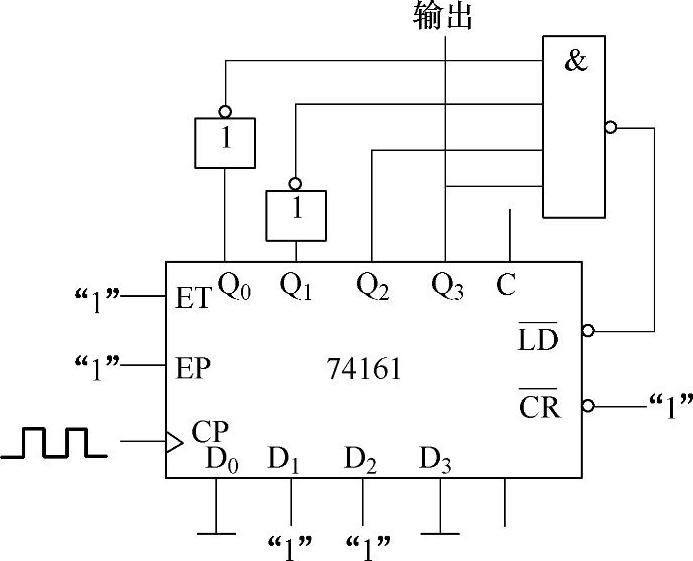

图4-140所示为截取法示意图。

从图4-140中可以确定分频器的初值为0110,返回信号逻辑 。

。

用4位二进制计数器74161制作这个七分频器,如图4-141所示。

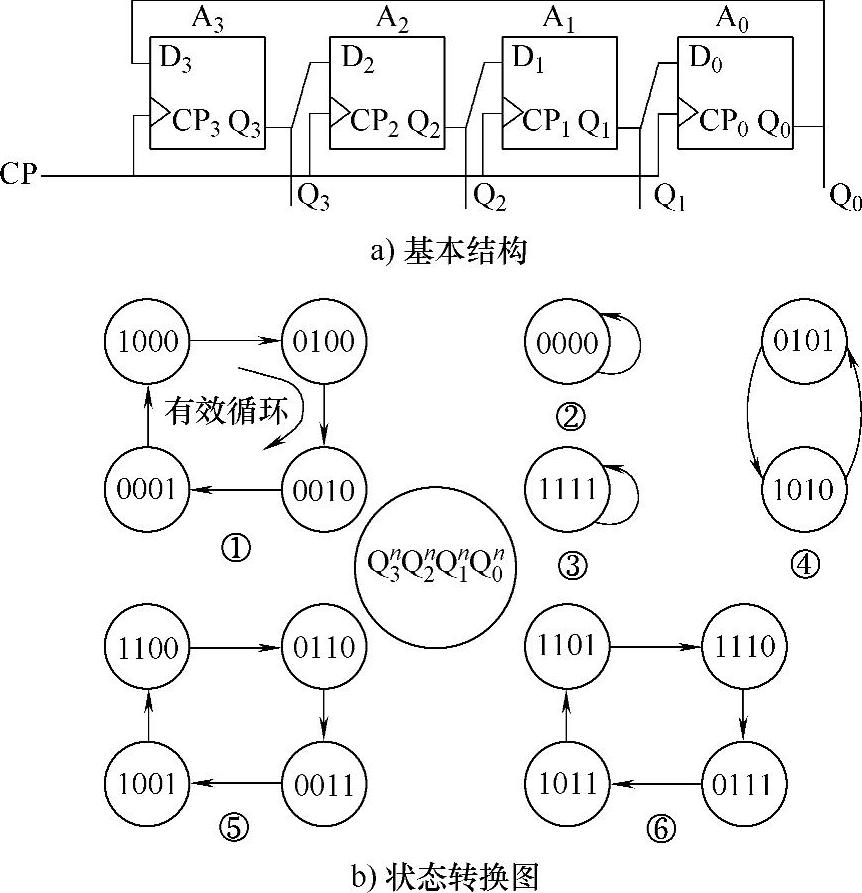

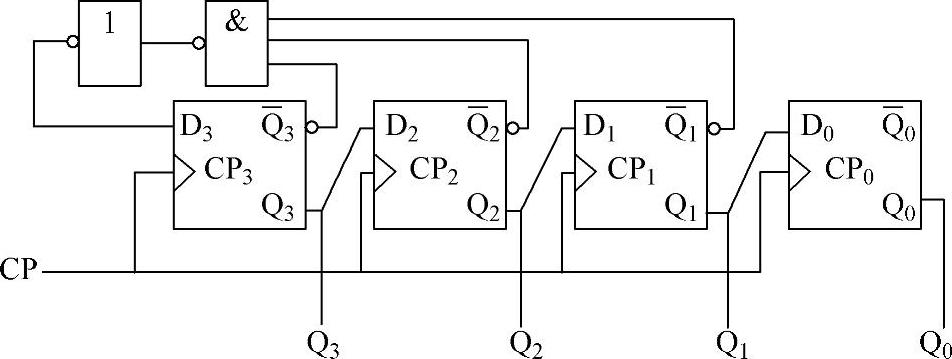

(3)环形计数器

1)基本结构。把单向移位寄存器的串行输入与串行输出两端接在一起,就构成循环移位寄存器,称为环形计数器。图4-142a所示为一个4位环形计数器的基本结构,图4-142b所示是环形计数器的6种循环状态,使用时可根据实际需要选定一种作为有效循环(②与③两种为无用循环),其余的则是无效循环。

图4-140 截取法示意图

图4-141 74161接成七分频器

图4-142 4位环形计数器及状态转换图

2)添加自启动电路。这种环形计数器不能由无效状态自然进入有效循环,叫做无自启动功能。使用时必须为其预置有效状态,受干扰进入无效循环也不能自行返回。为使用方便,应对电路进行修改,添加自启动电路,让环形计数器能由无效循环自动进入有效循环。(https://www.daowen.com)

自启动电路的设计步骤:

①在电路中任选一个修改点(如选在A3的输入逻辑D3);

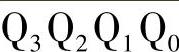

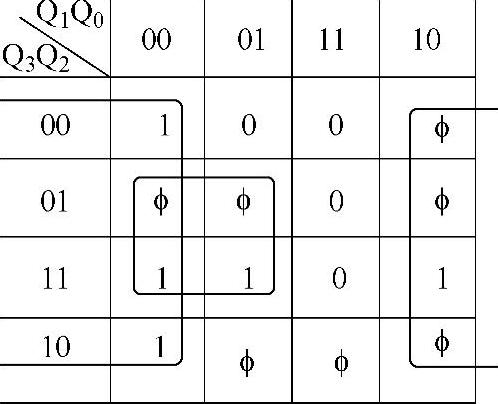

②按确定的有效循环(见图4-142b①)列出电路有效状态转换表(见表4-55)。制出FF3状态Qn+13的卡诺图,并进行化简圈项(见图4-143,其中ϕ表示无效项)。

表4-55 有效状态转换表

③按以下条件确定无效循环断点:

a.必须是有效逻辑化简圈项外的ϕ项(必须属于无效循环)。

b.必须与一个有效循环项相邻(具有引入有效循环的可能)。

在卡诺图中确定断点最直观,从图4-143可以看出,符合上述条件的只有 一项。按相邻的有效逻辑值改写该项,把无效循环断开,就能将无效循环引入有效循环。这就是自启动电路的设计原理。

一项。按相邻的有效逻辑值改写该项,把无效循环断开,就能将无效循环引入有效循环。这就是自启动电路的设计原理。

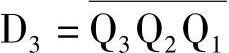

④对修改点的逻辑重新化简(见图4-144),得出修改点的新逻辑表达式(含必要的变换), (修改之前D3=Q0)。

(修改之前D3=Q0)。

图4-143 断点选择

图4-144 重新化简

⑤按新逻辑表达式画出修改后的逻辑图,如图4-145所示。

图4-145 修改后的环形计数器

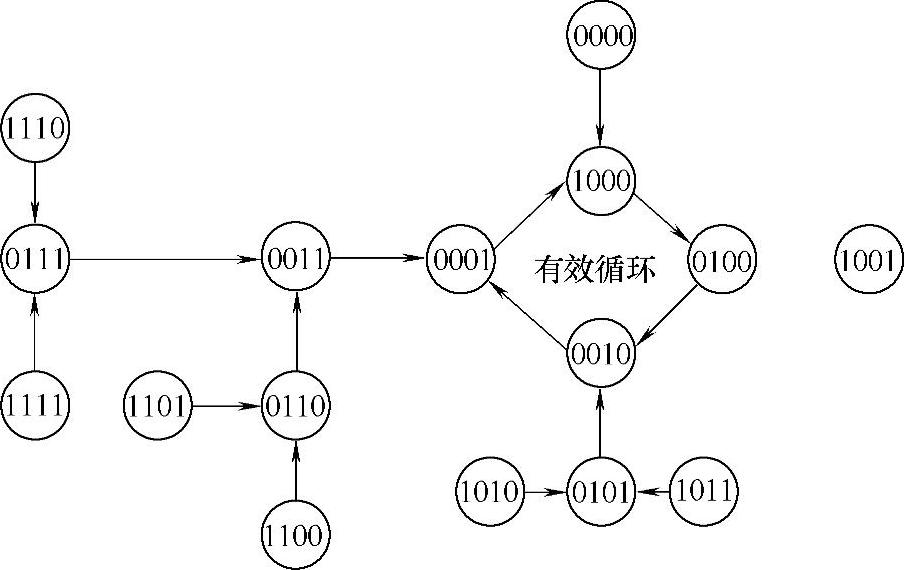

⑥检验自启动效果(若不理想,则需更换或增加断点),画出自启动状态转换图(见图4-146)。

图4-146 能自启动的环形计数的状态图

(4)扭环计数器设计

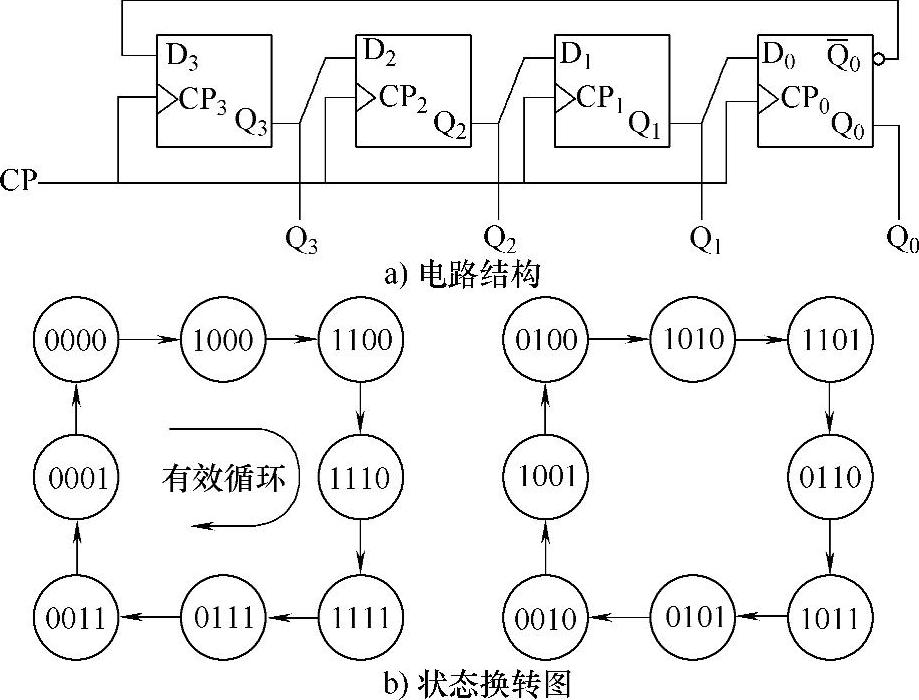

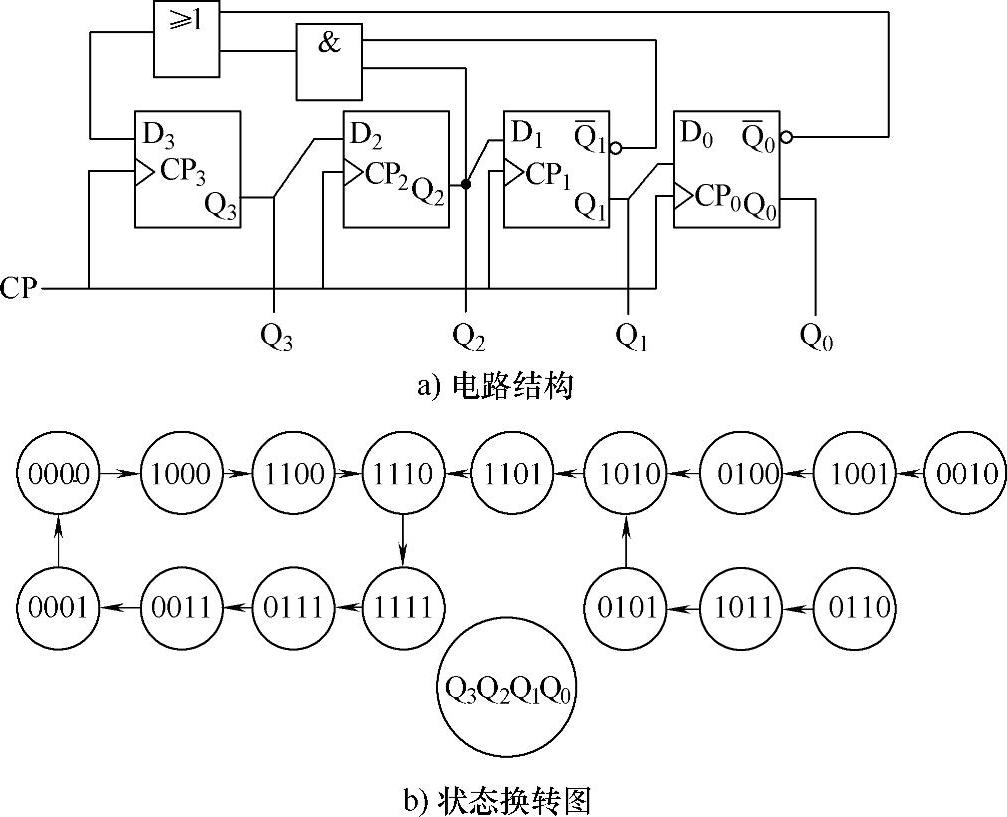

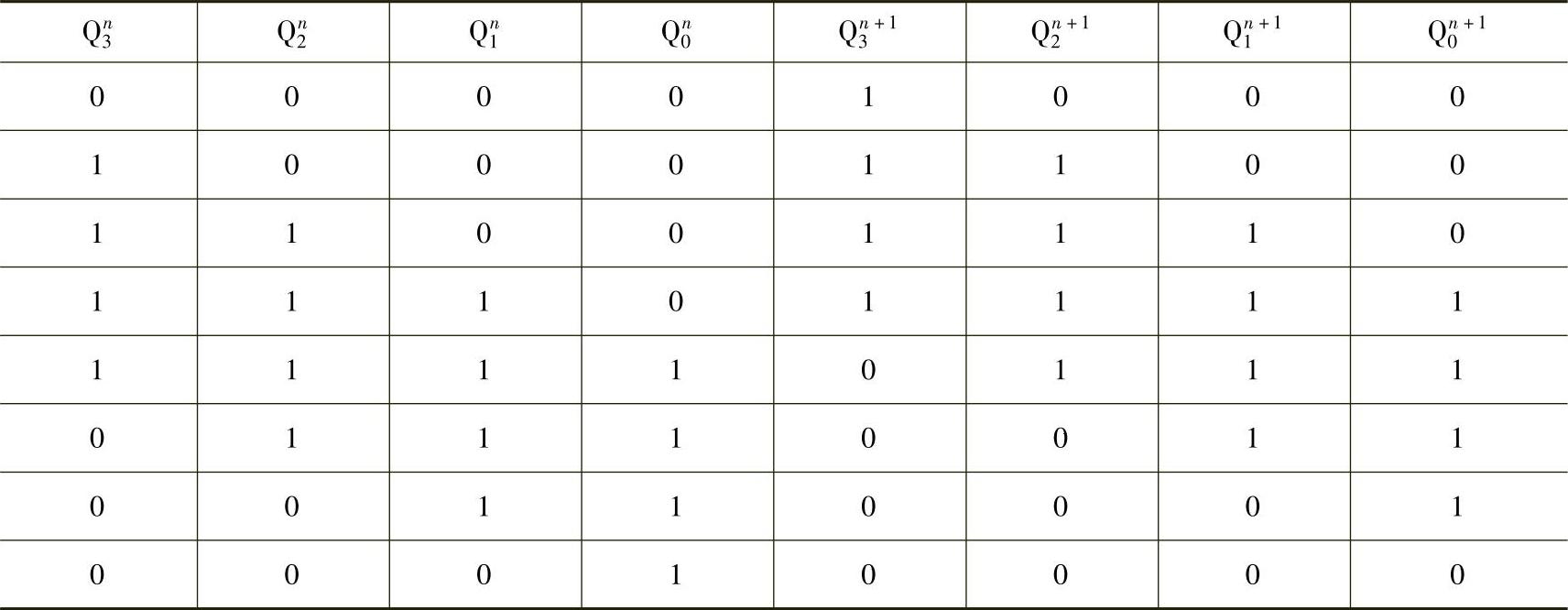

1)扭环计数器的基本结构。把移位寄存器的串行输出的反相端引回输入端,就构成扭环计数器。图4-147所示为一个4位扭环计数器电路的基本结构和状态转换图,它有两个独立的状态循环,但不能自启动。

图4-147 扭环计数器

2)添加自启动电路。和环形计数器一样,扭环也要经过修改,使其具备自启动功能。修改逻辑的化简过程如图4-148所示(修改D3的输入逻辑)。

图4-148 修改逻辑的化简

修改后的电路结构和状态转换图如图4-149所示。

图4-149 能自启动的4位扭环计数器电路结构与状态转换图

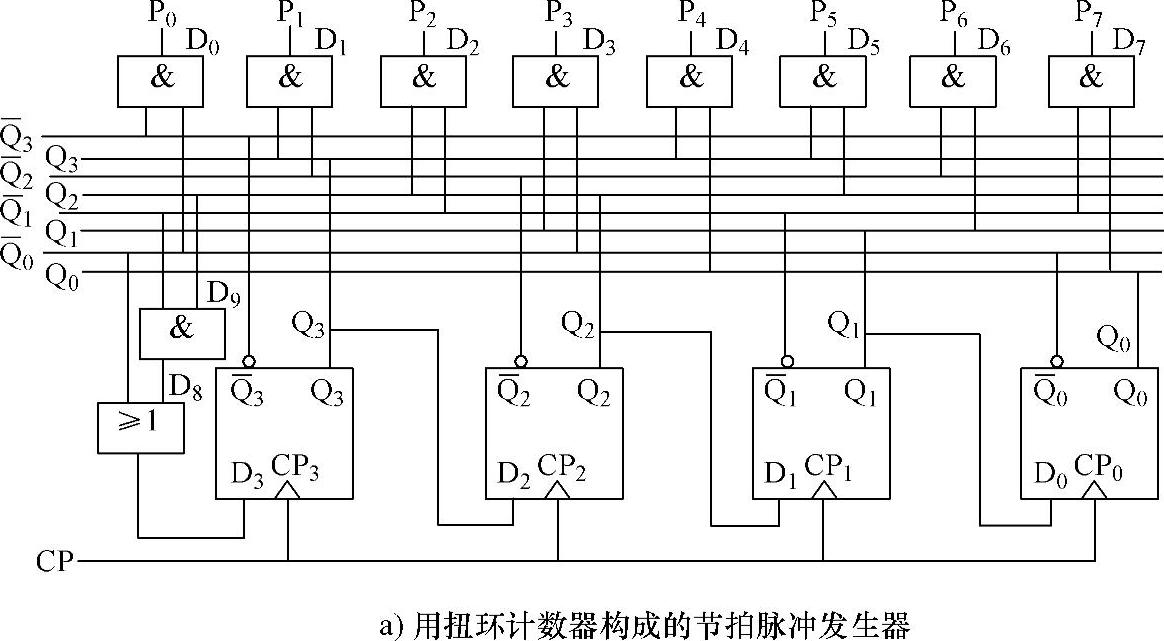

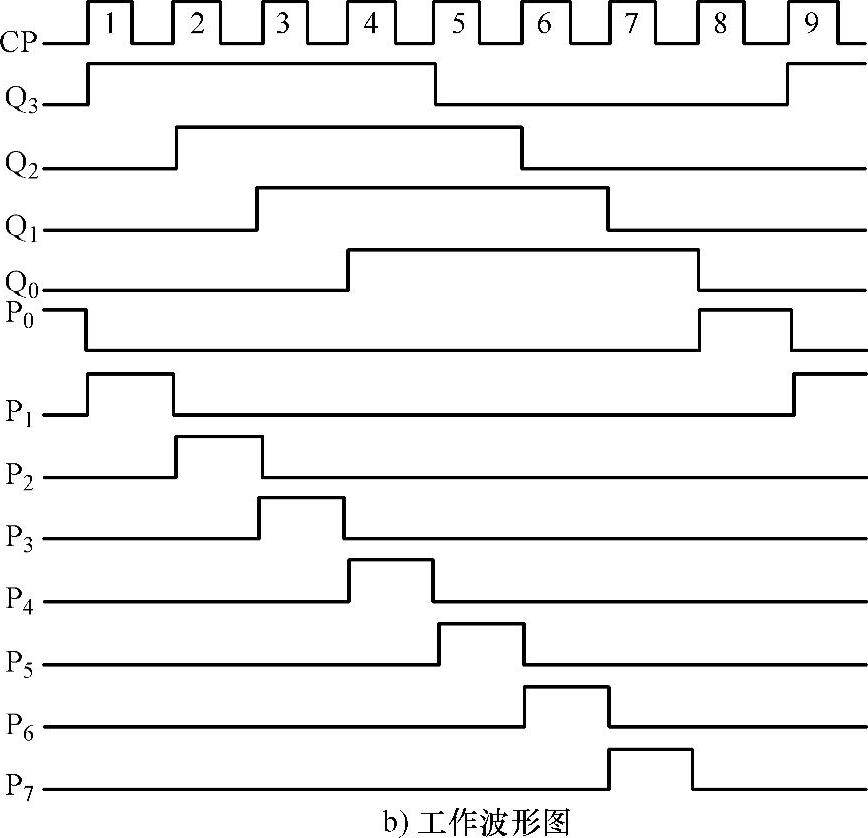

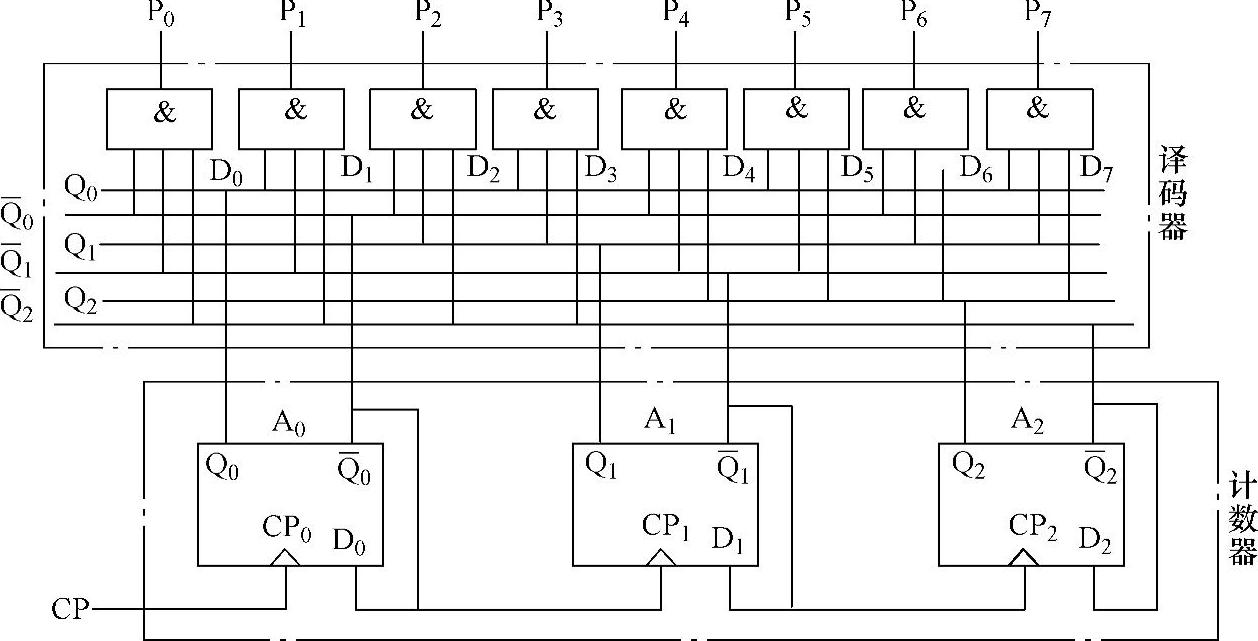

扭环计数器的有效输出状态数量虽比环形计数器提高一倍,但输出脉冲位数仍受到触发器数量的限制。为了获得更大规模的脉冲序列,可将扭环计数器与译码器相连接,如图4-150所示,这个电路可输出8位序列脉冲。

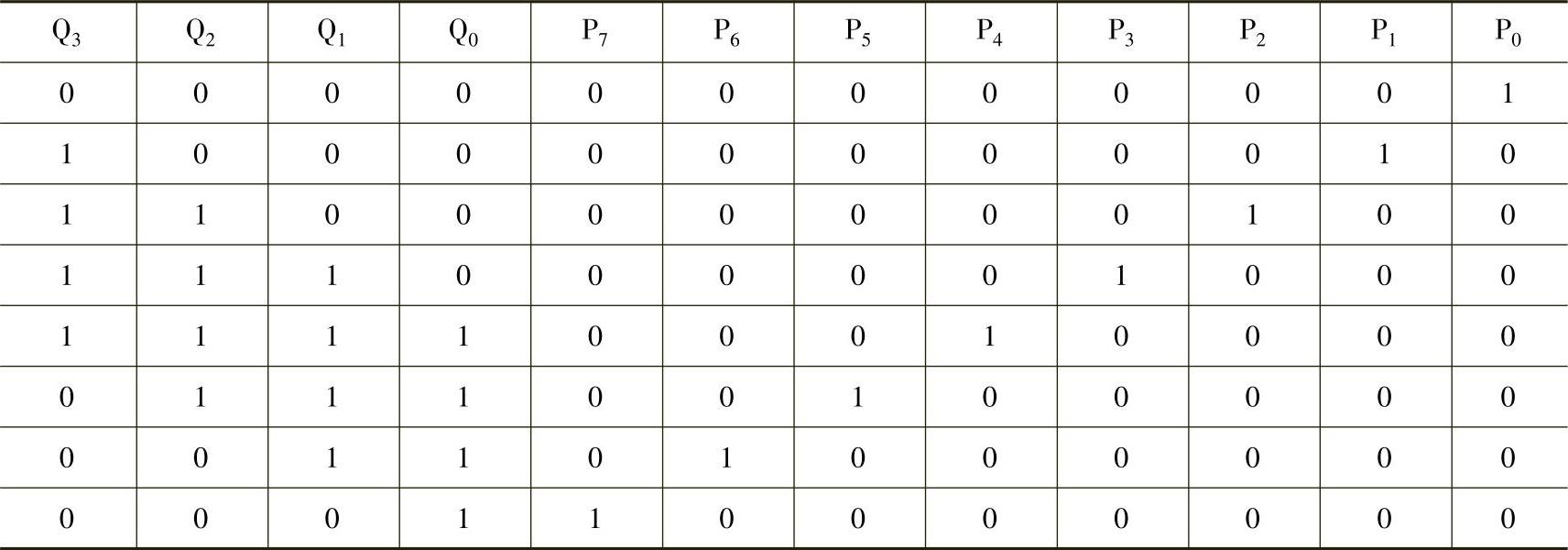

扭环计数器的有效循环中只有2N-1个状态变化,它虽有两组状态循环,在自启动电路引入后其状态循环则固定为一组。译码器的结构却可依据输出状态的需要灵活设计。表4-56是图4-150的功能转换表,表4-57为译码真值表,是按单脉冲输出方式设计的。

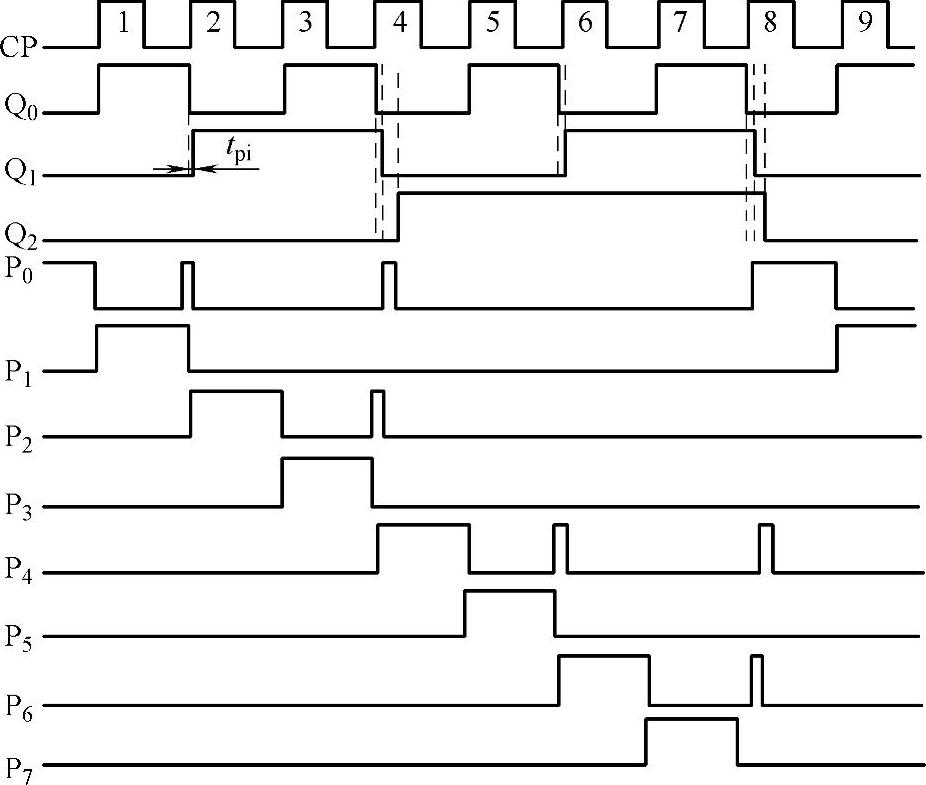

图4-150 用扭环计数器构成的节拍脉冲发生器及工作波形

图4-150 用扭环计数器构成的节拍脉冲发生器及工作波形(续)

表4-56 扭环计数器有效循环状态转换表

表4-57 译码真值表

(5)节拍器

数字系统对其负荷的控制操作常常要求控制信号在时间上有先后顺序,需要有固定时间顺序的信号作为基准。能产生顺序脉冲的电路称为顺序脉冲发生器,又称节拍器。

节拍器可用计数器和译码器构成,也可用扭环计数器构成。

1)用计数器和译码器构成的节拍器。图4-151所示节拍器是用3位二进制异步计数器和一只3线—8线译码器组成的计数器型节拍器。

图4-151 计数型节拍器

计数器型节拍器比扭环节拍器少用一只触发器,但因各触发器不可能同时翻转,会使计数器出现竞争冒险现象而输出干扰脉冲。如计数器从001向010变化过程中,会出现FF0已从1翻转为0,而FF1尚未动作的情况,使计数器输出瞬间的000,在译码器的P0端出现一个尖峰脉冲。电路输出波形如图4-152所示。

图4-152 计数器型节拍器工作波形

2)用扭环计数器构成节拍器。计数器型节拍器若采用同步计数器也能消除竞争冒险现象。扭环形节拍器不存在竞争冒险问题。

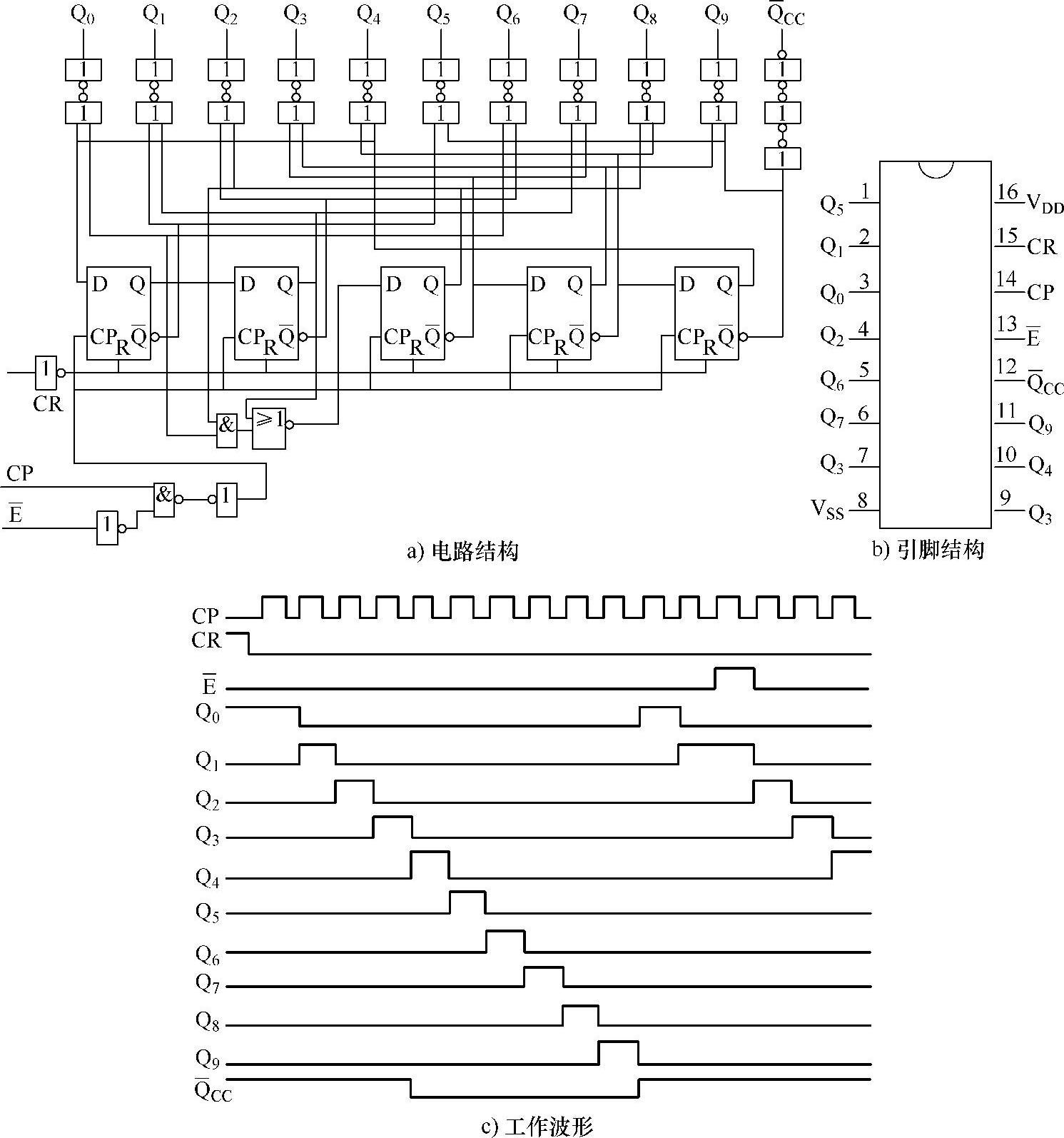

4017B为十进制计数器/脉冲分配器,图4-153所示为该电路的电路结构、引脚结构和波形图。

图4-153 4017B

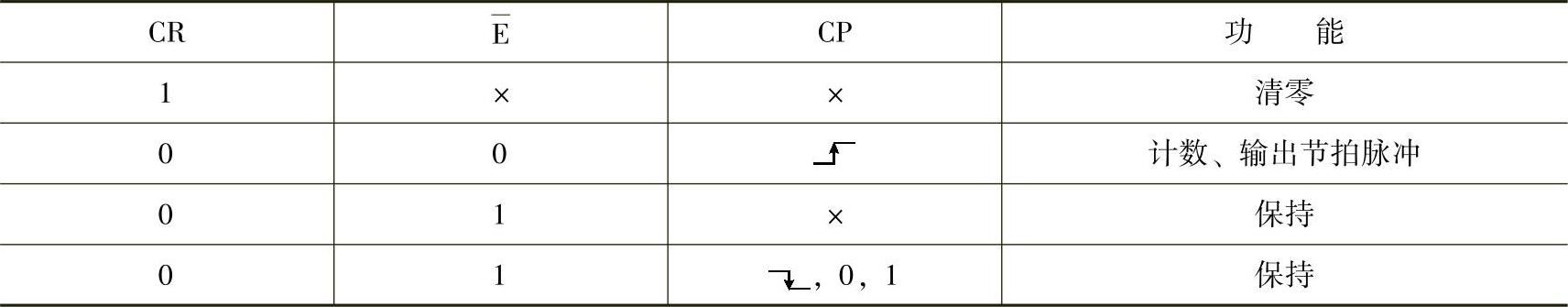

表4-58为4017B的逻辑功能表。

表4-58 4017B逻辑功能表

CR为高电平清零端; 为低电平有效的使能端,用以控制时钟信号,

为低电平有效的使能端,用以控制时钟信号, 为高电平时,时钟信号被禁止;CP为上升沿触发的计数脉冲信号;Q0~Q9为节拍信号输出端。

为高电平时,时钟信号被禁止;CP为上升沿触发的计数脉冲信号;Q0~Q9为节拍信号输出端。 为计数器进位信号输出端。

为计数器进位信号输出端。

2.简单时序电路设计

对于功能简单或没有相关成品可用的时序电路,就需要设计者自己制作。

(1)D触发器应用简例

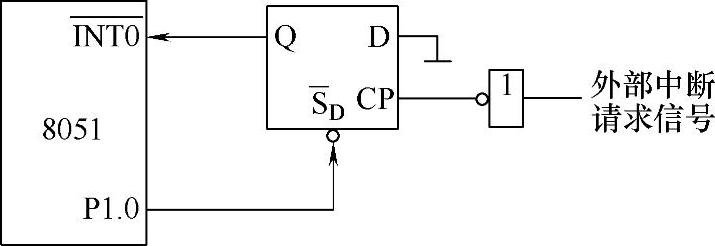

用D触发器为单片机8051存储中断请求信号的电路如图4-154所示。

图4-154 用D触发器构成8051中断请求电路

单片机8051的片外中断请求信号INT0(低电平有效),在8051响应并实施中断服务操作过程中,片外中断请求信号 要始终保持有效状态。

要始终保持有效状态。

电路利用D触发器存储作用将片外中断请求信号 保持到8051的中断响应完成,由P1.0口输出低电平将D触发器置1(高电平)为止。

保持到8051的中断响应完成,由P1.0口输出低电平将D触发器置1(高电平)为止。

电路动作原理:把D触发器的同步输入端D固定接地(构成低电平输入)作为片外中断请求信号 ,触发器的输出端Q信号与8051的

,触发器的输出端Q信号与8051的 信号入口连接。选用CP为上升沿触发的D触发器。平时P1.0口输出高电平,对触发器不起作用。当外部设备需要8051的中断服务时,P1.0口就发出一个低电平脉冲,经非门倒相变为高电平送入触发器的时钟信号CP端(上升沿触发),信号脉冲的前沿触发触发器,D端的低电平进入触发器,Q端输出低电平,发出中断请求信号。8051响应中断请求、并执行相应的中断服务程序,完成中断服务后,由P1.0口发出一个低电平信号(对CP端无影响)给D触发器的SD端,使触发器直接置1,触发器Q端输出高电平,撤销中断请求。

信号入口连接。选用CP为上升沿触发的D触发器。平时P1.0口输出高电平,对触发器不起作用。当外部设备需要8051的中断服务时,P1.0口就发出一个低电平脉冲,经非门倒相变为高电平送入触发器的时钟信号CP端(上升沿触发),信号脉冲的前沿触发触发器,D端的低电平进入触发器,Q端输出低电平,发出中断请求信号。8051响应中断请求、并执行相应的中断服务程序,完成中断服务后,由P1.0口发出一个低电平信号(对CP端无影响)给D触发器的SD端,使触发器直接置1,触发器Q端输出高电平,撤销中断请求。

此例是8051单片机用外中断方式为内中断服务,中断请求和结束中断都由P1.0口发出信号。对于真正外部设备的中断请求信号可调整电平后接在D触发器的CP端。

(2)J-K触发器应用简例

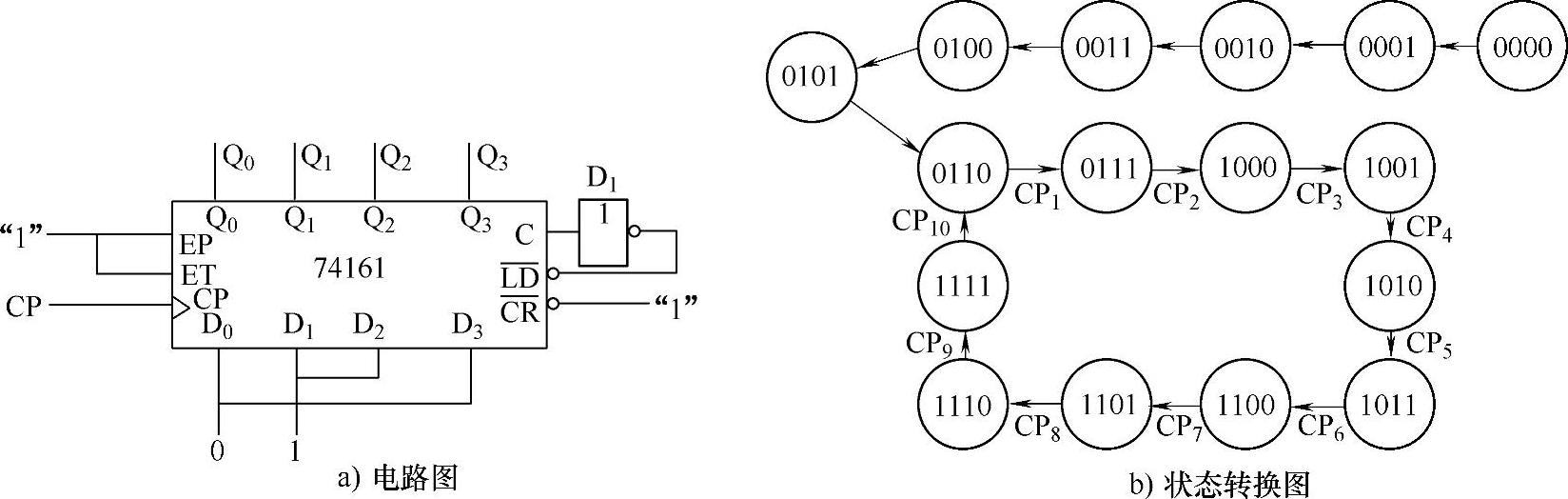

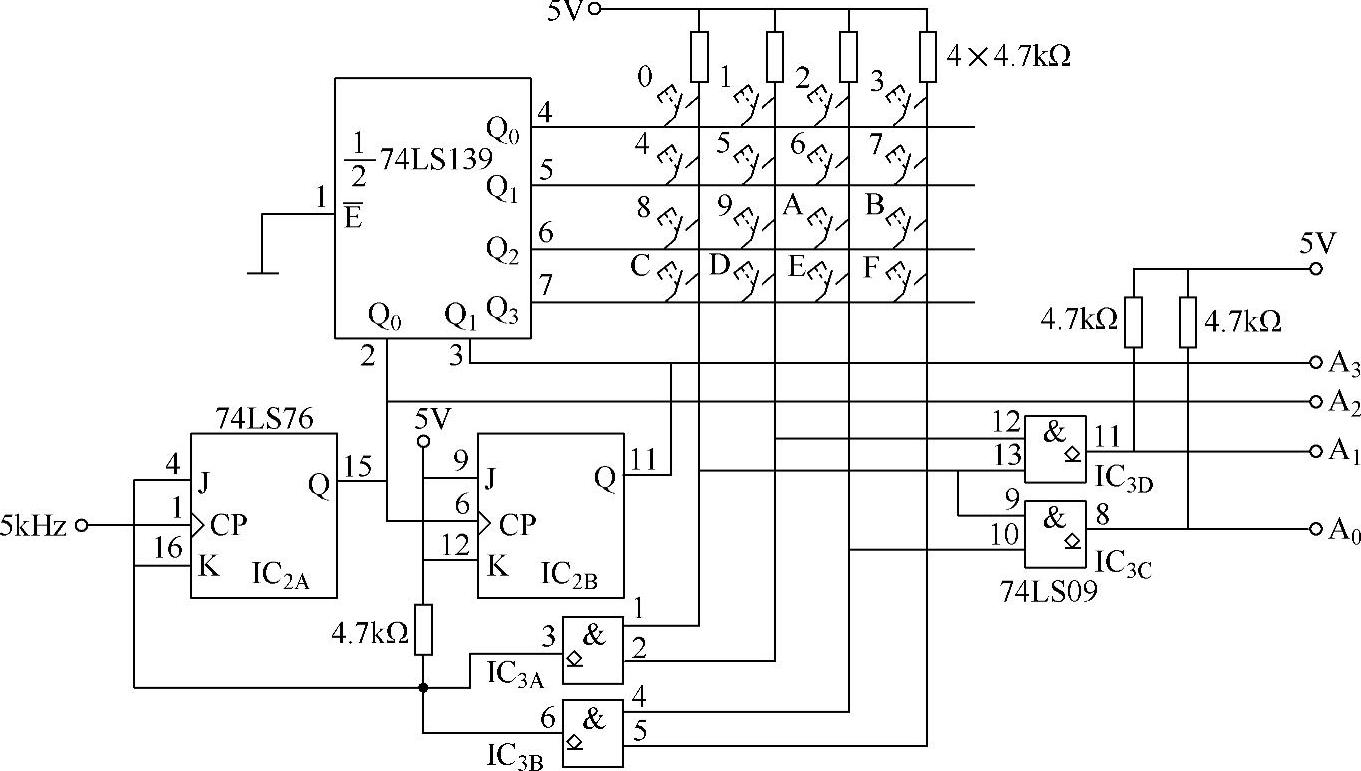

图4-155所示为一例十六进制键盘编码器电路。

图4-155 十六进制键盘编码器电路

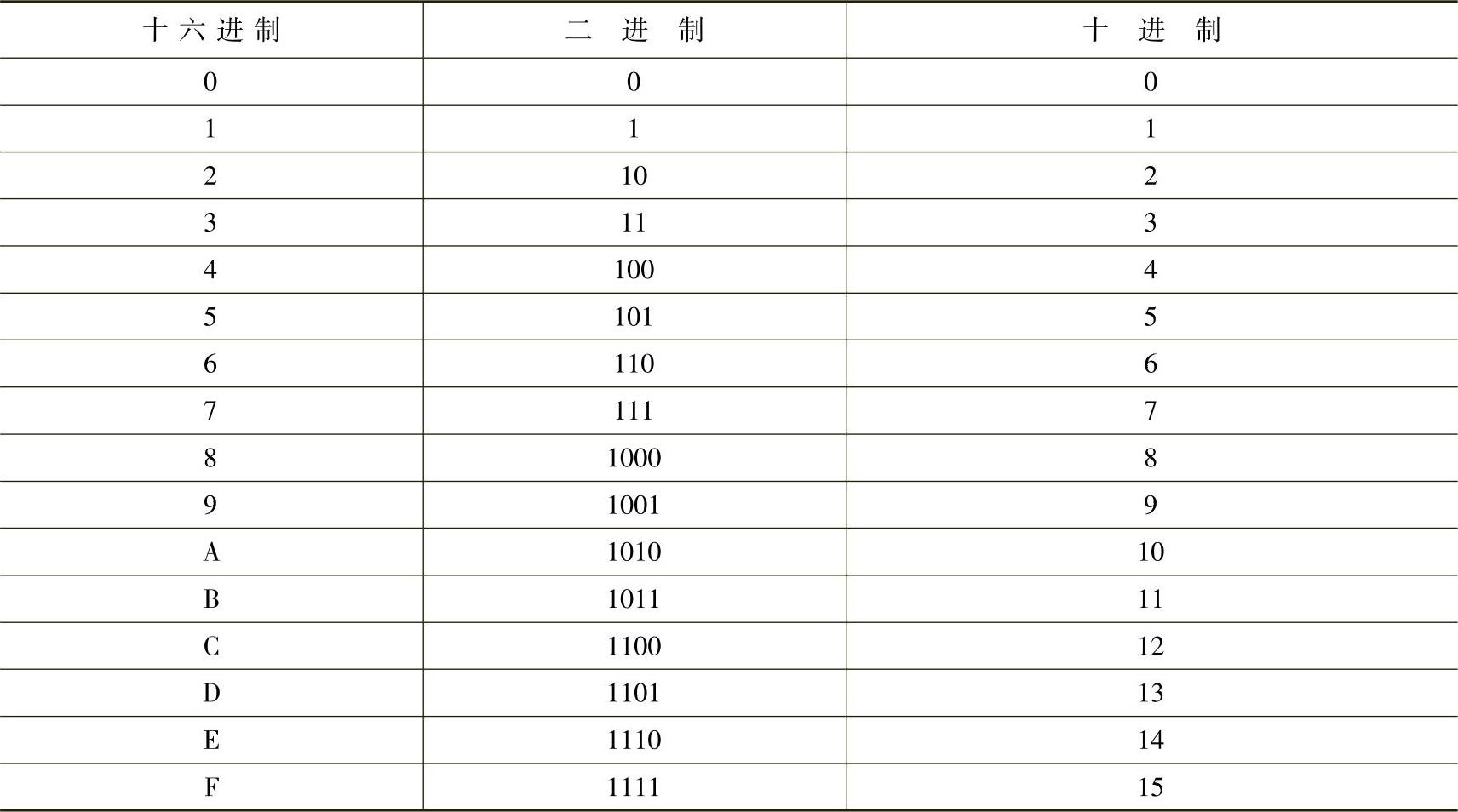

十六进制是用0~9和A、B、C、D、E、F 6个字母计数的方法,逢十六进一。在计算机软件系统中,主要用作二进制码的缩写,十六进制与二进制的对应关系见表4-59。

表4-59 十六进制、二进制及十进制对照表

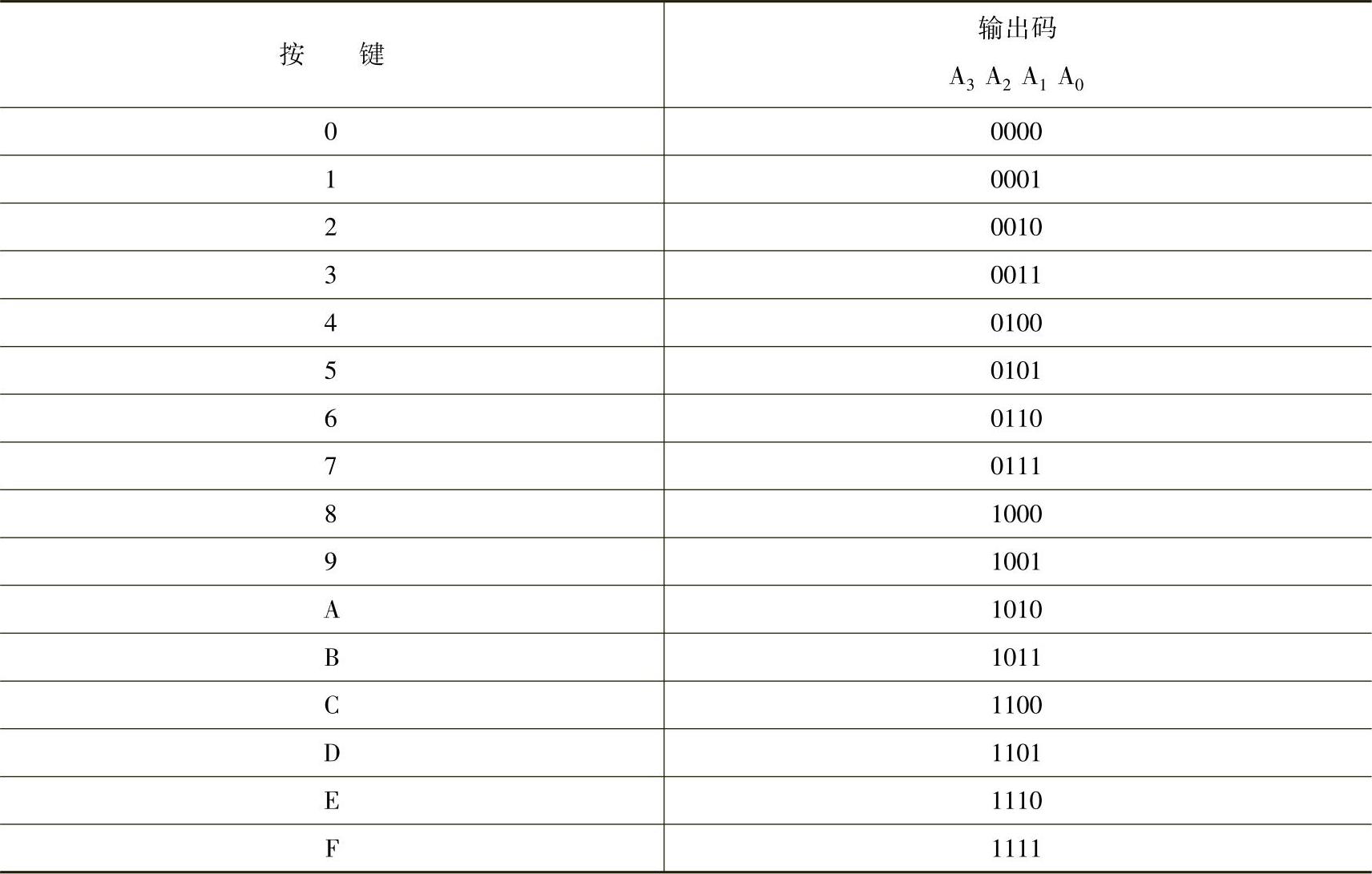

电路的功能是将0~F 16个按键动作转换为A3、A2、A1、A04位输出码的不同状态,按键与输出码的对应关系见表4-60。

表4-60 按键与输出码的对应表

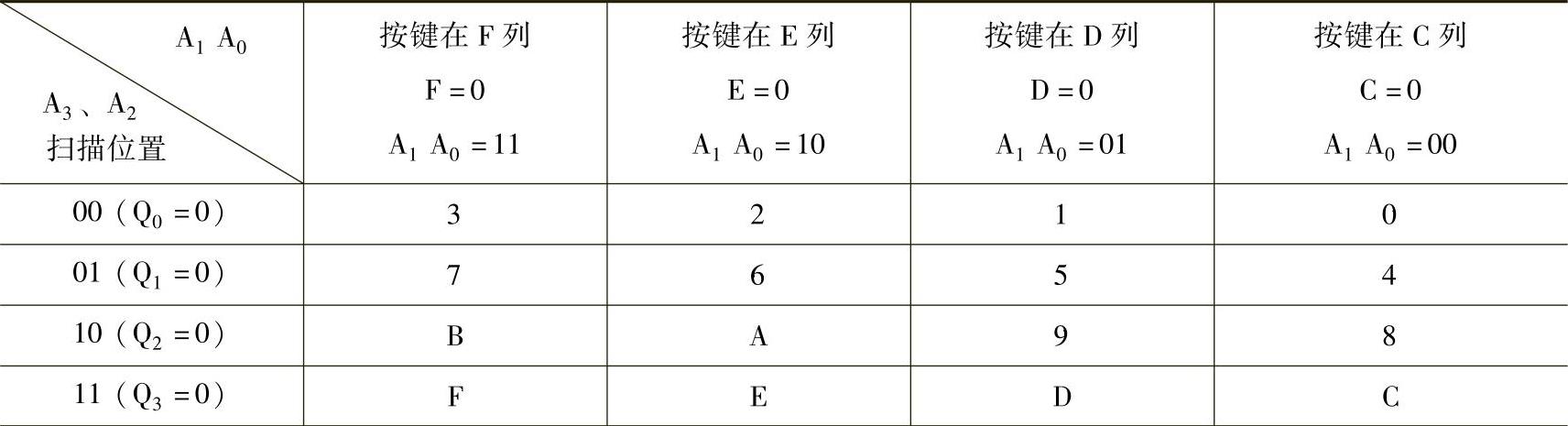

电路中的时序电路由74LS76(双J-K触发器)构成,IC2A转换为T触发器,IC2B转换为T′触发器,两者共同组成一个两位二进制减法异步计数器。计数器输出作为电路输出编码中的A3、A2两位,同时又是74LS139译码输入信号D1、D0。

74LS139(双2-4译码器)的使能信号( )接地,总处于工作状态,负责为16个开关键阵列输出扫描信号,用OC与门(74LS09,输出端接有4.7kΩ上拉电阻)负责读键盘,查找被按动的键。其中两个(IC3A、IC3B)合并为一个4输入端的与逻辑门,用于控制计数器,当有键被按住时就输出0,计数器停止动作,保持输出数据不变,形成电路输出码的高两位A3、A2,确定按键所在的行位。另外两个(IC3D、IC3C)用于形成电路输出码的低两位A1、A0,确定按键所在的列位。

)接地,总处于工作状态,负责为16个开关键阵列输出扫描信号,用OC与门(74LS09,输出端接有4.7kΩ上拉电阻)负责读键盘,查找被按动的键。其中两个(IC3A、IC3B)合并为一个4输入端的与逻辑门,用于控制计数器,当有键被按住时就输出0,计数器停止动作,保持输出数据不变,形成电路输出码的高两位A3、A2,确定按键所在的行位。另外两个(IC3D、IC3C)用于形成电路输出码的低两位A1、A0,确定按键所在的列位。

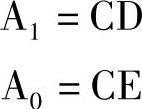

用C、D、E、F分别代表4列(纵线)键信号,A1、A0两位数值由C、D、E、F 4列键信号决定。它们之间的逻辑关系是

C、D、E、F 4列键信号在无按键时都为高电平;有按键时键开关把行、列线接通,键所在的列线被74LS139输出的扫描信号拉为低电平。键盘编码A3A2A1A0的形成可用表4-61说明。

表4-61 键盘编码形成表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。