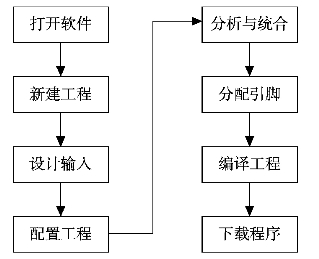

Quartus软件的使用流程如图3-38所示。

从图中可以看出,首先打开Quartus软件,然后新建一个工程,在新建工程的时候,可以通过创建工程向导的方式来创建工程;工程建立完成后,需要新建一个Verilog顶层文件,然后将设计的代码输入到新建的Verilog顶层文件中,并对工程进行配置;接下来就可以对设计文件进行分析与综合了,此时Quartus软件会检查代码,如果代码出现语法错误,那么Quartus软件将会给出相关错误提示,如果代码语法正确,Quartus软件将会显示编译完成;工程编译完成后,需要给工程分配引脚,引脚分配完成后,接下来就开始编译整个工程了;在编译过程中,Quartus软件会重新检查代码,如果代码及其他配置都正确后,Quartus软件会生成一个用于下载至FPGA芯片的.sof文件。最后,通过下载工具将编译生成的.sof文件下载至电路板,完成整个开发流程。

接下来以流水灯实验的工程为例,熟悉QuartusⅡ软件的使用。

图3-38 Quartus软件使用流程

(1)新建工程。

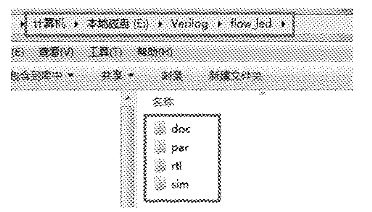

为方便管理,在创建工程之前,通常在硬盘中新建一个文件夹用于存放自己的Quartus工程。需要注意的是,这个工程目录的路径名应该只有字母、数字和下划线,以字母为首字符,且不要包含中文和其他符号;不能将硬盘的根目录作为工程目录,否则不能进行统合编译。工程文件夹的命名要能反映出工程实现的功能,现以流水灯的实验为例,将文件夹命名为flow_led。然后在flow_led文件夹下创建4个子文件夹,分别命名为:doc、par、rtl和sim。doc文件夹用于存放项目相关的文档,par文件夹用于存放Quartus软件的工程文件,rtl文件夹用于存放源代码,sim文件夹用于存放项目的仿真文件。创建的文件夹目录如图3-39所示。

图3-39 工程文件夹目录

建议大家在开始创建工程之前都要先创建这四个文件夹,如果说工程相对简单,不需要相关参考文档或者仿真文件的话,doc文件夹和sim文件夹可以为空,但是对于复杂的工程,相关文档的参考与记录以及仿真测试几乎是必不可少的,所以从简单的实验开始就要养成良好的习惯,为设计复杂的工程打下基础。

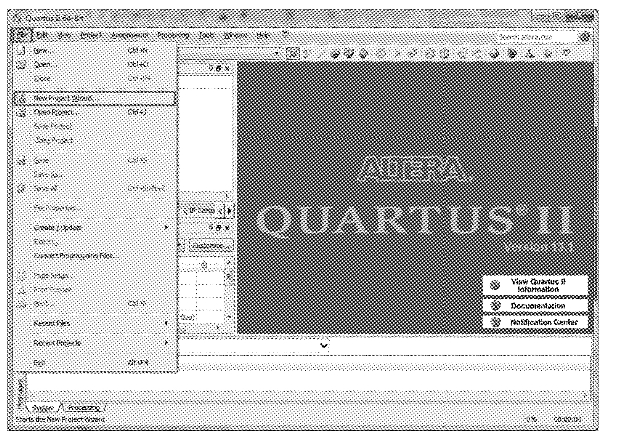

接下来启动QuartusⅡ软件。在菜单栏上选择File→New Project Wizard…来新建一个工程,如图3-40所示。

图3-40 新建工程操作界面

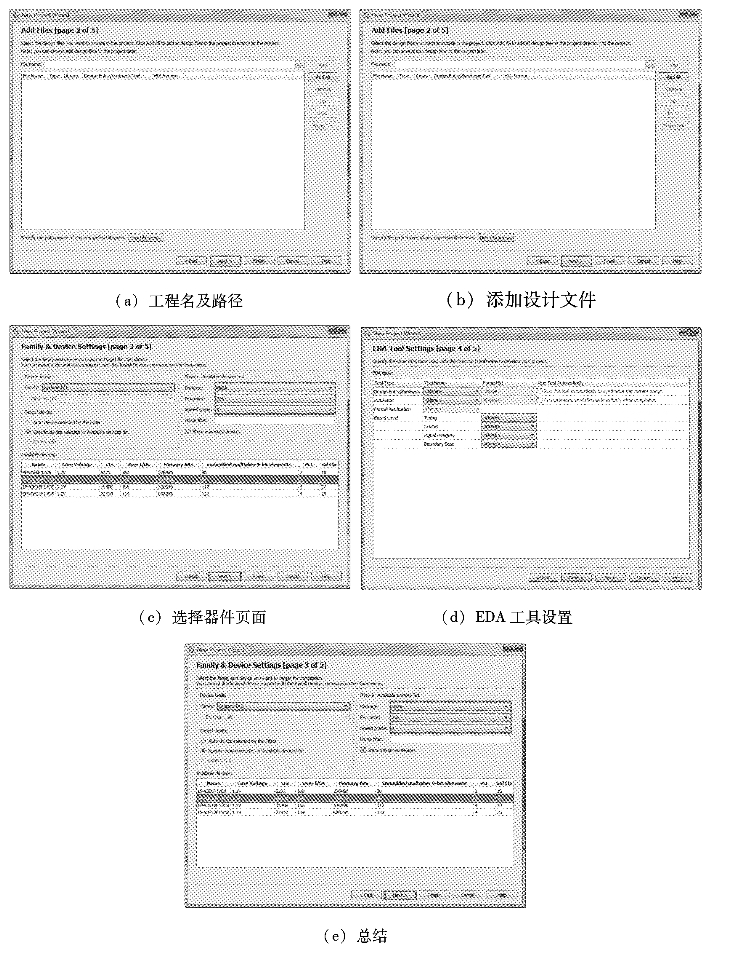

在新建工程向导说明页面中,可以了解到在新建工程的过程中要完成以下五个步骤:

a.工程的命名以及指定工程的路径。

b.指定工程的顶层文件名。

c.添加已经存在的设计文件和库文件。

d.指定器件型号。

e.EDA工具设置。

单击Next按钮进入图3-41(a)所示工程名及路径页面。

图3-41(a)的第一栏用于指定工程所在的路径;第二栏用于指定工程名,这里建议大家直接使用顶层文件的实体名作为工程名;第三栏用于指定顶层文件的实体名。设置的工程路径为E:/Verilog/flow_led/par文件夹,工程名与顶层文件的实体名同为flow_led。文件名和路径设置完毕后,单击Next按钮,如图3-41(b)所示。在该页面中,通过点击“…”符号按钮添加已有的工程设计文件(Verilog或VHDL文件),由于这里是一个完全新建的工程,没有任何预先可用的设计文件,所以不用添加,直接单击Next按钮,进入如图3-41(c)所示页面。这里要根据实际所用的FPGA型号来选择目标器件,单击Next按钮进入如图3-41(d)所示页面。在“EDA Tool Settings”页面中,可以设置工程各个开发环节中需要用到的第三方EDA工具,比如:仿真工具Modelsim、综合工具Synplify。如果没有使用任何的EDA工具,此页面保持默认不添加第三方EDA工具,直接单击Next进入图3-41(e)所示页。从该页面中,可以看到工程文件配置信息报告,点击Finish完成工程的创建。

图3-41 创建工程向导页面

此时返回到Quartus软件界面,可以在工程文件导航窗口中看到刚才新建的flow_led工程,如果需要修改器件的话,直接双击工程文件导航窗口中的“Cyclone IV E:EP4CE10F17C8”即可。

(2)设计输入。

下面创建工程顶层文件,在菜单栏中找到File→New,弹出如图3-42所示,以使用Verilog HDL语言来作为工程的输入设计文件为例,在Design Files一栏中选择Verilog HDL File,然后点击OK按钮。

图3-42 创建Verilog文件

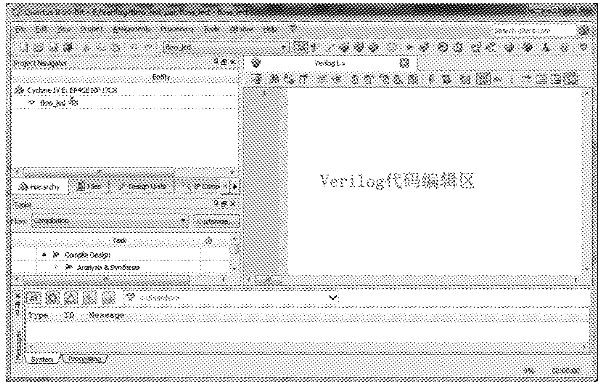

在主窗口编辑区会出现一个Verilogl.v文件的设计界面,用于输入Verilog代码,如图3-43所示。

图3-43 创建Verilog文件工程界面

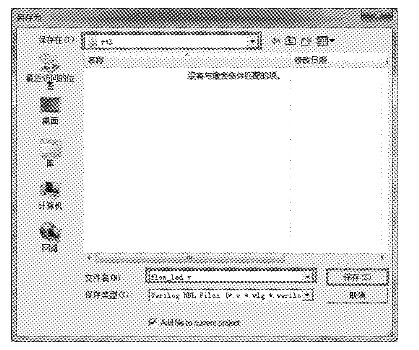

接下来在该文件中编写流水灯代码。代码编写完成后进行保存,默认文件名会和所命名的module名称一致,默认路径也会是当前的工程文件夹,将存放的路径修改为rtl文件夹下,如图3-44所示。

图3-44 Verilog代码保存界面

保存代码文件后,可以在工程文件导航窗口File一栏中找到新建的flow_led.v文件。(https://www.daowen.com)

(3)配置工程。

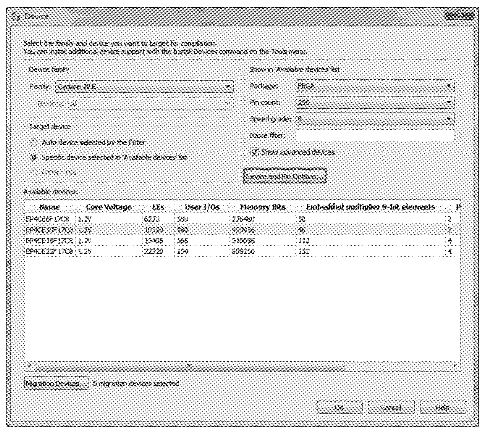

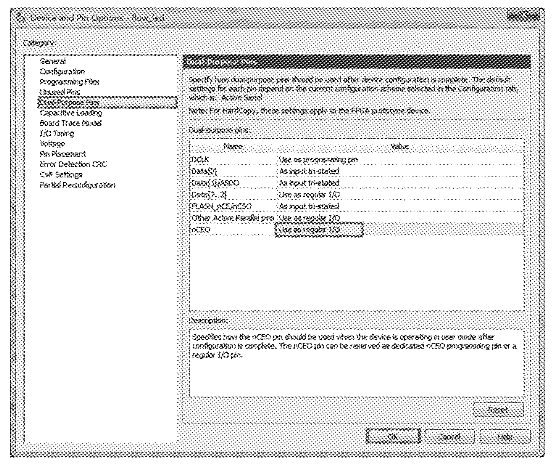

在工程中,需要配置双用的管脚。首先在Quartus软件的菜单栏中找到Assignments→Device,出现如图3-45所示页面。

图3-45 器件选择页面

该页面就是可以重新选择器件页面,然后点击Device and Pin Options按钮,会弹出一个设置页面,在左侧Category一栏中选择Dual-Purpose Pin。对于需要使用EPCS器件的引脚时,需要将下图页面中所有的引脚都改成Use as regular IO,如果不确定工程中是否用到EPCS器件时,可以全部修改。本次实验只修改了nCEO一栏中,将Use as programming pin修改为Use as regular I/O,修改完成后,点击OK按钮完成设置。设置界面如图3-46所示。

图3-46 双用的管脚设置成普通I/O

(4)分析与综合(编译)。

为了验证代码是否正确,可以在工具栏中选择Analysis & Synthesis图标来验证语法是否正确,也可以对整个工程进行一次全编译,即在工具栏中选择Start Compilation图标,不过全编译的时间耗时会比较长。接下来对工程进行语法检查,点击工具栏中的Analysis & Synthesis图标。

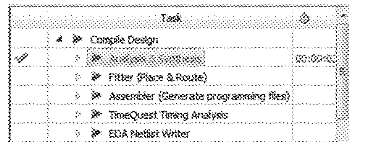

在编译过程中如果没有出现语法错误,编译流程窗口【Analysis & Synthesis】前面的问号会变成对勾,表示编译通过,如图3-47所示。

图3-47 编译完成界面

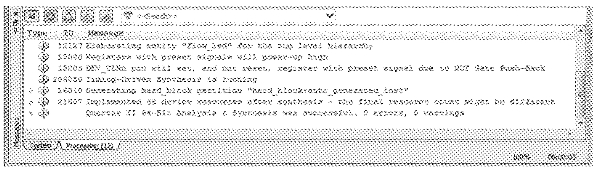

最后,可以查看打印窗口的“Processing”里的信息,包括各种“Warning”和“Error”o“Error”是必须要关心的,“Error”意味着代码有语法错误,后续的编译将无法继续,如果出现错误,可以双击错误信息,此时编辑器会定位到语法错误的位置,修改完成后,重新开始编译;而“Warning”则不一定是致命的,有些潜在的问题可以从“Warning”中寻找,如果一些“Warning”信息对设计没有什么影响,也可以忽略它。信息提示窗口界面如图3-48所示。

图3-48 信息提示窗口界面

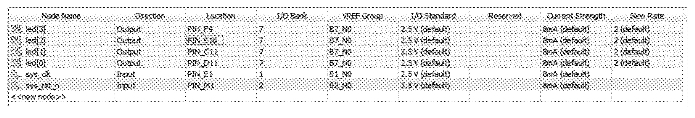

(5)分配引脚。

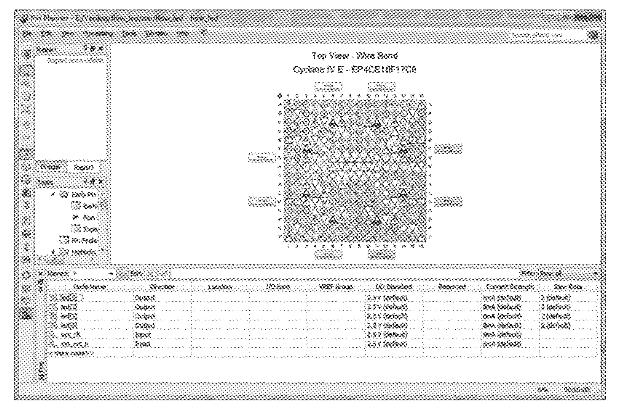

编译通过以后,接下来就需要对工程中输入、输出端口进行管脚分配。可以在菜单栏中点击Assignments→Pin Planner或者在工具栏中点击Pin Planner的图标,出现如图3-49所示引脚分配界面。可以看到该界面出现了6个端口分别是4个LED、时钟和复位,通过参考原理图及FPGA电路板IO引脚分配表来对引脚进行分配。引脚分配完成后如图3-50所示。引脚分配完成后,直接关闭引脚分配窗口,软件会在工程所在位置生成一个.qsf文件用来存放引脚信息。

图3-49 引脚分配界面

图3-50 引脚分配完成界面

(6)编译工程。

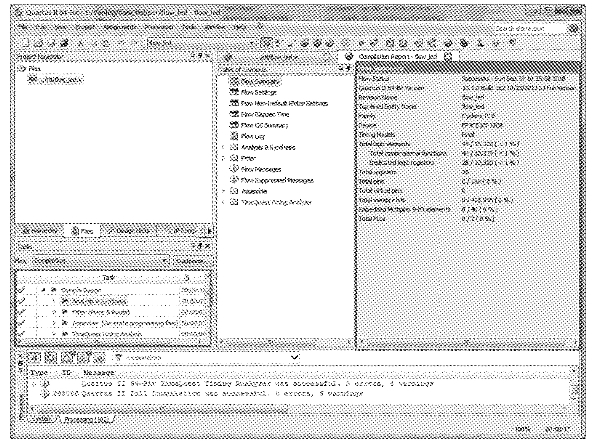

分配完引脚之后,需要对整个工程进行一次全编译,在工具栏中选择Start Compilation图标。编译完成后的界面如图3-51所示。

图3-51 全编译完成界面

在全编译完成界面中,左侧编译流程窗口全部显示打钩,说明工程编译通过,右侧Flow Summary观察FPGA资源使用的情况。

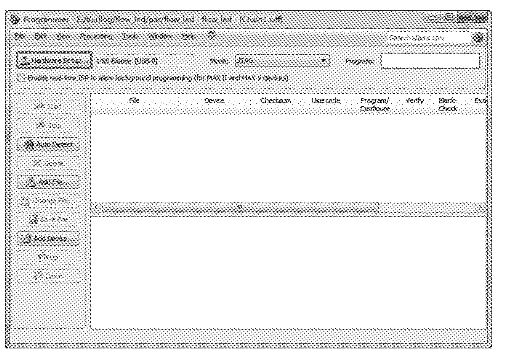

(7)下载程序。

编译完成后,就可以给电路板下载程序,来验证程序能否正常运行。首先将USB Blaster下载器一端连接电脑,另一端与电路板上的JTAG接口相连接;然后连接电路板电源线,并打开电源开关。接下来在工具栏上找到“Programmer”按钮或者选择菜单栏Tools→Programmer,程序下载界面如图3-52所示。

图3-52 程序下载界面

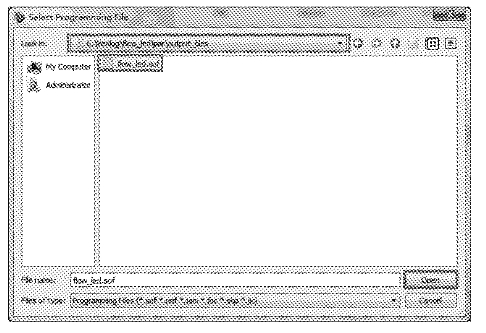

点击上图页面中的“Hardware Setup...”按钮,选择“USB-Blaster”。然后点击Close按钮完成设置,接下来回到下载界面,点击ADD File按钮,添加用于下载程序的sof文件,如图3-53所示。

图3-53 选择sof文件

找到“output_files”下面的“flow_led.sof”文件点击Open即可。接下来点击Start按钮下载程序。下载程序时,可以在Process一栏中观察下载进度,程序下载完成后,可以看到下载进度为100%。下载完成之后,可以看到电路板上的DS0~DS3按顺序点亮,呈现出流水灯的效果。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。