HRPWM是基于微边沿定位器(MEP)技术的。MEP逻辑电路通过细分常规PWM发生器的粗系统时钟,能够很精细地定位一个边沿。时间步的精度是150ps的数量级。对具体的器件,典型的MEP步大小需参考相应的手册来确定。HRPWM还具有一个自检软件诊断模式,以检测在各种运行条件下MEP逻辑是否最优运行。

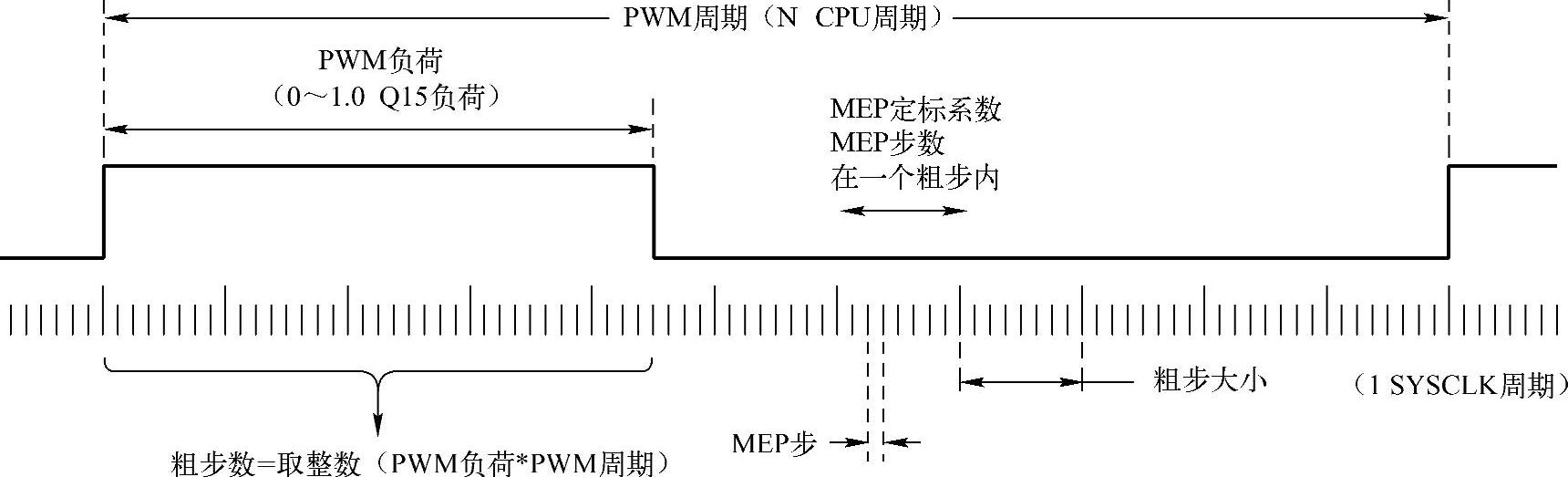

图7-28给出了粗系统时钟与以MEP步表示的边沿位置的关系,该边沿位置可以由比较A寄存器(CMPAHR)的8位域控制。图中,MEP步数=取小数(PWM负荷∗PWM周期)∗(MEP定标系数)+0.5(圆整),对于MEP范围与圆整调整,Q8格式为0x0080。而且有

16位CMPA寄存器值=粗步数。

16位CMPAHR寄存器值=MEP步数<<8(高8位)。

图7-28 采用MEP的运行逻辑关系

为产生一个给定频率与极性的HRPWM波形,与对于需要配置寄存器TBM、CCM和AQM。这与产生常规PWM波形一样。HRPWM与这些寄存器配合,扩展边沿分辨率并作相应的配置。尽管有多种可能的编程组合,但是只需要其中很少且实用的组合。

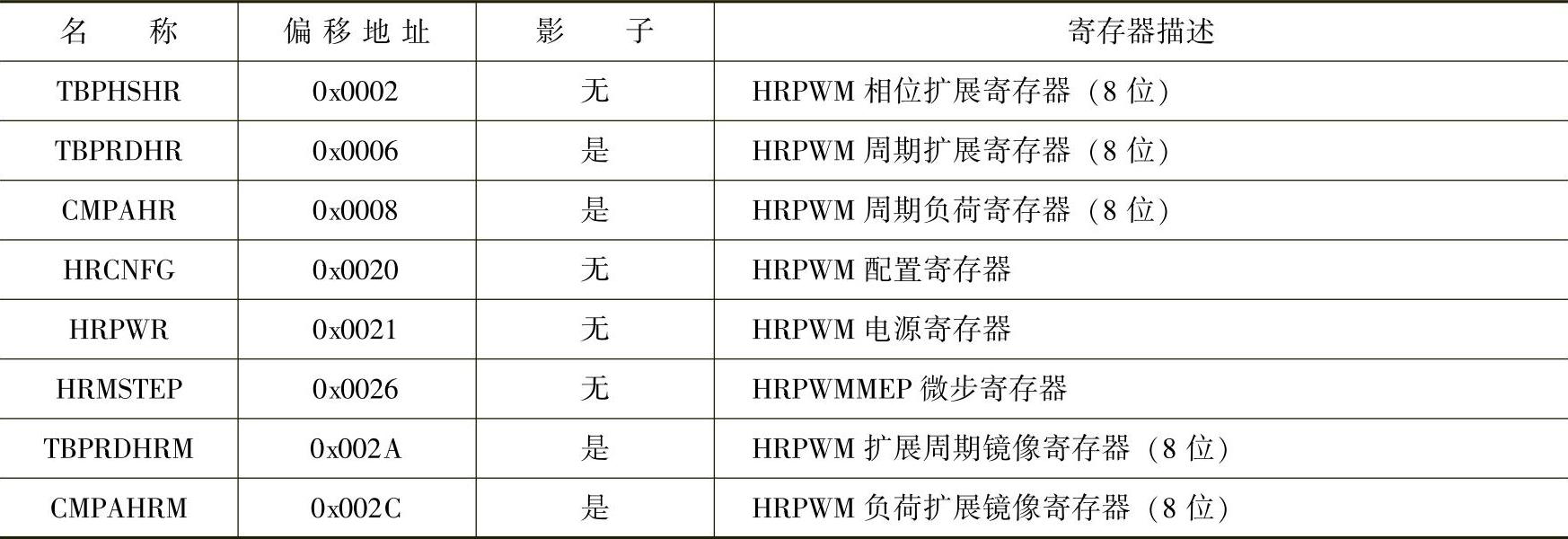

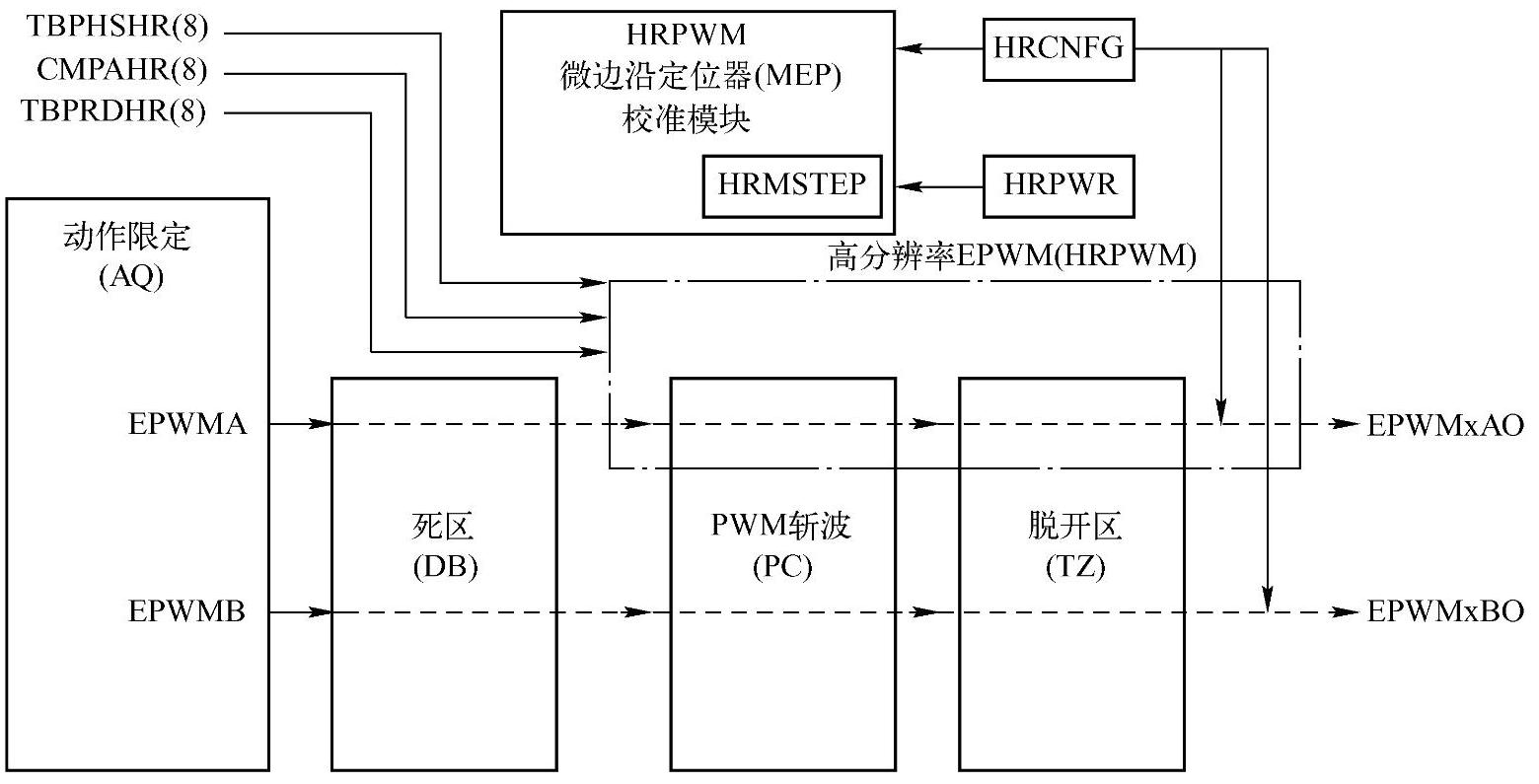

HRPWM的运行由表7-10所示的寄存器控制与监测。

表7-10 HRPWM模块的寄存器

(1)控制HRPWM能力

HRPWM的微边沿定位器(MEP)能力由三个扩展寄存器扩展,它们都是8位宽度。这些HRPWM寄存器与16位寄存器TBPHS、TBPRD和CMPA联合一起控制PWM运行。

●TBPHSHR,时基相位高分辨率寄存器。

●CMPAHR,计数比较A高分辨率寄存器。

●TBPRDHR,时基周期高分辨率寄存器(某些器件可用)。

图7-29给出了HRPWM扩展寄存器与存储器配置。图中上标带A的寄存器有镜像,能写到两个不同的存储器单元(镜像寄存器带有后缀“M”,例如CMPA镜像即CMPAM)。读高分辨率镜像寄存器会有不确定的值。另外,TBPRDHR和TBPRD只有在镜像地址可以按32位值写入,不是所有器件都有这两个寄存器。

图7-29 HRPWM扩展寄存器与存储器配置

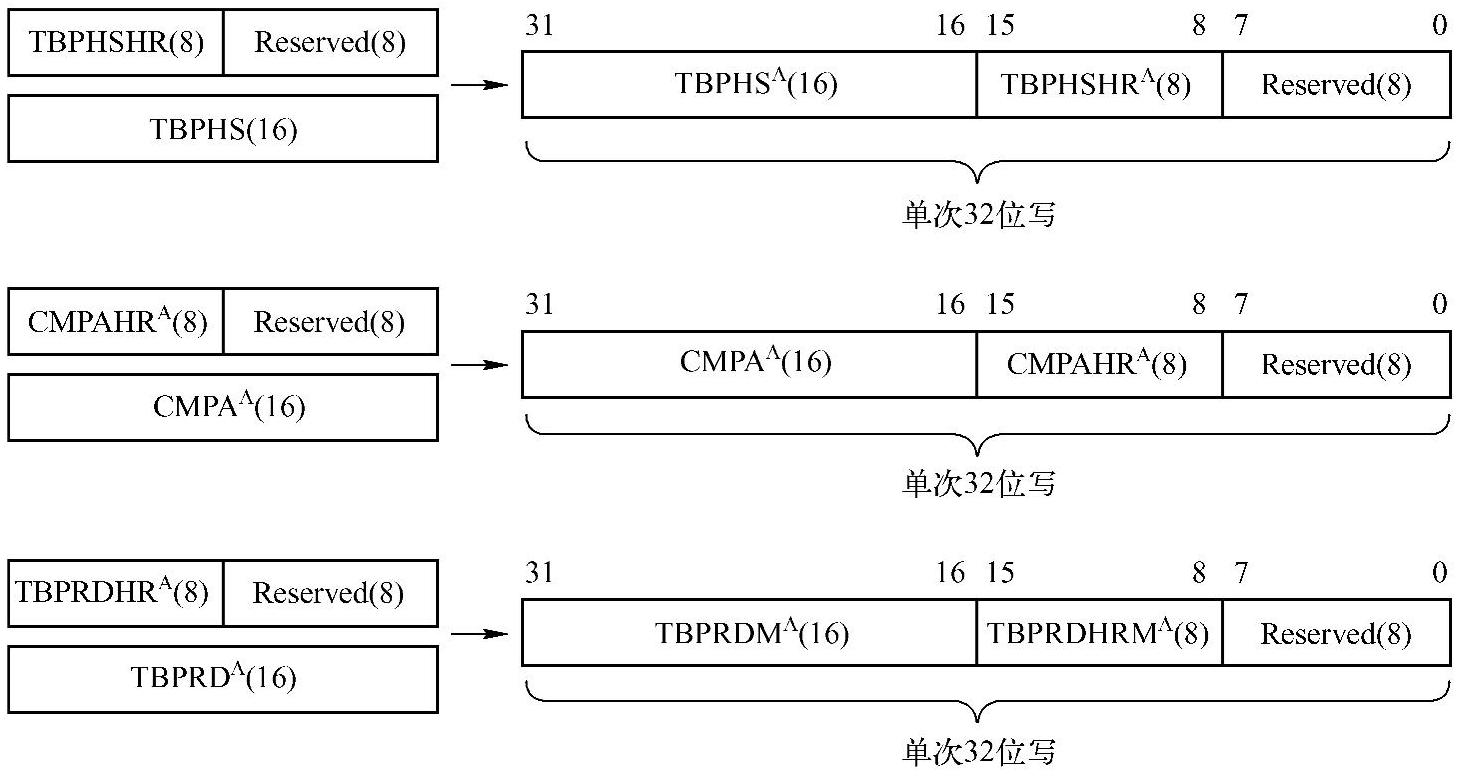

采用通道A的PWM信号通路控制HRPWM能力。通过合适配置HRCNFG寄存器,可以在通道B的PWM信号通路支持HRPWM。图7-30给出了HRPWM模块框图,其中的寄存器TBPHSHR、TBPRDHR来自于时基子模块,寄存器CMPAHR来自于计数比较子模块。

图7-30 HRPWM模块框图

(2)配置HRPWM

一旦ePWM对于一个给定的频率与极性配置为提供常规PWM,HRPWM就可以通过编程HRCNFG寄存器进行配置。该寄存器有如下配置选择:

1)边沿模式。可以编程MEP以提供上升沿(RE)、下降沿(FE)或同时双沿(BE)的精密的位置控制。FE与RE用于需要占空比控制(CMPA高分辨率控制)的功率拓扑电路,而BE用于需要相位偏移控制的功率拓扑电路,例如相移全桥(TBPHS或TBPRD高分辨率控制)。

2)控制模式。MEP编程控制既可以采用CMPAHR寄存器(占空比控制),也可以采用TBPHSHR寄存器(相位控制)。RE或FE控制模式应与CMPAHR寄存器一起使用。BE控制模式应与TBPHSHR寄存器一起使用。当MEP由TBPRDHR寄存器(周期)控制时,占空比与相位也可以通过其相应的高分辨率寄存器控制。

3)影子模式。该模式与常规PWM模式提供一样的影子(双缓冲)选择。只有通过CMPAHR与TBPRDHR寄存器运行,这种选择才有效,而且应当与CMPA寄存器常规装入选择相同。若选择TBPHSHR,那么该选项无效。

4)高分辨率B信号控制。ePWM通道的B信号通路可以产生一个高分辨率输出,该输出可以是交换A、B输出(高分辨率信号出现在ePWMxB而不是ePWMxA),或者在eP-WMxB引脚输出高分辨率ePWMxA信号的反相信号。

5)自动转换模式。该模式只与定标系数优化软件联合使用。对于类型1的HRPWM模块,如果使能自动转换模式,CMPAHR=取小数(PWM占空比∗PWM周期)<<8。定标系数优化软件通过背景代码计算定标系数MEP,并用每粗步的MEP计算步数自动更新HRM-STEP寄存器。MEP校准模块将使用寄存器HRMSTEP、CMPAHR的值,自动计算由小数占空比表示的合适的MEP步数,并按此移动高分辨率ePWM信号边沿。如果自动转换被禁止,CMPAHR寄存器就像一个类型0的HRPWM模块,且CMPAHR=(取小数(PWM占空比∗PWM周期)∗MEP定标系数+0.5)<<8)。此模式所有的这些计算需要由用户代码完成,并忽略HRMSTEP寄存器。高分辨率周期自动转换与高分辨率占空比的自动转换有相同的行为。对于高分辨率周期模式,自动转换必须总是使能。

(3)HRPWM运行原理

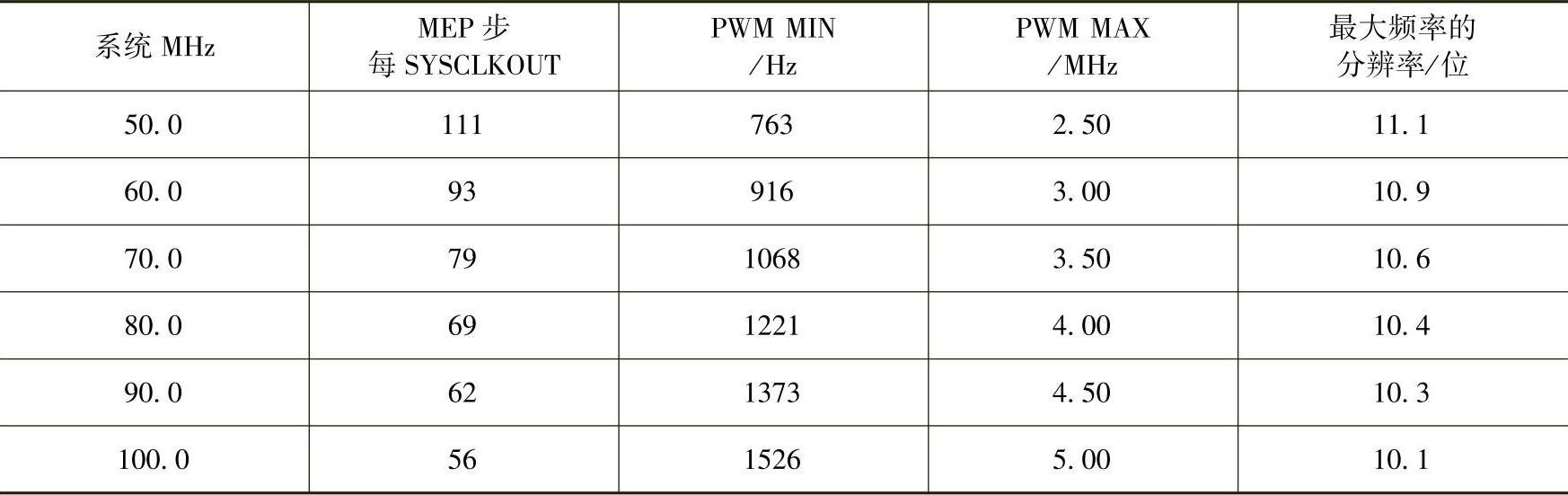

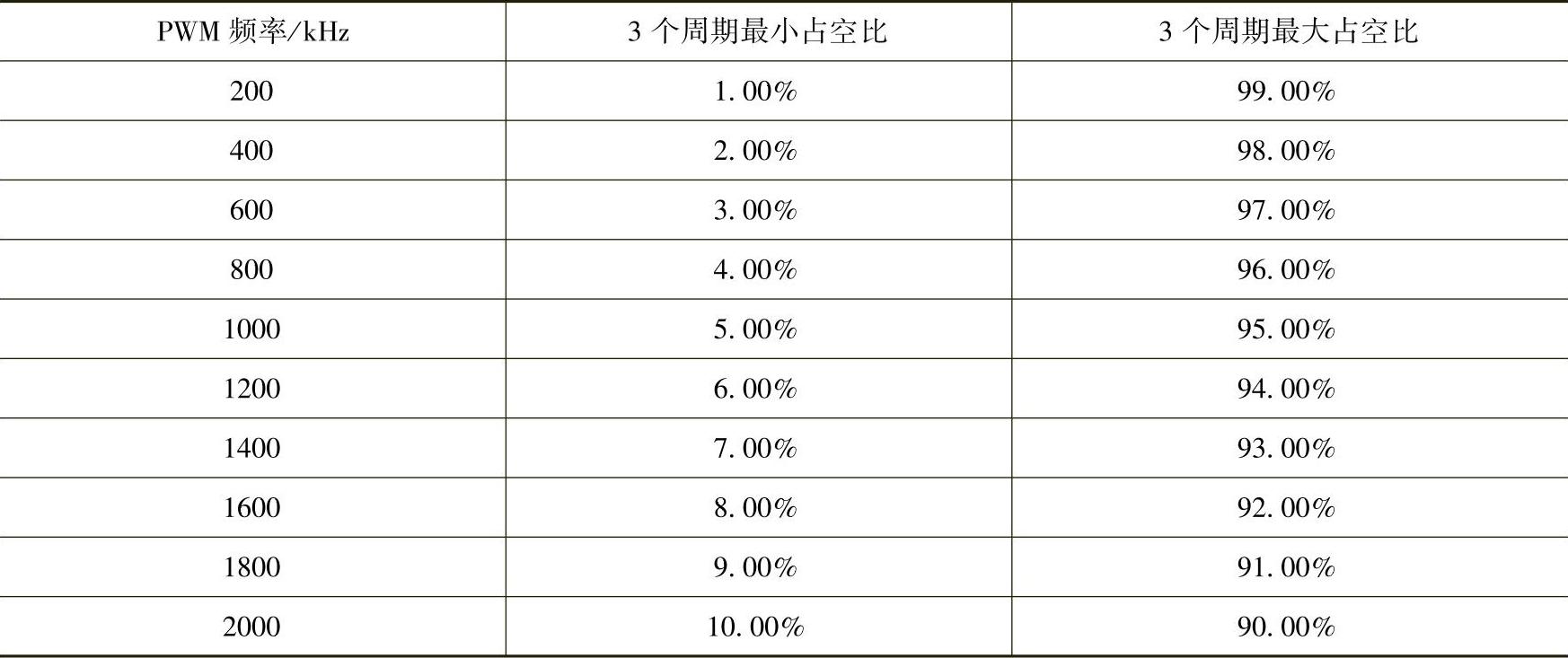

MEP逻辑能够在255(8位)个离散时间步之一设置边沿。MEP配合TBM、CCM寄存器,以保证应用最优的时间步而且在宽范围的PWM频率、系统时钟频率及其他运行条件下保持边沿设置精度。表7-11给出了HRPWM支持的运行频率的典型范围。

表7-11 MEP步、PWM频率与分辨率的关系

对表7-11有以下说明。

●系统频率为SYSCLKOUT即CPU时钟。TBCLK=SYSCLKOUT。

●数据以180ps的MEP时间分辨率为基础,具体器件对MEP的限制需要查手册。

●本例MEP步为TSYSCLKOUT/180ps。

●PWM最小频率基于最大周期值,即TBPRD=65535。PWM模式为非对称增计数。

●对于最大PWM频率给出以位表示的分辨率。

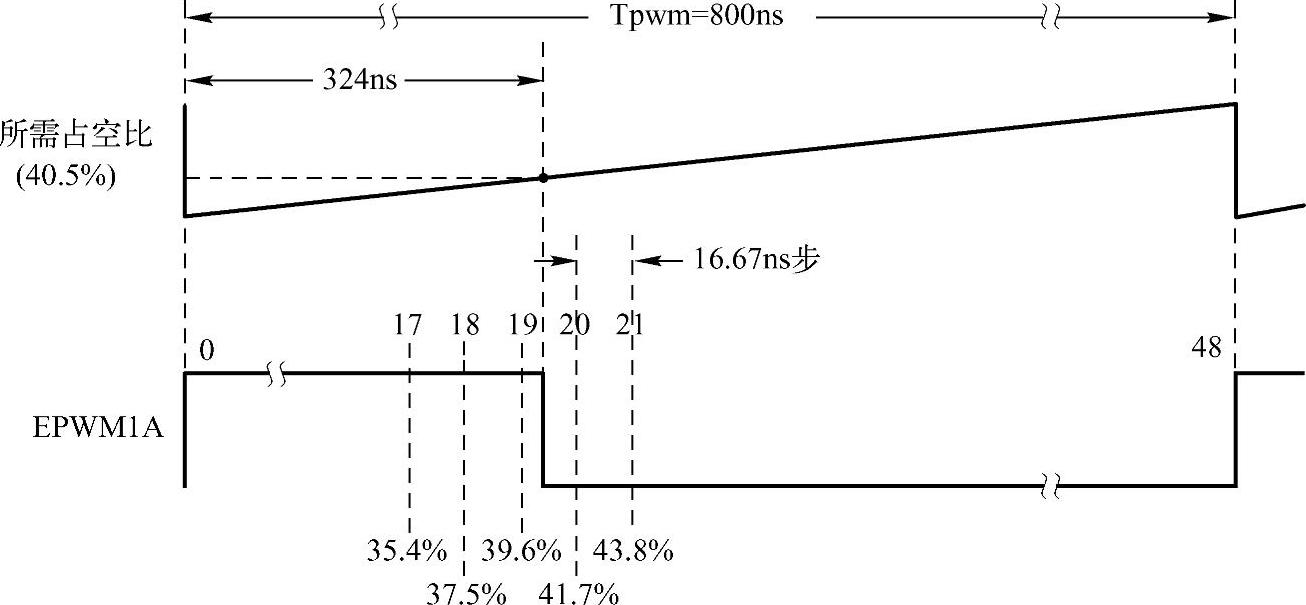

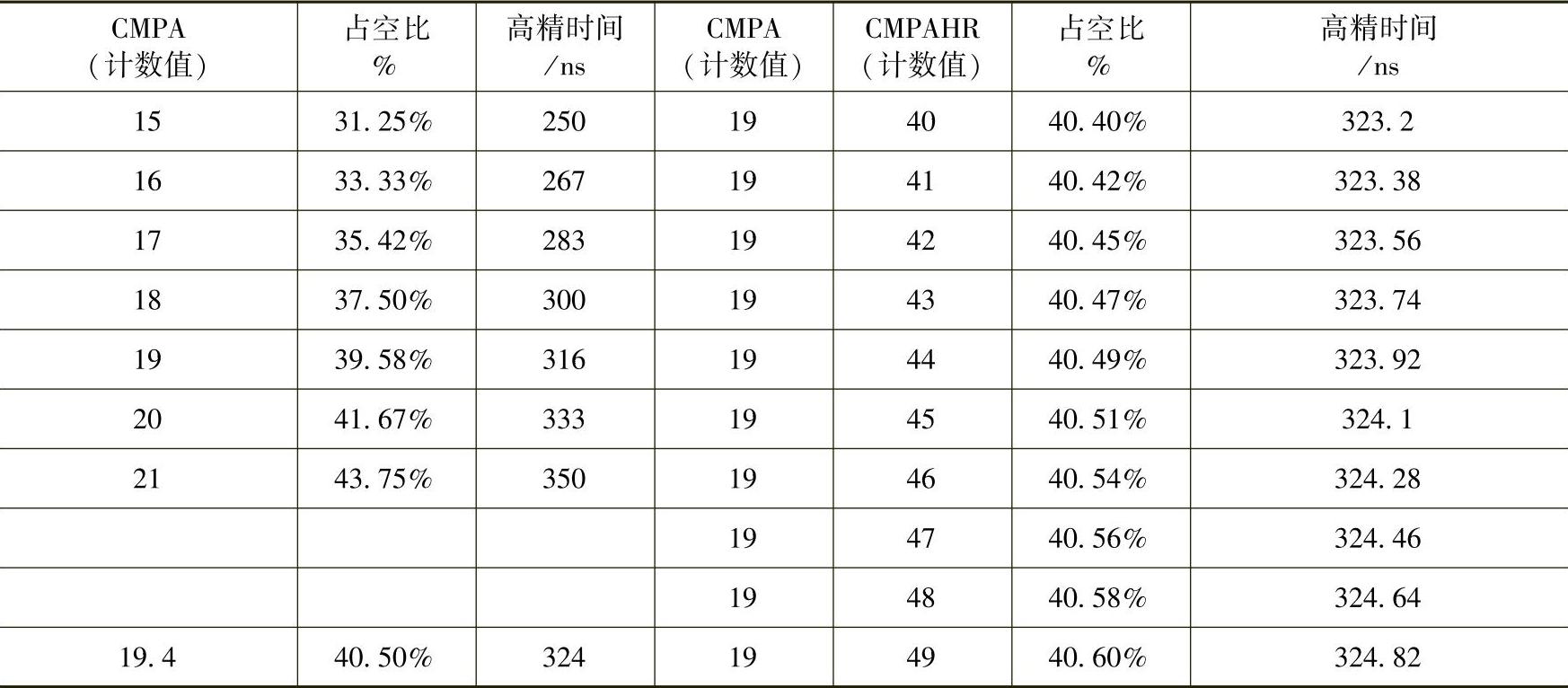

1)边沿定位。在一个典型的功率控制循环中,例如,开关模式数字电机控制(DMC)、不间断电源(UPS)、数字控制器(PID,2极点/2零点,滞后/超前)等,通常以单位制或百分制发出一个占空比命令。假设在某一个运行点,要求的占空比为0.405或40.5%,需要的逆变器PWM频率为1.25MHz。在系统时钟为60MHz的常规PWM发生系统中,选择的占空比在40.5%附近。图7-6是占空比为40.5%需要的PWM波形图。图中,计数比较值19(即占空比39.6%)是可以获得的最接近40.5%的数值。这相当于316.7ns的边沿位置,而不是希望的324ns。数据如图7-31所示。

通过应用MEP,可以获得更接近324ns理想点的边沿位置。见表7-12,除了CMPA值外,MEP值44步(CMPAHR寄存器)将边沿定位在323.92ns,几乎为零误差。本例假定MEP具有180ps的步分辨率。

图7-31 占空比为40.5%需要的PWM波形

表7-12 CMPA与占空比(左)及[CMPA:CMPAHR]与占空比(右)的关系

表7-12中,采用的系统时钟SYSCLKOUT和TBCLK为60MHz,16.67ns。对于PWM周期寄存器的计数值48,PWM周期=48∗16.67ns=800ns,PWM频率=1/800ns=1.25MHz。假定MEP大小为180ps,具体器件的MEP典型与最大值可参照英文手册。

2)定标考虑。前面已说明了采用标准CMPA和MEP(CMPAHR)寄存器资源在时间上精密定位边沿的机制。然而在实际应用中,有必要无缝地提供从标幺(小数)占空比到最终的整数(非小数)表示的映射函数,该整数要写到[CMPA:CMPAHR]寄存器组合。下面只从标幺占空比的角度描述该映射。

为此,首先检查涉及的定标或映射步。控制软件通常用标幺值或百分值表示占空比。这样具有不需要关心最终的绝对占空比(以时钟计数或以ns表示的高分辨率时间表示)而完成所需的数学计算的优点。而且,也使得代码便于移植到运行于不同PWM频率的多种逆变器类型。

为实现映射方案,需要一个两步的定标过程。

下面以实例说明。

本例假定,系统时钟SYSCLKOUT=16.7ns(60MHz),PWM频率=1.25MHz(1/800ns),要求的PWM占空比PWMDuty=0.405(40.5%)。

以粗步表示的PWM周期PWMperiod(800ns/16.67ns)=48。

若MEP大小为180ps,每一个粗步的MEP步数(16.67ns/180ps)=93。

MEP_ScaleFactor=0.5(0.080h,Q8格式),保持1~255范围的CMPAHR和小数圆整常数(默认值)。在取小数(PWMDuty∗PWMperiod)∗MEP_ScaleFactor,得到数值的小数部分≥0.5时,该圆整常数将圆整CMPAHR值到1MEP步。

第1步:用于CMPA寄存器的百分比整数占空比值转换。

CMPA寄存器值=int(PWMDuty∗PWMperiod),int表示取整数部分

=int(0.405∗48)=19(13h)。

第2步:用于CMPAHR寄存器的百分比小数部分转换。

CMPAHR寄存器值=(frac(PWMDuty∗PWMperiod)∗MEP_ScaleFactor+0.5)<<8,frac表示取小数部分。

CMPAHR寄存器值=(frac(19.4)∗93+0.5<<8,数值移位到CMPAHR高字节

=((0.4∗93+0.5)<<8)=(37.2+0.5)<<8

=37.7∗256,左移8位相当于乘以256=9651=25B3h,硬件忽略低8位。

说明:

如果AUTOCONV位(HRCNFG.6)置1且MEP_ScaleFactor在HRMSTEP寄存器,那么CMPAHR寄存器值=取小数PWMDuty∗PWMperiod<<8。其他的转换运算由硬件自动完成,且正确的MEP定标信号边沿出现在ePWM通道输出。如果AUTOCONV位未置1,上述运算必须由软件完成。

MEP定标系数(MEP_ScaleFactor)随系统时钟与DSP运行条件变化。TI提供MEP定标系数优化(SFO)软件C函数,它采用HRPWM内建的诊断功能对于给定的运行点返回最佳的定标系数。定标系数在一定范围变化缓慢,这样优化(SFO)C函数可以在背景循环中缓慢运行。

CMPA和CMPAHR寄存器配置在存储器,这样28x CPU的32位数据能力可以作为一个联合数值即[CMPA:CMPAHR]写入。TBPRDM与TBPRDHRM(镜像)寄存器也相似地配置在存储器。

映射方案已经由C或汇编代码实现,本节中随后的实例由C或汇编代码实现了上述方案。实例代码采用了28x系列32位CPU的优点。对于时间要求严格(Tme critical)的控制环,建议采用汇编语言。它是一个采用Q15占空比值作为输入并写入单一[CMPA:CM⁃PAHR]值的周期优化函数(11个SYSCLKOUT周期)。

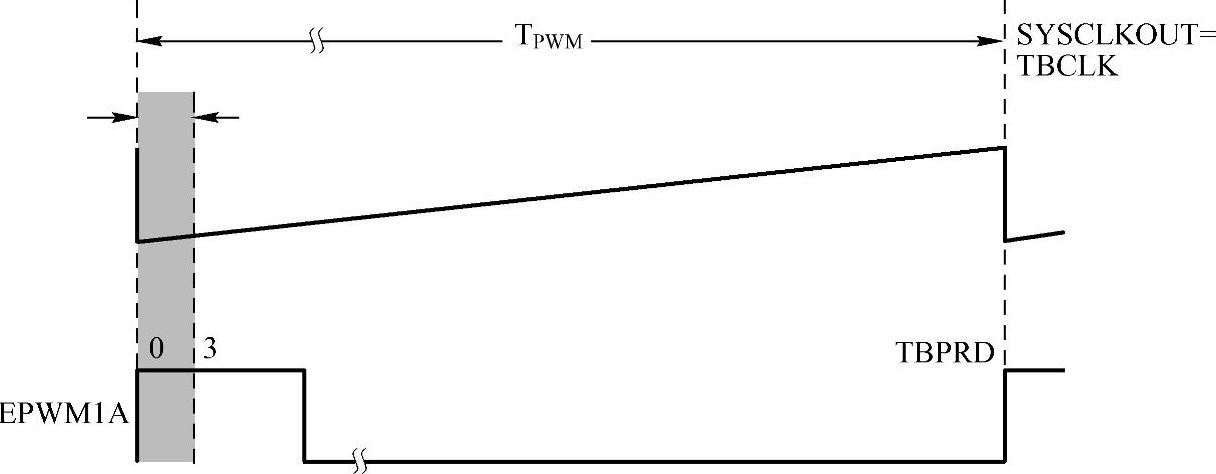

3)占空比范围限制。在高分辨率模式,MEP不在100%的PWM周期内有效,是可选的。

●当高分辨率周期(TBPRDHR)控制不使能周期开始后3个SYSCLK周期。

●当高分辨率周期(TBPRDHR)控制通过HRPCTL寄存器使能时:

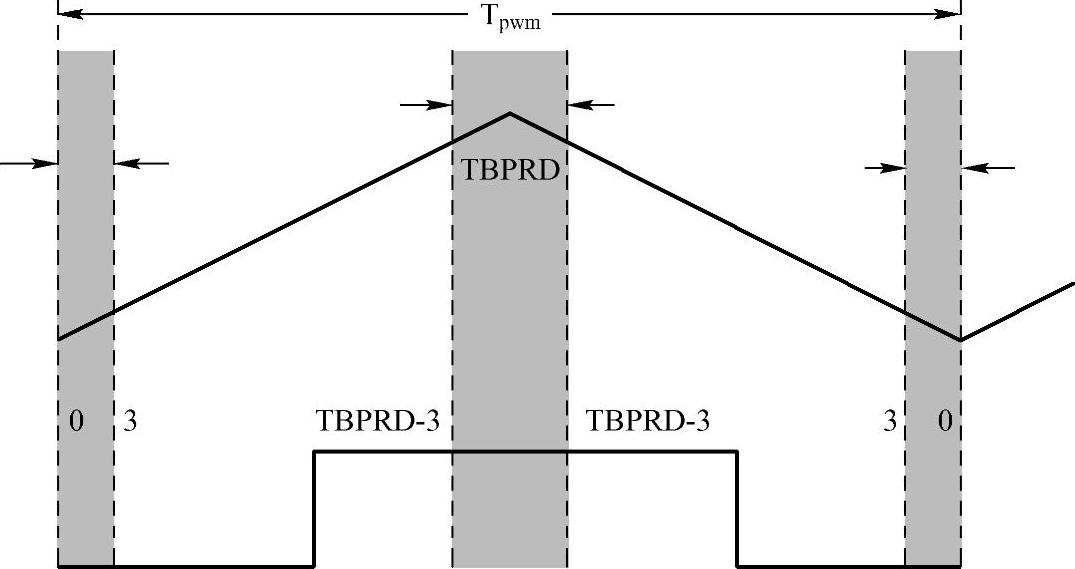

对于增计数模式,周期开始后3个SYSCLK周期直到周期结束前的3个SYSCLK周期。

对于减计数模式,增计数时,CTR=0后3个周期直到CTR=PRD的3个周期,减计数时,CTR=PRD后的3个周期直到CTR=0前的3个周期。

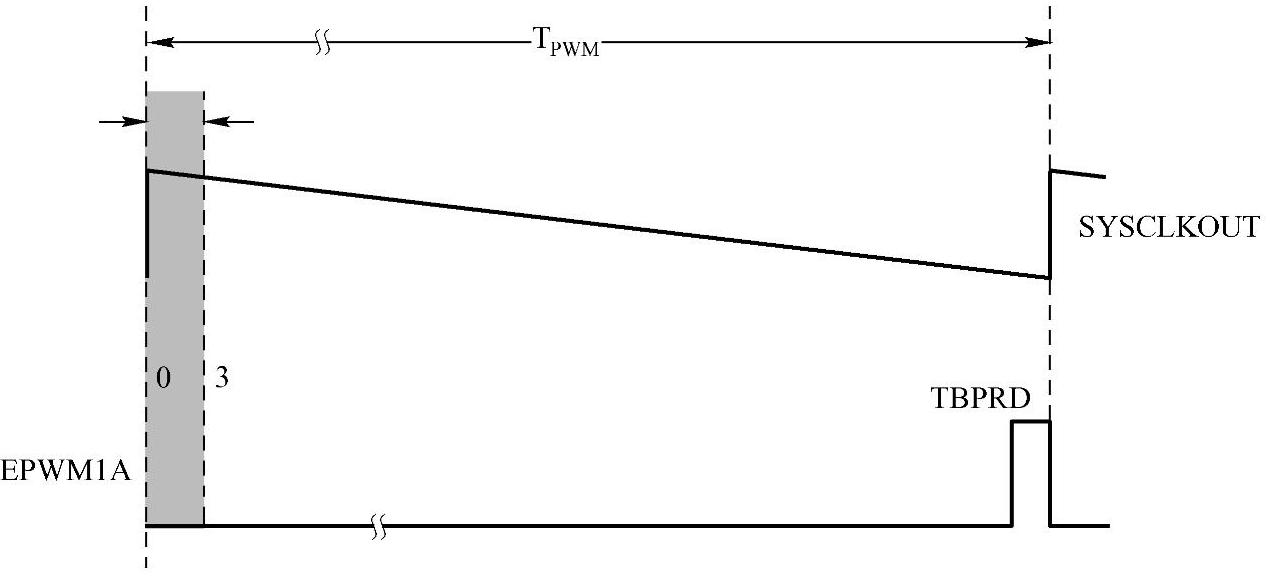

占空比范围限制示于图7-32~图7-35。该限制在MEP上施加了占空比限制。例如,精密边沿控制并非是一直到0%的占空比都可用。当高分辨率控制禁止时,尽管头3个周期,HRPWM能力不可用,但是通常PWM占空比控制仍然是完全可以向下运行到0%的占空比。在大部分情况下,这不是问题,因为控制器的调节点通常不会设计到接近0%的占空比。为更好地理解可用的占空比范围,可以参见表7-13。当高分辨率周期控制使能时(HRPCTL[HRPE]=1),占空比不能落到受限范围,否则,在ePWMxA输出会有未定义的行为情况。

图7-32 低占空比范围限制示例(HRPCTL[HRPE]=0)

表7-13 3个SYSCLK/TBCLK周期占空比范围限制

(https://www.daowen.com)

(https://www.daowen.com)

对于表7-13,系统时钟TBCLK=60MHz,系统时钟周期TSYSCLKOUT=16.67ns。只有高分辨率周期(TBPRDHR)控制使能时,才有周期最大占空比限制。

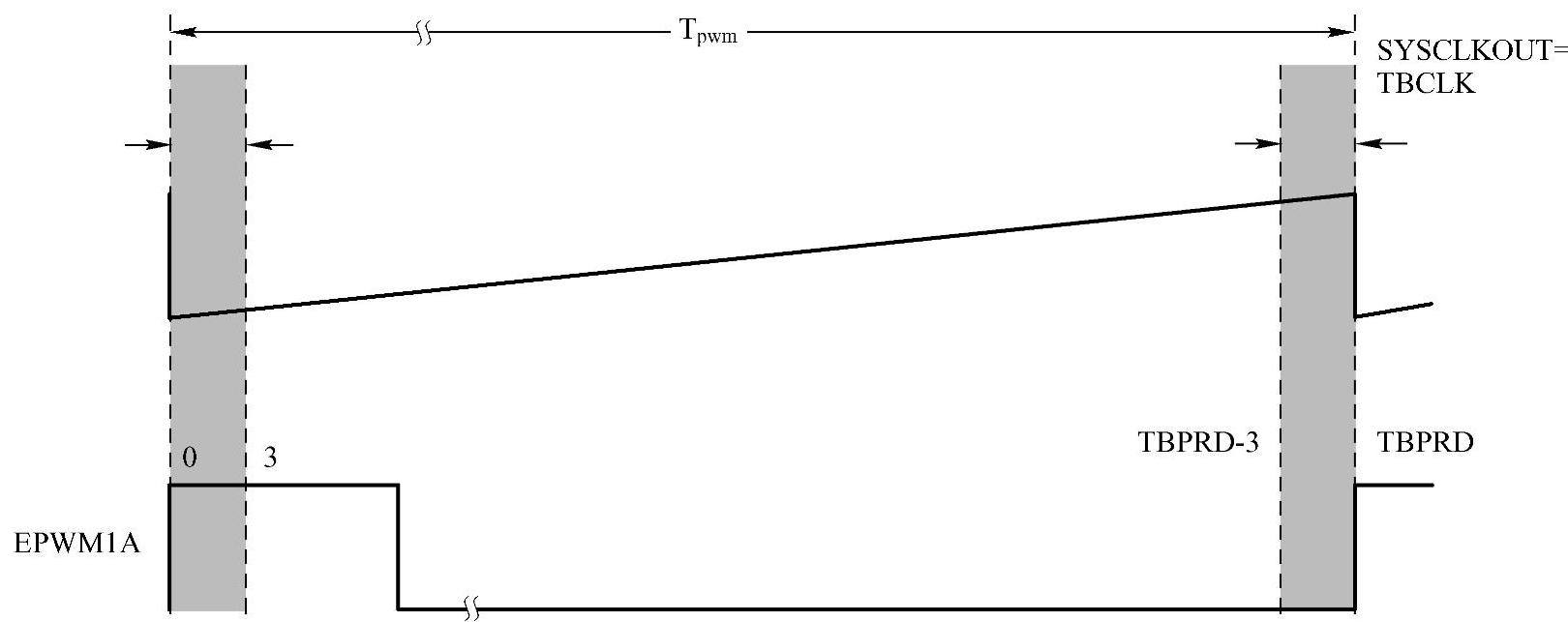

如果应用中需要HRPWM运行在低占空比区域,那么HRPWM可以配置在减计数模式,这时高分辨率周期禁止(HRPCTL[HRPE]=0),上升沿位置(REP)由MEP控制,如图7-33所示。这种情况下,低占空比限制不再是一个问题。然而,将会有一个具有同样百分比的最大占空比限制问题,见表7-13。

注意:当高分辨率周期控制使能时(HRPCTL[HRPE]=1),占空比不能落到受限范围,否则,在ePWMxA输出会有未定义的行为情况。

4)高分辨率周期。具有类型1的ePWM模块的器件支持通过TBPRDHR(M)寄存器支持采用MEP逻辑的高分辨率周期控制。

注意:当使能高分辨率周期控制时,ePWMxB输出在增计数模式具有±1个TBCLK周期抖动,而减计数模式具有±2个TBCLK周期抖动。

图7-33 高占空比范围限制示例(HRPCTL[HRPE]=0)

图7-34 增计数占空比范围限制示例(HRPCTL[HRPE]=1)

图7-35 减计数占空比范围限制示例(HRPCTL[HRPE]=1)

上述对于占空比的定标过程也可用于高分辨率周期。

本例假定:

系统时钟SYSCLKOUT =16.67ns(60MHz)

要求的PWM频率 =175kHz(周期342.857)

每一个180ps粗步的MEP步数 =93(16.67ns/180ps)

(MEP_ScaleFactor)

在1~255范围内保持的TBPRDHR =0.5(0080hQ8格式)

值和小数圆整常数(默认值)

问题:

在增计数模式:

若TBPRD=342,那么PWM频率 =174.93kHz(周期=(342+1)∗TTBCLK)

TBPRD=341,那么PWM频率 =175.44kHz(周期=(341+1)∗TTBCLK)

在减计数模式:

若TBPRD=172,那么PWM频率=174.42kHz(周期=(172∗2)∗TTBCLK)

TBPRD=171,那么PWM频率=175.44kHz(周期=(171∗2)∗TTBCLK)

解决方案:

每一个180ps粗步有93个MEP步:

第一步:TBPRD寄存器的百分比整数周期值

整数周期值 =342∗TTBCLK

=int(342.857)∗TTBCLK

=int(PWMperiod)∗TTBCLK

在增计数模式:

TBPRD寄存器值 =341(TBPRD=周期值-1)

=0155h

在减计数模式:

TBPRD寄存器值 =171(TBPRD=周期值/2)

=00ABh

第一步:TBPRD寄存器的百分比小数值

TBPRDHR寄存器值 =(frac(PWMperiod)∗MEP_ScaleFactor+0.5)

(移位TBPRDHR高字节)

如果使能自动转换且HRMSTEP=

MEP_ScaleFactor值(93) :=frac(PWMperiod)<<8

TBPRDHR寄存器值=frac(342.857)<<8

=0.857×256

=DB00h

自动转换将自动完成计算 =((TBPRDHR(15:0)>>8)×HRMSTEP+80h)>>8

这样TBPRDHRMEP延迟

由硬件定标:

=(00DBh×93+80h)>>8

=(500Fh)>>8

周期MEP延迟=0050hMEP步

对高分辨率周期进行如下配置。

为使用高分辨率周期,ePWMx模块应当按下述严格顺序初始化:

①使能ePWMx时钟。

②禁止TBCLKSYNC。

③配置ePWMx寄存器AQ、TBPRD、CC等。

●ePWMx可以配置为增计数或减计数模式。高分辨率周期不兼容减计数模式。

●TBCLK必须等于SYSCLKOUT。

●TBPRD与CC寄存器必须配置影子装入。

●CMPCTL[LOADAMODE]。

●增计数模式:CMPCTL[LOADAMODE]=1(在CTR=PRD时装入)。

在减计数模式:CMPCTL[LOADAMODE]=2(在CTR=0或CTR=PRD时装入)。

④配置HRPWM寄存器:

●HRCNFG[HRLOAD]=2(在CTR=0或CTR=PRD时装入)。

●HRCNFG[AUTOCONV]=1(使能自动转换)。

●HRCNFG[EDGMODE]=3(双沿MEP控制)。

⑤对于TBPHS:TBPHSHR用高分辨率周期同步,设置HRPCTL[TBPSHRLOADE]=1和TBCTL[PHSEN]=1。在减计数模式不论TBPHSHR的内容,这两位都设为1。

⑥使能高分辨率周期控制(HRPCTL[HRPE]=1)。

⑦使能TBCLKSYNC。

⑧TBCTL[SWFSYNC]=1。

⑨由于自动使能自动转换,HRMSTEP必须包含一个精确的MEP定标系数(每一个SYSCLKOUT粗步的MEP步数)。MEP定标系数能通过SFO()函数获得。

⑩为控制高分辨率周期,写入TBPRDHR(M)寄存器。

注意:当使能高分辨率周期时,一个EPWMxSYNC脉冲会为PWM引入±1~2个周期的抖动(增计数模式下±1周期,减计数模式下±2周期)。因此,TBCTL[SYNCOSEL]不应设为1(CTR=0是EPWMxSYNCO的源)或2(CTR=CMPB是EPWMxSYNCO的源)。不然,抖动会随同步脉冲发生在每一个PWM周期。

当TBCTL[SYNCOSEL]=0(EPWMxSYNCI是EPWMxSYNCO的源),一个软件同步脉冲将在高分辨率周期初始化时只产生一次。在PWM运行时,如果施加一个软件同步脉冲,在有同步脉冲时PWM输出将会出现抖动。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。