5.1.6 存储器的接口设计

2025年09月21日

5.1.6 存储器的接口设计

存储器的接口设计主要应考虑的问题包括存储器容量、存储空间的安排、总线上的存储器存取信号及时序、数据总线宽度等。

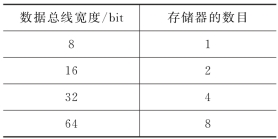

①存储器是按字节编址的。存储器的数目要依赖于数据总线的宽度,如表5.5所示。

表5.5 存储器的数目与数据总线宽度的关系

②存储区域的安排与具体CPU有关,具体如下。

a.8086存储器的高端:上电初始化程序,应放ROM。

b.8086存储器的低端:中断处理程序入口地址表,应放ROM。

c.其他部分:RAM或ROM。

d.MC 68000存储器0地址:上电初始化程序,应放ROM;接着是异常处理程序入口地址表,应放RAM。

所以,不同存储芯片要根据CPU安排在适当的区域。

③芯片的地址分配是通过地址译码实现的。这与芯片的内地址单元数和数据总线宽度有关。如选中芯片的内部存储单元数是N,数据总线宽度M=4字节,则

存储器的基地址=L·N·M, L=0,1,2,…

这一原则同样适合于I/O寄存器的地址安排。

④地址译码可采用全译码(唯一的地址空间,可充分利用空间,但译码器复杂)、部分译码(空间不唯一,占用空间大,译码简单,用于小系统)或者“选线”法(无须译码,占用空间大;大部分空间不能有效使用,只用于小系统)。