8.2 例题详解

例8.1 对如图8.11所示的并行输出口,如何改进即可变成选通(带联络信号)输出口,且可用中断管理或DMA传输管理?

解

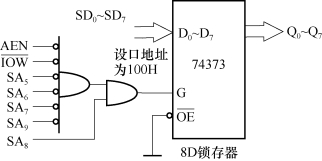

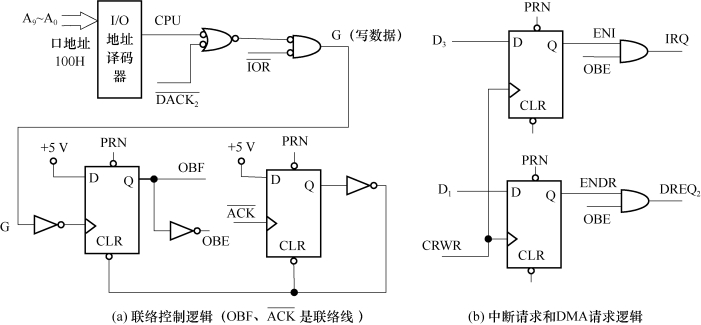

对图8.11所示的并行输出口,进行如图8.12所示电路的改进,即可变成选通输出口。

图8.11 简单8位并行输出口

图8.12 中断管理和DMA传输管理电路

其中,ENI和ENDR是命令寄存器的两位(D1与D3),当ENI=1时,允许中断;当ENDR=1时,为DMA请求。OBE为输出缓冲器空。CRWR是写命令信号,其产生方法和写数据信号G类似。IRQ是中断请求。DREQ2是DMA请求,它和![]() 属于同一DMA通道。

属于同一DMA通道。

思考:若想用查询管理,应加些什么?

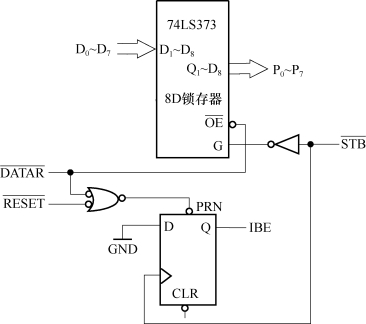

例8.2 设计一个CPU访问8255A并行接口的电路,其中,通道B是选通输出口,它同时也可以用DMA的通道3来访问。

解

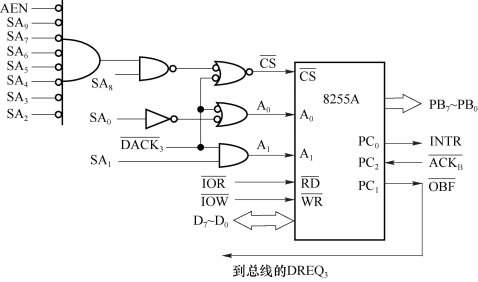

因为8255A有4个端口,所以假定其口地址是100H~103H。图8.13是CPU访问8255A的接口电路。

图8.13 CPU和DMAC都可访问8255A的接口电路

DMA通道3的请求信号是DREQ3,响应信号是![]() 。

。

8255A的基地址为100H,CPU访问时,A9~A2=01000000。以AEN=0为条件译码产生的信号和![]() 作“负或”后,作为8255A的片选信号

作“负或”后,作为8255A的片选信号![]() 。

。

在![]() 时,是DMA传输,这时8255A的A1 A0=01,选中8255A的B通道数据寄存器。这里MUX简化为一个与门和一个与非门。

时,是DMA传输,这时8255A的A1 A0=01,选中8255A的B通道数据寄存器。这里MUX简化为一个与门和一个与非门。

8255A的![]() ,表示B口输出数据寄存器空,请求下一次输出数据,可作为DMA传输请求。当CPU或DMAC把数据写入后,

,表示B口输出数据寄存器空,请求下一次输出数据,可作为DMA传输请求。当CPU或DMAC把数据写入后,![]() 变低(输出缓冲器满)。

变低(输出缓冲器满)。

注意

若这一接口电路的DMA传输不正确,很可能是![]() 对写数据操作的延时过大引起的,则应重新设计DREQ3逻辑,对

对写数据操作的延时过大引起的,则应重新设计DREQ3逻辑,对![]() 作简单处理,以使

作简单处理,以使![]() 和

和![]() 同时有效时,就立即撤销DREQ3。

同时有效时,就立即撤销DREQ3。

例8.3 若用8237实现存储器到存储器传送,要用它的通道0和1,问:具体用了通道0和1的哪些资源?怎样启动传送的开始?若要实现存储器“块填充”,即在一个存储区域填入固定数据,应如何实现?

解

8237的存储器到存储器传送要用通道0和1。

对于通道0,用了它的DREQ软件请求,以启动传输开始。启动地址寄存器、现行地址寄存器。地址生成方式:可以是递增/递减或者固定不变。

对于通道1,用了它的起始地址寄存器、现行地址寄存器。地址生成方式:可以是递增/递减。还要用该通道的块长寄存器(即块计数器)。

存储器到存储器传送是由通道0的DREQ置1来启动的。启动后,按块方式连续传送。每次传送时,读源口(通道0指向的存储器口),把读出的数据放到TEMP寄存器,尔后,写目的口(通道1指向的存储器口),通道1的块计数器减1,若不为0,继续传送。每次传送后,源口地址按约定递增/递减或不变,目的地址按约定递增或递减。

若通道0的地址生成方式设为“固定不变”,则可以实现“块填充”操作,使整个目的块填入同一字符(源块的第一个字符)。

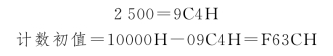

例8.4 某计数器电路有16位二进制增计数器,分别是CL(计数器高字节)和CH(计数器低字节)。若FOSC=10MHz,要产生2kHz的方波,求计数初值K。

解

要产生2kHz的方波,必须产生4kHz的频率,再经2分频。

![]()

例8.5 某一具有预标器的24位二进制计数器,其预标器可实现4分频、16分频、32分频、64分频,其内部时钟频率是24 MHz,问要产生32 ms的计时间隔,计数器初值应是多少?

解

因为内部时钟周期为![]() ,若预标器为1分频,预标器计数值为K,有

,若预标器为1分频,预标器计数值为K,有

若用4分频预标值,则K=192 000;若用16分频预标值,则K=48 000;若用32分频预标值,则K=24 000;若用64分频预标值,则K=12 000。若计数器是增计数器,则:初值=计数模值-计数值。若计数器是减计数器,则:初值=计数值。

用计算结果就可以对计数器进行初始化了。

例8.6 8253/8254没有输入捕获功能,但8253/8254具有内部软件捕获功能,即用软件指令可以把某通道的计数器当前值记忆在当前值寄存器内,供CPU读出。问这种机制是如何实现的?这一功能在什么时候解除?

解

8253/8254计数器中每个通道都有一个16位的当前计数值锁存器,它可以锁存减1计数器的内容,以供读出和查询。由于减1计数器的内容是随输入时钟在不断改变的,为了捕获减1计数器的当前值,只有先把它送到当前计数值锁存器,然后才可用指令读出当前值。

实现的办法是:首先按照工作方式字的格式写入锁存命令,即在命令字中D5 D4=00为锁存,D7 D6为选择要锁存的计数通道;然后用IN指令读所选择的计数器数据口即可。

这一功能在下一次写入工作方式字后即解除。

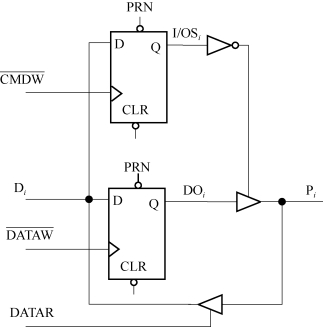

例8.7 位控I/O接口的基本结构如图8.14所示。其中:触发器I/OSi是输入/输出选择位,1为输入,0为输出;触发器DOi是数据输出寄存器的第i位;![]() 是命令寄存器写信号;

是命令寄存器写信号;![]() 是数据寄存器写命令;DATAR是读数据口命令。如何把它变成“字节I/O口”?

是数据寄存器写命令;DATAR是读数据口命令。如何把它变成“字节I/O口”?

图8.14 位控I/O基本电路

解

若要把它变成“字节I/O口”,只需要一位I/O选择控制,如图8.14中的I/OSi信号,控制整个I/O口所有口线(例如8位或16位)的输入/输出即可。

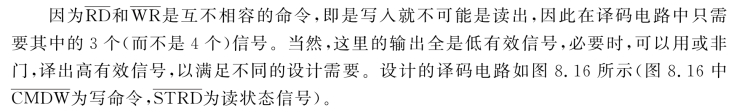

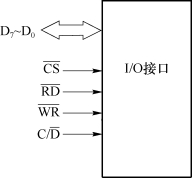

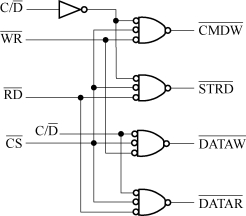

例8.8 有一个I/O接口,其接口信号如图8.15所示,其操作真值表如表8.1所示。试设计其内部命令译码电路。

表8.1 操作真值表

解

图8.15 I/O接口电路对外信号

图8.16 I/O接口译码电路

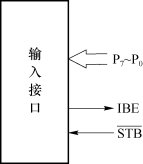

例8.9 若某选通输入接口如图8.17所示,其联络信号是:输入联络是![]() ,输出联络是IBE(In Buffer Empty)。试设计该输入接口电路。

,输出联络是IBE(In Buffer Empty)。试设计该输入接口电路。

图8.17 输入接口对外信号

解

根据所给的联络信号,设计的带联络信号的输入接口电路如图8.18所示。该电路是一种混合联络的联络逻辑。IBE是电平信号,高电平相当于“I/O READY”,可以接收下一个输入数据。![]() 是负脉冲信号,低电平相当于输入数据有效。该电路只用于速度较低的外设和高速数据总线。若不符合这一前提,则可能出现传输错误。(读者可以思考这一问题,并找出解决办法。这就是设计严谨性的问题,即某些不完善的设计看似可行,在某些条件下也可正确工作,但换一种条件,它就不能正常工作。)

是负脉冲信号,低电平相当于输入数据有效。该电路只用于速度较低的外设和高速数据总线。若不符合这一前提,则可能出现传输错误。(读者可以思考这一问题,并找出解决办法。这就是设计严谨性的问题,即某些不完善的设计看似可行,在某些条件下也可正确工作,但换一种条件,它就不能正常工作。)

图8.18 带联络信号的输入接口电路

例8.10 说明8250的波特率产生机制。

解

8250的波特率产生机制如图8.19所示。

![]()

图8.19 8250波特率产生机制图

其中,分频比由分频比锁存器的初值确定。

例8.11 说明8250可以控制的参数。

解

8250可以控制如下参数:

·字长和停止位位数;

·有无奇偶校验,以及有奇偶校验时,是奇校验还是偶校验,或者固定奇偶位(1或者0);

·波特率;

·可发送和检测BREAK序列;

·可设置本地环回测试;

·可设置查询管理或者中断管理;

·用中断管理时,可产生发送中断、接收中断、异常接收条件中断、外部(MODEM)中断(共有4种中断源)。每一中断源都可单独控制。

例8.12 说明8250中每一中断源的标志位和它们的置位与复位条件。

解

8250共有4种中断源,每一中断源的情况如下。

(1)发送中断THRE

置位条件:当数据从发送保持寄存器(THR)传送到发送移位寄存器(TSR)时。复位条件:写一个数据到发送保持寄存器后。

(2)接收中断DR

置位条件:正确接收一个数据并将其放入接收数据寄存器后。复位条件:从接收数据寄存器读出数据后。

(3)异常接收条件中断

①BI。置位:在检测到BREAK序列时。复位:接收数据线恢复到常态(高电平)且读LSR之后。

②OE。置位:在接收数据准备就绪DR=1,且又一个接收数据被装入时。复位:读LSR之后。

③PE。置位:在接收的P位与收校验产生的P位不符时。复位:读LSR之后。

④FE。置位:在没有接收到正确的停止位时。复位:读LSR之后。

(4)MODEM中断

①CTS。置位:CTS线发生了变化。复位:读MSR之后。

②DSR。置位:DSR线发生了变化。复位:读MSR之后。

③RI。置位:RI线检测到一次振铃脉冲的后沿时。复位:读MSR之后。

④LSI。置位:接收数据线上信号消失时。复位:接收信号恢复正常且读MSR之后。

例8.13 在上电后,若8250开放了发送中断,它能否产生发送中断?为什么?

解

能,因为上电后,THRE状态的初态是1。

例8.14 8250在启动发送中断传送时,为什么发送中断可产生两次?

解

据8250发送中断的产生机制,其原因是发送保持寄存器空,即THRE状态是1。若开放发送中断,THRE=1,且TSRE=1,则:

·第一个数据写入THR后,THRE=0,即THR中有数据;

·因为TSRE=1,THR中的数据马上被装入TSR并开始发送,而THR立即变空,所以THRE又被置位,而产生发送中断。第二次中断几乎是随着数据的写入而立即产生的。

这是发送双缓冲(即有THR和TSR)的通信控制器所共有的特点。

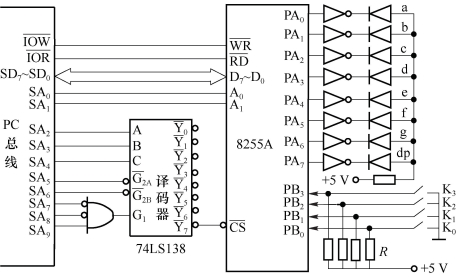

例8.15 并行接口8255A经常用来和LED显示器、键盘、打印机、A/D和D/A转换器接口。图8.20是8255A与七段代码显示器的接口电路。开关设置的二进制信息由8255A的B口输入,经程序转换为对应的七段LED的字形码(段选码)后,通过A口输出并由七段LED显示。试编制其控制程序。

图8.20 8255A与七段LED显示器的接口电路

解

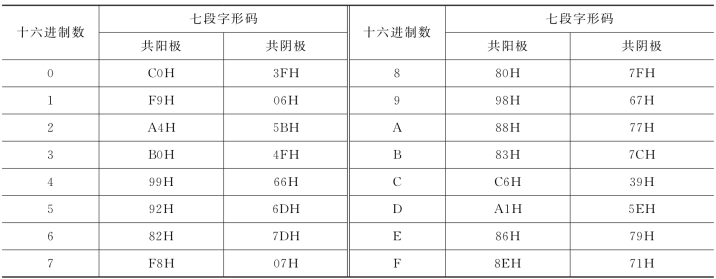

根据电路可知,8255A工作于方式0,B口工作于输入,A口工作于输出,不使用联络信号。8255A的工作方式字为1000×01×B(可设为82H)。

根据译码器可知,8255A的口地址为2ICH~2IFH。

根据电路可知,七段LED为共阳极电路,但B口输出的经反向器驱动后的字形码和共阴极的一样。七段16个(0~F)数字、字符的字形码表参看程序中SCODE定义的表。

编写控制程序的步骤如下:

·设置工作方式字;

·读B口状态,得到有关开关的信息;

·将得到的信息用查表法转换为七段字形码;

·七段字形码送A口至LED显示器显示;

·延时,使所显示的信息显示一段时间以便于观察。

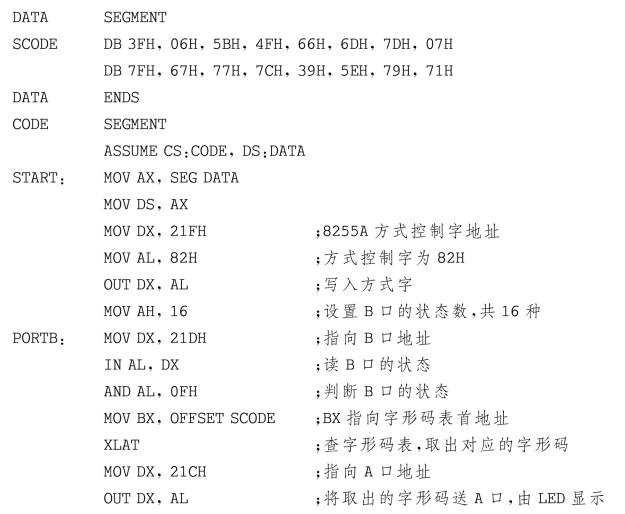

按题意编写的控制程序如下:

关于七段LED显示器的说明如下。

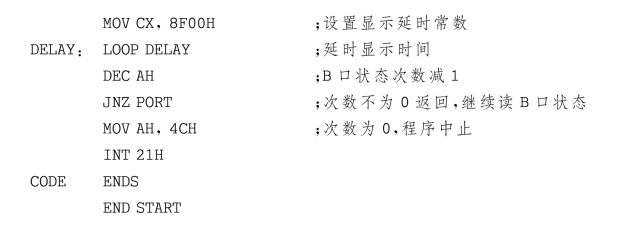

七段LED显示器由8个发光二极管构成,共有七段,构成显示的数字与字符。每段分别称为a、b、c、d、e、f、g。最高位dp表示显示圆点(·),如图8.21所示。

图8.21 七段LED显示器及其电路结构

根据其内部结构,LED显示器有共阴极电路和共阳极电路。该显示器可显示十六进制数字、部分英文字母及一些常用字符,其中十六进制数的七段字形码如表8.2所示。

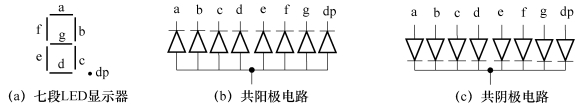

表8.2 十六进制数的七段字形码

注:不难看出,表中共阳极字形码与共阴极字形码互为反码。