★6.10.3 扩展外部存储器测试电路设计

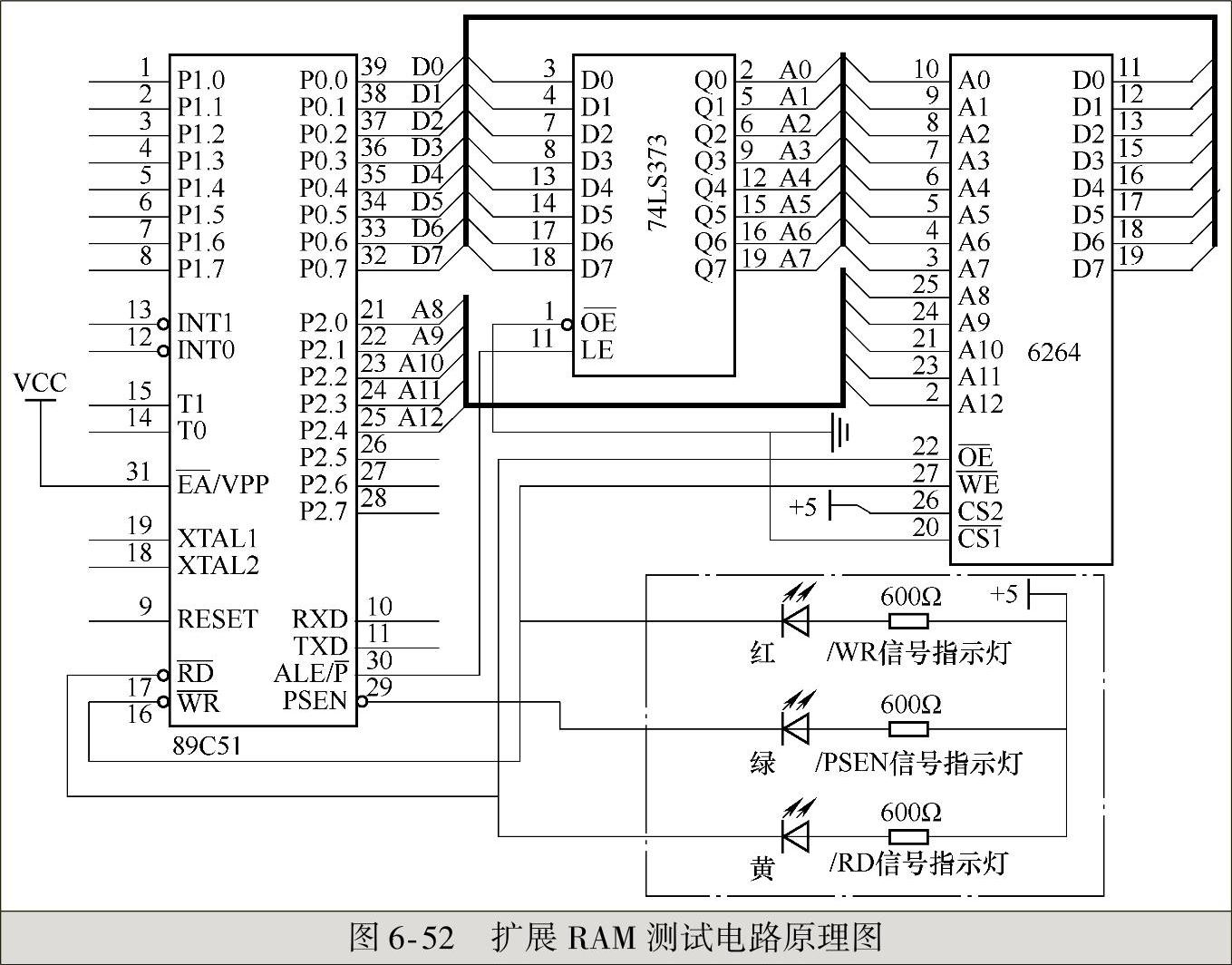

例6-12:如图6-52所示是扩展RAM测试电路原理图。与单片机 引脚相接的绿色LED灯为显示外ROM控制信号作用的指示灯;与单片机

引脚相接的绿色LED灯为显示外ROM控制信号作用的指示灯;与单片机 引脚相接的黄色LED灯为显示读取外RAM控制信号作用的指示灯;与单片机WR引脚相接的红色指示灯为显示写外RAM控制信号作用的指示灯。当所接控制信号有效(即为低电平)时对应指示灯发光。

引脚相接的黄色LED灯为显示读取外RAM控制信号作用的指示灯;与单片机WR引脚相接的红色指示灯为显示写外RAM控制信号作用的指示灯。当所接控制信号有效(即为低电平)时对应指示灯发光。

扩展一片外RAM的电路和程序设计基本方法:观察执行指令时控制信号 、

、 R的状态,时钟信号频率低,机器周期为1s。

R的状态,时钟信号频率低,机器周期为1s。

图6-52 扩展RAM测试电路原理图

如图6-52所示电路编制的简单演示程序如下:

ORG 0000H

MOV DPTR,#1000H;将外RAM地址送DPTR

MOV A,#68H

STAR:MOVX @DPTR,A;向外RAM写数, 红色指示灯亮

红色指示灯亮 黄色指示灯灭

黄色指示灯灭

MOVX A,@DPTR;从外RAM读数, 黄色指示灯亮WR红色指示灯灭

黄色指示灯亮WR红色指示灯灭

MOV 30H,A;读出的数送到内RAM地址30H单元因为是内RAM操作,所以 、

、 指示灯都

指示灯都

不亮;

LJMP STAR;返回循环

END

注意:由于复位之后,PC=0000H,故程序存储器第一条指令必须起始于0000H。若外部程序存储器起始于0000H,则单片机的引脚应接地,否则0000H指向内部程序存储器。

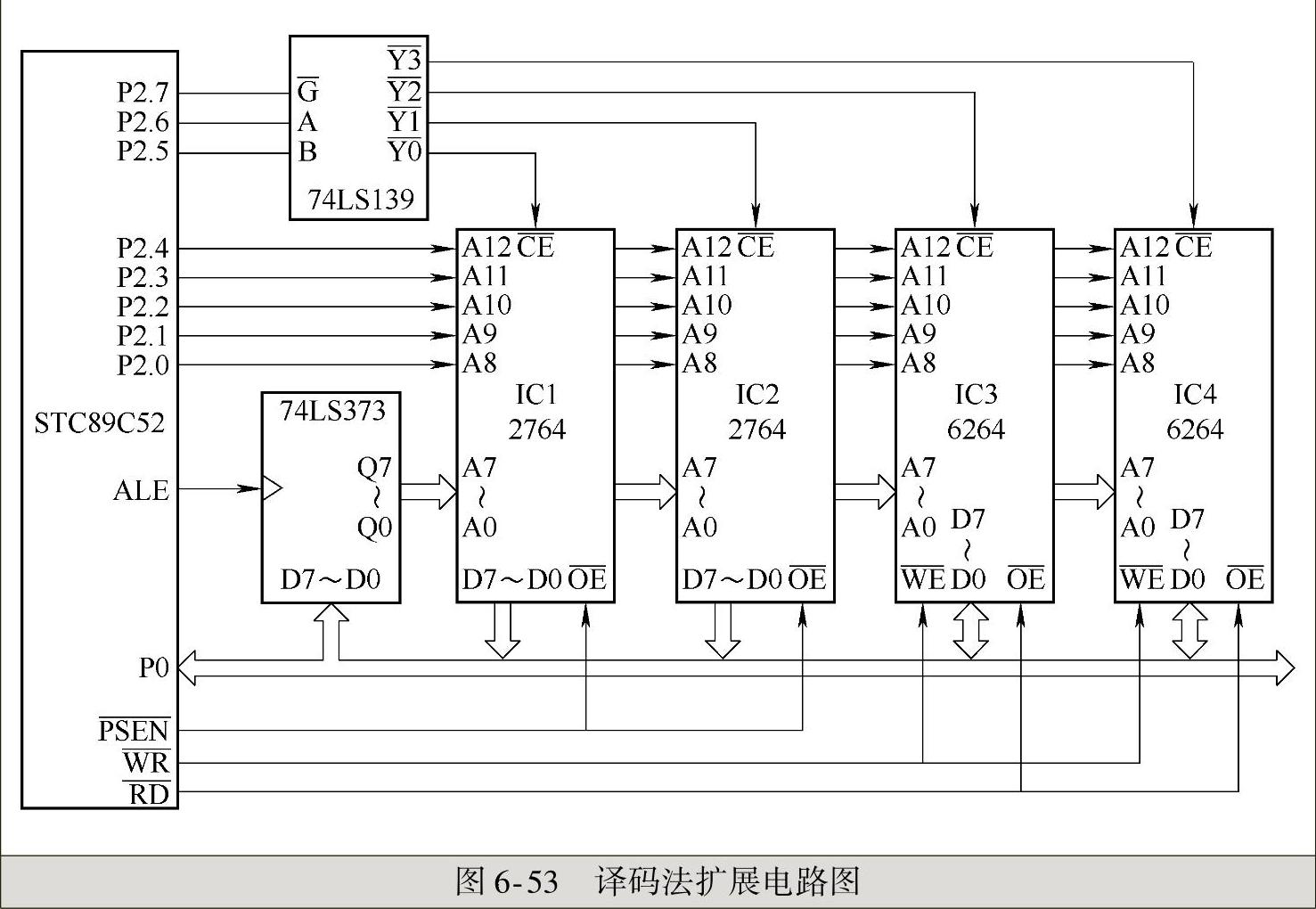

例6-13:用译码法扩展2片SRAM 6264和2片EPROM 2764。要求:①给出硬件接口电路;②确定各芯片的地址范围;③编写程序将片外程序存储器中以TAB为首地址的64个单元的内容依次传送到其中一片6264中。

2764和6264的容量均为8KB,片内地址线有13条。可将高位剩余的3条地址线接到74LS139译码器的3个输入端 、A、B,输出端

、A、B,输出端 ~

~ 分别连接4片芯片IC1、IC2、IC3、IC4的片选端。

分别连接4片芯片IC1、IC2、IC3、IC4的片选端。

1)扩展接口电路如图6-53所示。

图6-53 译码法扩展电路图

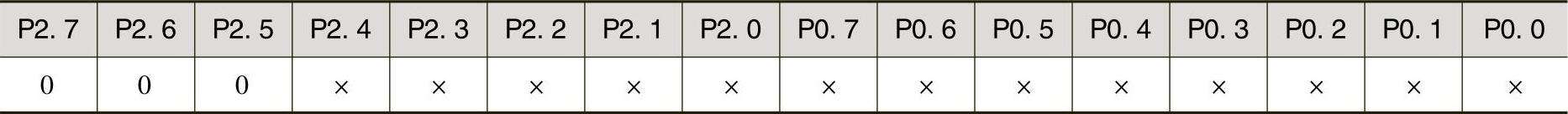

2)74LS139译码器要工作,使能端必须为0,因此P2.7=0。若此时P2.6=0、P2.5=0,选中IC1。地址线A15~A0与P2、P0对应关系如下:

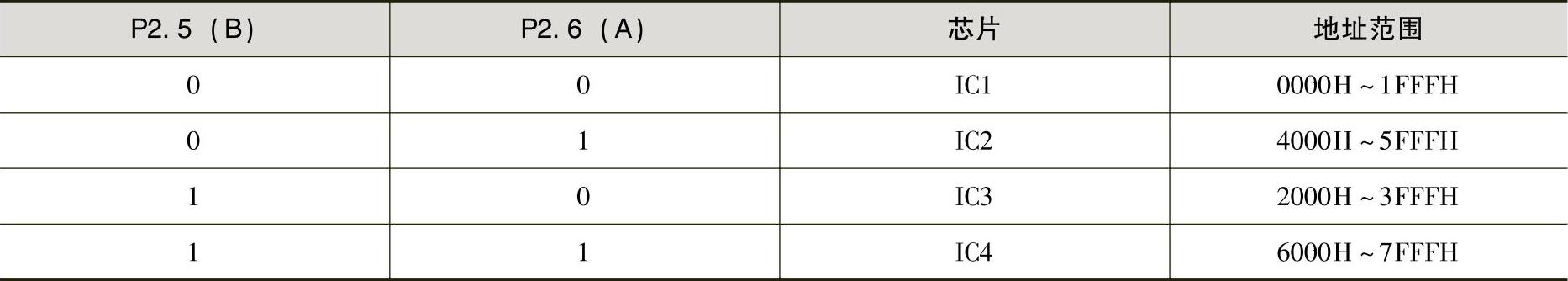

当P2.7、P2.6、P2.5全为0,P2.4~P2.0与P0.7~P0.0这13条地址线的任意状态都能选中IC1的某一单元。当“×”全为0时,则为最小地址0000H;当“×”全为1时,则为最大地址1FFFH。因此,IC1的地址空间为0000H~1FFFH。同理,可得其他芯片的地址范围。采用译码法4片芯片地址空间分布见表6-19。

表6-19 芯片地址空间分布(https://www.daowen.com)

3)要实现片外程序存储器中以TAB为首地址的64个单元的内容依次传送到片外RAM,可以采用循环程序,设置DPTR指向待传送的数据块的首地址#TAB,循环次数为64。设数据块传送到IC3中,参考程序如下:

MOV DPTR,#TAB;要传数据的首地址#TAB送入数据指针DPTR

MOV R0,#0;R0的初始值为0

MOV R3,#20H

MOV R2,#00H

AGIN:MOV A,R0

MOVC A,@A+DPTR;把以TAB为首地址的32个单元内容送入A

PUSH DPH

PUSH DPL

MOV DPL,R2

MOV DPH,R3

MOVX @DPTR,A;程序存储器中表的内容送入外部RAM单元

INC DPTR

MOV R2,DPL

MOV R3,DPH

POP DPL

POP DPH

INC R0;循环次数加1,也即外部RAM单元的地址指针加1

CJNE R0,#64,AGIN;判64个单元的数据是否已经传送完毕,未完则继续

HERE:SJMP HERE;原地跳转

TAB:DB …;外部程序存储器中要传送的64个单元的内容