四、P3口

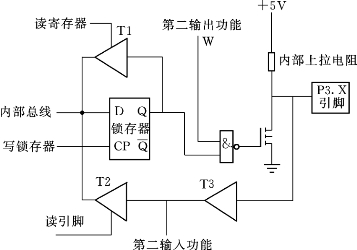

P3口的口线逻辑电路如图2-19所示。

图2-19 P3口某位结构

P3口的特点在于,为适应引脚信号第二功能的需要,增强了第二功能控制逻辑。对比P1口的结构图不难看出,P3口与P1口的差别在于多了“与非”门和缓冲器3。正是这两部分,使得P3口除了具有P1口的准双向I/O功能之外,还可以使用各引脚所具有的第二功能。“与非”门的作用实际上是一个开关,决定是输出锁存器Q端数据,还是输出第二功能(W)的信号。当W=1时,输出Q端信号;当Q=1时,可输出W线信号。编程时,不必事先由软件设置P3口为第一功能(通用I/O口)还是第二功能。当CPU对P3口进行SFR寻址(位或字节)访问时,由内部硬件自动将第二功能输出线W置“1”,这时,P3口为通用I/O口。当CPU不对P3口进行SFR寻址(位或字节)访问时,即用作第二功能输出/输入线时,由内部硬件使锁存器Q=1。

1.P3口用作通用I/O口

工作原理与P1口类似。当把P3口作为通用I/O口进行SFR寻址时,“第二输出功能端W”保持高电平,打开“与非”门,所以,D锁存器输出端Q的状态可通过“与非”门送至FET场效应管输出。这是用作通用I/O口输出的情况。

当P3口作为输入使用(即CPU读引脚状态)时,同P0~P2口一样,应由软件向口锁存器先写“1”,即使D锁存器Q端保持为“1”,“与非”门输出为“0”,FET场效应管截止,引脚端可作为高阻输入。当CPU发出读命令时,使缓冲器2上的“读引脚”信号有效,三态缓冲器2开通。于是引脚的状态经缓冲器3(常开)、缓冲器2送到CPU内部总线。

2.P3口用作第二功能

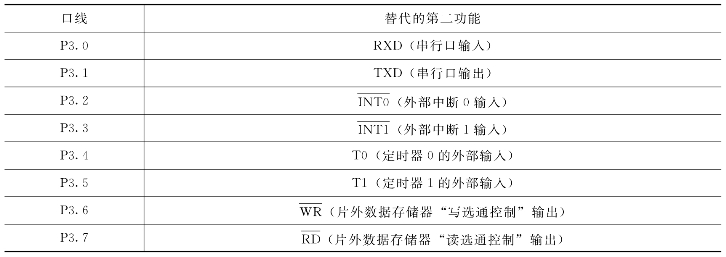

当端口用于第二功能时,八个引脚可按位独立定义,见表2-10。

表2-10 P3各口线与第二功能表

第二功能信号有输入和输出两类,以下分两种情况加以说明。

对于第二功能为输出的信号引脚,该位的D锁存器Q应被内部硬件自动置“1”,使“与非”门对“第二功能信号W”的输出是畅通的,从而实现第二功能信号的输出。“第二功能信号W”可为表2-11中的TXD、![]() 或

或![]() 这三个输出功能引脚。例如,P3.7位被选择为

这三个输出功能引脚。例如,P3.7位被选择为![]() 功能,则该位的W线上的

功能,则该位的W线上的![]() 控制信号状态通过“与非”门和FET输出到引脚端。

控制信号状态通过“与非”门和FET输出到引脚端。

对于第二功能为输入的信号引脚时,在口线的输入通路上增加了一个缓冲器3,输入的第二功能信号就从这个缓冲器的输出端取得,而输出电路中的D锁存器Q和第二功能输出信号线W都应该保持高电平。

可见,当MCS-51单片机执行输出操作时,CPU通过内部总线把数据写入锁存器,而执行输入(读端口)操作却有两种方式:当执行的是读锁存器指令时,CPU发出读锁存器信号,此时锁存器状态由D触发器的Q端经锁存器上面的三态输入缓冲器1(图2-16~图2-19)送入内部总线;如果执行的是读端口引脚指令,则CPU发出的是读引脚控制信号,直接读取端口引脚上的外部输入信息,此时引脚状态经三态输入缓冲器3送入内部总线。

在MCS-51单片机无片外扩展存储器的系统中,这四个端口都可以作为准双向通用I/O口使用。在具有片外扩展存储器的系统中,P0口为双向总线,分时输出低8位地址和输入/输出数据;P2口输出高8位地址。