扩展数据存储器

MCS-51单片机内部有128或256个字节的数据存储器,通常作为工作寄存器区、堆栈区、临时变量区,等等。如果系统要存储大量的数据,比如数据采集系统,那么片内的数据存储器就不够用了,需要进行扩展,最大可扩展到64K字节。

由于单片机是面向控制的,实际需要扩展容量不大,因此,一般采用静态RAM较方便,如6116(2K×8bit),6264(8K×8bit)。如有特殊需要,可选用62128(16K×8bit),62256(32K×8bit)等。与动态RAM相比,静态RAM无需考虑刷新电路,因此扩展电路较简单;但是,由于静态RAM是通过有源电路来保持存储器中的数据,因此要消耗较多的功率,价格也较高。

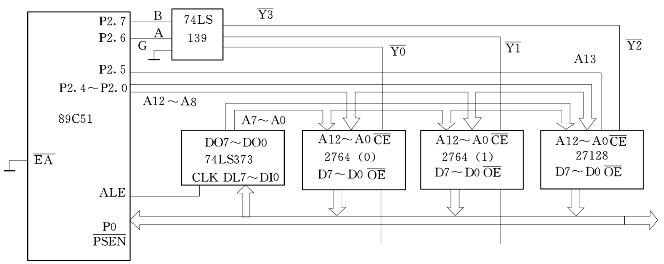

图6-2 2764/27128与单片机的连接

片外存储器,通常由半导体随机存取存储器RAM组成,也可用E2PROM芯片,其掉电后信息不丢失。串行E2PROM芯片引脚少(一般为8脚),系统扩展时占用MCU的I/O口线少,接口简单,故经常采用串行扩展方案。

并行扩展数据存储器包括读、写片外_RAM两种操作时序,但基本过程是相同的。这时所用的控制信号有ALE和![]() 在取指阶段,P0口和P2口用来传送ROM地址和指令,而在执行阶段,P0口和P2口用来传送片外RAM地址和读/写的数据。

在取指阶段,P0口和P2口用来传送ROM地址和指令,而在执行阶段,P0口和P2口用来传送片外RAM地址和读/写的数据。

89C51单片机若外扩RAM,则应将其![]() 引脚

引脚![]() 引脚连接。ALE信号连接至外部地址锁存器74LS373的CLK端,用以锁存P0口输出的低8位地址。

引脚连接。ALE信号连接至外部地址锁存器74LS373的CLK端,用以锁存P0口输出的低8位地址。

(一)访问片外数据存储器的操作指令

89C51单片机对片外数据存储器读、写操作的指令有如下两组:

MOVX A,@Ri ;片外RAM→(A)

MOVX@Ri,A ;(A)→片外RAM

这组指令因@Ri只能寻址8位地址,所以仅能访问256B的片外RAM。

MOVX A,@DPTR ;片外RAM→(A)

MOVX@DPTR,A ;(A)→片外RAM

这组指令因@DPTR能寻址16位地址,所以可访问64KB的片外RAM。

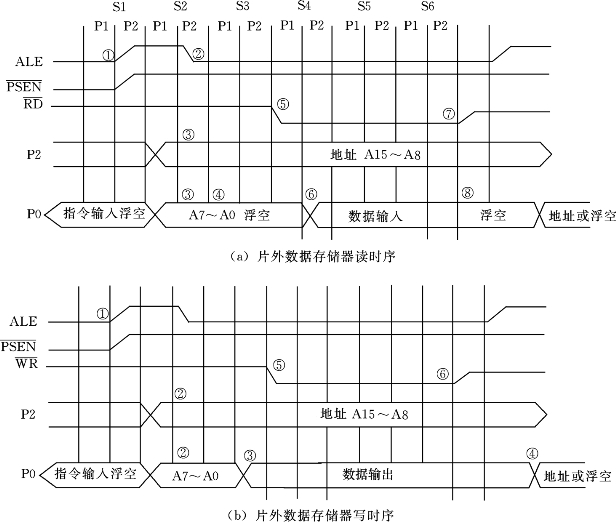

(二)MOVX A,@DPTR和MOVX@DPTR,A的操作时序

1.片外数据存储器的读操作时序

片外RAM的读操作时序如图6-3(a)所示。

在第一个机器周期的S1状态,ALE信号由低变高①,读RAM周期开始。

在S2状态,CPU把低8位地址送到P0口总线上,把高8位地址送上P2口(在执行“MOVX A,@DPTR”指令阶段时才送高8位;若是“MOVX A,@Ri”指令,则不送高8位)。ALE的下降沿②用来把低8位地址信息锁存到外部锁存器74LS373内③,而高8位地址信息一直锁存在P2口锁存器中。

在S3状态,P0口总线变成高阻悬浮状态④。

在S4状态,![]() 信号变为有效⑤(是在执行“MOVX A,@DPTR”后使

信号变为有效⑤(是在执行“MOVX A,@DPTR”后使![]() 信号有效),

信号有效),![]() 信号使得被寻址的片外RAM略过片刻后把数据送上P0口总线⑥,当

信号使得被寻址的片外RAM略过片刻后把数据送上P0口总线⑥,当![]() 回到高电平后⑦,P0总线变为悬浮状态。至此,读片外RAM周期结束。

回到高电平后⑦,P0总线变为悬浮状态。至此,读片外RAM周期结束。

2.片外数据存储器的写操作时序

向片外RAM写(存)数据,是89C51执行“MOVX@DPTR,A”指令后产生的动作。这条指令执行后,在89C51的![]() 信号的有效电平,此信号使RAM的

信号的有效电平,此信号使RAM的![]() 端被选通。

端被选通。

片外RAM的写操作时序如图6-3(b)所示。

图6-3 89C51访问片外数据存储器的操作时序

开始的过程与读过程类似,但写的过程是CPU主动把数据送上P0口总线,故在时序上,CPU先向P0总线上送完低8位地址后,在S3状态就将数据送到P0总线③。此间,P0总线上不会出现高阻悬浮现象。

在S4状态,写控制信号![]() 有效,选通片外RAM,稍过片刻,P0上的数据就写到RAM内了。

有效,选通片外RAM,稍过片刻,P0上的数据就写到RAM内了。

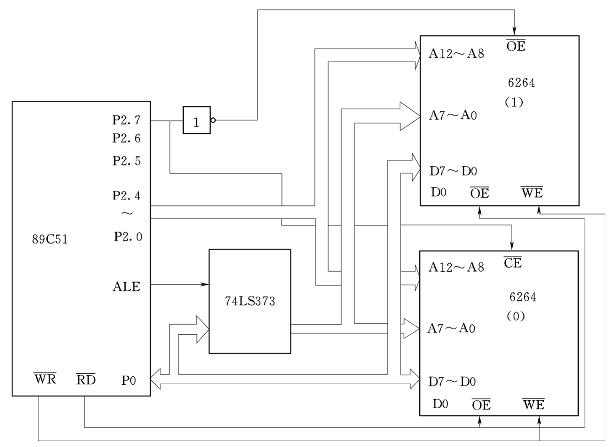

(三)数据存储器扩展实例

如图6-4所示的是用两片6264扩展16K×8位片外数据存储器的电路,采用线选法(P2.7)来寻址:当P2.7=0时,访问6264(0)片;当P2.7=1时,访问6264(1)片。图中未使用P2.6与P2.5两位地址线,故该两位可取任意值。6264(0)片的地址范围是:0××0000000000000~0××1111111111111B(0000~1FFFH,或2000~3FFFH,或4000~5FFFH,或6000~7FFFH),6264片(1)的地址范围是:1××0000000000000~1××1111111111111B(8000~9FFFH,或A000~BFFFH,或C000~DFFFH,或E000~FFFFH)。

图6-4 16K字节片外数据存储器扩展电路