基本RS触发器

2026年01月15日

一、基本RS触发器

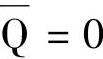

基本RS触发器是构成各种触发器的基本电路,它有“与非”型和“或非”型两种。图8-1a所示为与非型基本RS触发器逻辑电路。它是由两个与非门交叉耦合构成的。触发器的两个互补输出端用Q和 代表,R、S为输入端。当Q=0、

代表,R、S为输入端。当Q=0、 时,触发器为“0”状态,简称触发器置“0”;当Q=1、

时,触发器为“0”状态,简称触发器置“0”;当Q=1、 时,触发器为“1”状态,简称触发器置“1”。在正逻辑中,“1”代表高电平,“0”代表低电平。

时,触发器为“1”状态,简称触发器置“1”。在正逻辑中,“1”代表高电平,“0”代表低电平。

图8-1 与非型基本RS触发器

a)逻辑电路 b)逻辑符号

该触发器的工作原理如下:

1)当R=0、S=1时,因G1门有0输入,则其输出端 ;G2门为全1输入,其输出端Q=0,此时触发器被置“0”。R端称置0端,这是触发器的置0功能。

;G2门为全1输入,其输出端Q=0,此时触发器被置“0”。R端称置0端,这是触发器的置0功能。

2)当R=1、S=0时,G2门有0输入,其输出端Q=1,G1门为全1输入,其输出端 ,此时触发器被置“1”。S端称置1端,这是触发器的置1功能。

,此时触发器被置“1”。S端称置1端,这是触发器的置1功能。

3)当R=1、S=1时,设触发器初始状态为“1”态,此时G1门全1输入, ;G2门因有0输入而使Q=1,触发器仍为“1”态;如设触发器初始状态为“0”态,则此时G2门全1输入,Q=0;G1门因有0输入,使

;G2门因有0输入而使Q=1,触发器仍为“1”态;如设触发器初始状态为“0”态,则此时G2门全1输入,Q=0;G1门因有0输入,使 ,触发器仍为“0”态。即当R=1、S=1时,触发器保持原有状态不变。这是触发器的保持功能,即记忆功能。

,触发器仍为“0”态。即当R=1、S=1时,触发器保持原有状态不变。这是触发器的保持功能,即记忆功能。

4)当R=0、S=0时,G1、G2两门均有0输入,使Q=1、 ,这就破坏了触发器的逻辑关系,在R、S信号撤除后,触发器的状态很难确定。所以,R、S均为0的输入方式要避免,这是基本RS触发器的约束条件。(https://www.daowen.com)

,这就破坏了触发器的逻辑关系,在R、S信号撤除后,触发器的状态很难确定。所以,R、S均为0的输入方式要避免,这是基本RS触发器的约束条件。(https://www.daowen.com)

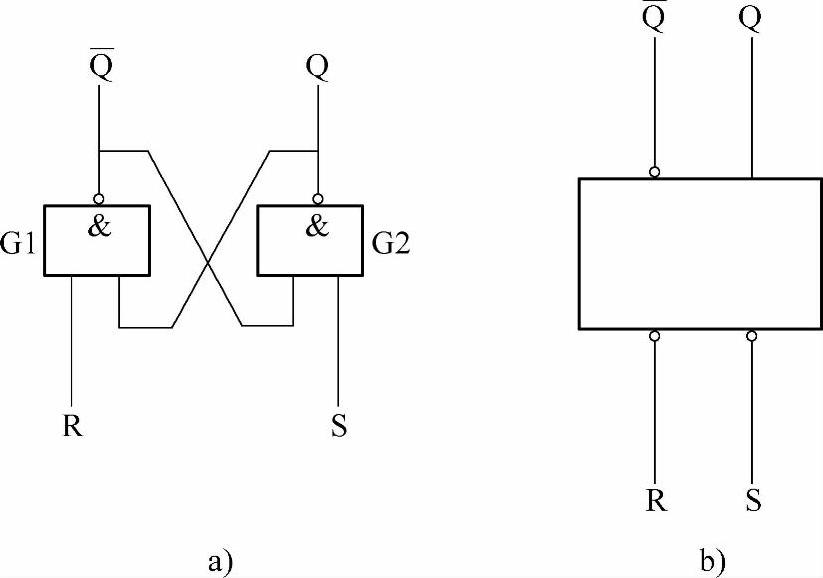

上述逻辑关系的变化情况列于表8-1中。

表8-1 基本RS触发器状态表

表中Qn+1表示触发后的电路状态。由表可知,与非型基本RS触发器是低电平触发(或低电平有效)。

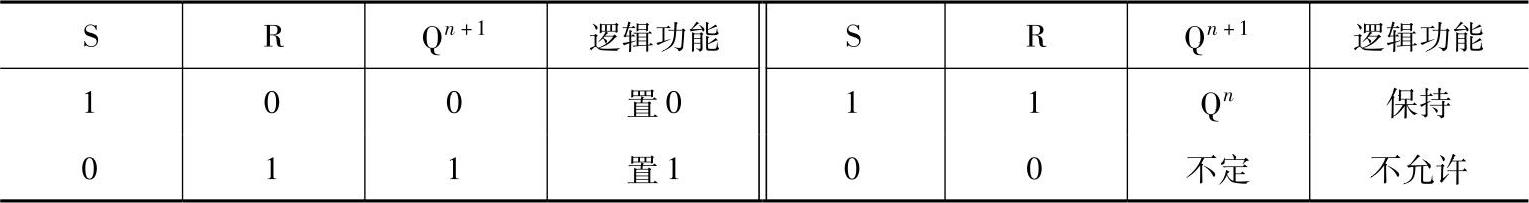

图8-2 主从JK触发器

a)逻辑电路 b)逻辑符号