主从JK触发器

图8-2所示为主从JK触发器的逻辑电路和逻辑符号。在图8-2a中,与非门D1~D4组成从触发器,D5~D8组成主触发器, 和

和 分别为直接置“0”和置“1”端,字母上面的“—”表示为负脉冲触发。时钟脉冲CP经过D9非门倒相,使主、从两触发器形成互补的时钟输入,可防止触发器空翻。所谓触发器空翻是指在同一个计数脉冲作用下,触发器状态变化两次(或多次)的现象。

分别为直接置“0”和置“1”端,字母上面的“—”表示为负脉冲触发。时钟脉冲CP经过D9非门倒相,使主、从两触发器形成互补的时钟输入,可防止触发器空翻。所谓触发器空翻是指在同一个计数脉冲作用下,触发器状态变化两次(或多次)的现象。

主从JK触发器的工作原理如下:

1)J=1、K=0 设触发器初始状态Q=1, ,D7、D8两门因均有0输入而被封锁。由基本R-S触发器的逻辑功能得知,主触发器的状态在CP到来后保持原来状态不变。若触发器的初始状态为Q=0、

,D7、D8两门因均有0输入而被封锁。由基本R-S触发器的逻辑功能得知,主触发器的状态在CP到来后保持原来状态不变。若触发器的初始状态为Q=0、 ,则在CP=1时,D8门打开,D7门被封锁,主触发器被置“1”;而在CP=1时,经D9门倒相,使D3、D4两门均有0输入而被封锁,直到CP下降沿到来后,即CP=0,D3、D4两门才被打开,从触发器取得与主触发器一致的状态,被置“1”。由此可见,无论触发器原来的状态如何,当J=1、K=0时,CP信号到来后,触发器置“1”。

,则在CP=1时,D8门打开,D7门被封锁,主触发器被置“1”;而在CP=1时,经D9门倒相,使D3、D4两门均有0输入而被封锁,直到CP下降沿到来后,即CP=0,D3、D4两门才被打开,从触发器取得与主触发器一致的状态,被置“1”。由此可见,无论触发器原来的状态如何,当J=1、K=0时,CP信号到来后,触发器置“1”。

2)J=0、K=1 设触发器初始状态为Q=0, ,D7、D8两门均被封锁,主触发器的状态在CP到来后保持原来的状态不变。若触发器初始状态为Q=1、

,D7、D8两门均被封锁,主触发器的状态在CP到来后保持原来的状态不变。若触发器初始状态为Q=1、 ,则在CP=1时,D7门打开,主触发器被置“0”,从触发器在CP=1期间被封锁,直到CP下降沿到来后,从触发器随之被置“0”。由此可见,无论触发器原来状态如何,当J=0、K=1时,CP信号到来后,触发器置“0”。

,则在CP=1时,D7门打开,主触发器被置“0”,从触发器在CP=1期间被封锁,直到CP下降沿到来后,从触发器随之被置“0”。由此可见,无论触发器原来状态如何,当J=0、K=1时,CP信号到来后,触发器置“0”。

3)J=K=0 D7、D8两门同时被封锁,触发器的状态保持不变。(https://www.daowen.com)

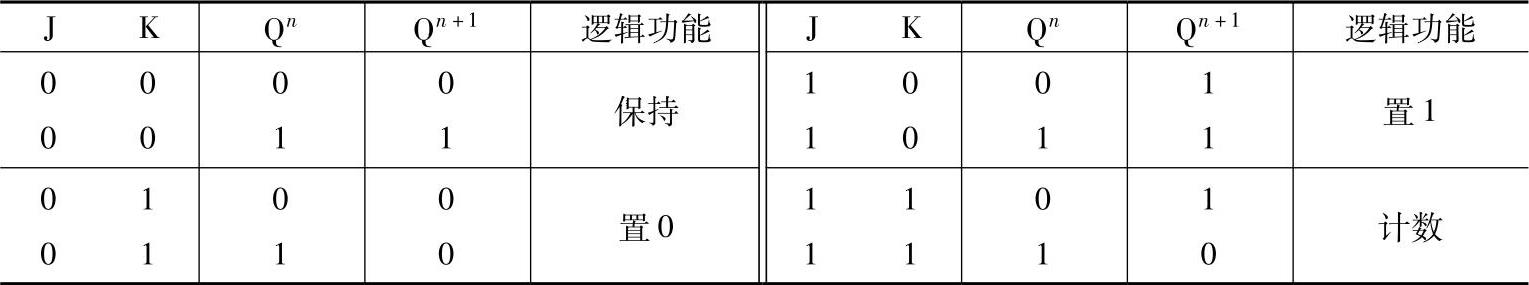

4)J=K=1 设触发器初始状态为Q=1、 ,在CP=1时,D7门全1输入,则输出0;D8门因有0输入而输出1,由表8-1可知,主触发器状态为“0”,在CP下降沿到来后,从触发器随之被置“0”。若触发器初始状态为“0”,则D7门输出1,D8门输出0,主触发器状态为“1”在CP下降沿到来后,从触发器随之被置“1”。即,在J=K=1时,每来一个时钟脉冲CP,触发器的状态就要翻转一次。主从J-K触发器的状态变化列于表8-2中。需要注意一点:触发器的状态翻转是在CP的下降沿处进行的。

,在CP=1时,D7门全1输入,则输出0;D8门因有0输入而输出1,由表8-1可知,主触发器状态为“0”,在CP下降沿到来后,从触发器随之被置“0”。若触发器初始状态为“0”,则D7门输出1,D8门输出0,主触发器状态为“1”在CP下降沿到来后,从触发器随之被置“1”。即,在J=K=1时,每来一个时钟脉冲CP,触发器的状态就要翻转一次。主从J-K触发器的状态变化列于表8-2中。需要注意一点:触发器的状态翻转是在CP的下降沿处进行的。

表8-2 主从JK触发器状态表