二、寄存器

存放数码的逻辑部件称为寄存器。具有记忆功能的触发器都能寄存数码。一个触发器能存放一位二进制数码,若需存放n位二进制数码,则应使用n个触发器,所以说触发器是寄存器的基本单元。

1.基本寄存器

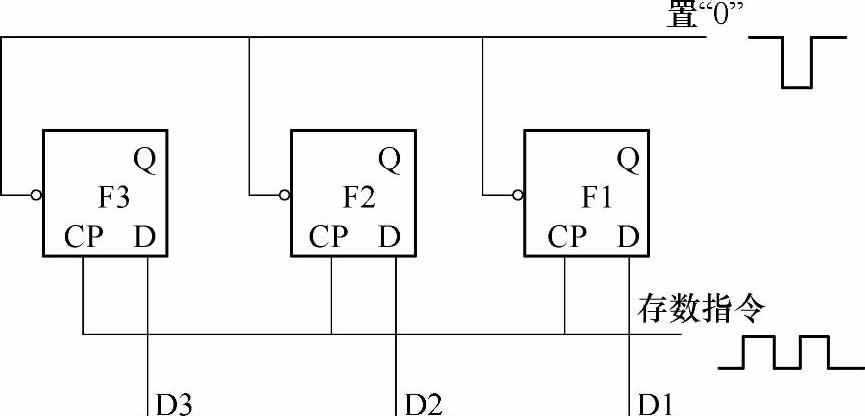

基本寄存器又称为数码寄存器,图8-8所示是由D触发器组成的三位数码寄存器逻辑图。由D触发器的逻辑功能得知,F1~F3的状态直接由D1~D3端的电平决定。把所需要寄存的数码加在D1~D3端,在存数指令的上升沿,F1~F3的状态被触发翻转。电路在接收数码之前,无需对寄存器清0。下面举例说明寄存器的工作过程。

图8-8 数码寄存器逻辑图

若寄存器要接收并寄存011这个数码,则在存数指令到来时,因D1=1、D2=1,使F1置“1”,即Q1=1,使F2也置“1”,即Q2=1;因D3=0,使F3置“0”,即Q3=0。这样在存数指令作用下,输入数码通过D1~D3控制端,被存入了相应的触发器中,而数码还可以从各触发器的Q端输出。

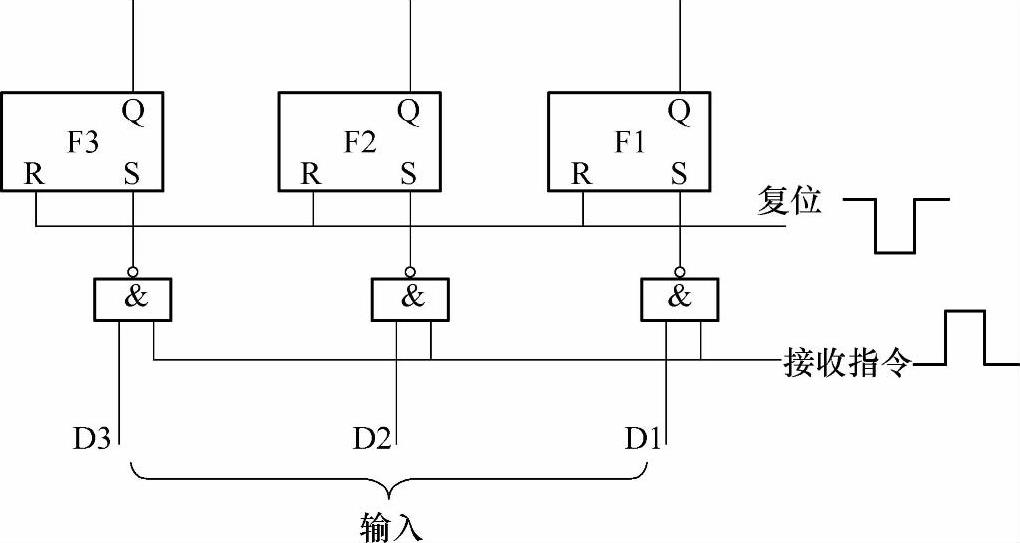

除了用D触发器组成的寄存器以外,还有用R-S触发器组成的寄存器,如图8-9所示。

图8-9 由基本RS触发器组成的数码寄存器

对于这种寄存器来说,在接收数码之前必须要先发一个复位脉冲,使寄存器中的所有触发器全部置“0”,然后再发接收指令。如输入的数码是110,当接收命令到来时,D3、D2、D1信号110将通过各自的与非门,其中F3和F2位的与非门输出负脉冲。由基本RS触发器的逻辑功能得知,这个负脉冲使F3、F2置“1”,而F1的S端输入的是正脉冲,使F1保持原来的“0”态,于是寄存器便把110这个数码寄存起来了。如果不对寄存器清0就接收数码,寄存器就可能出错。例如寄存器中原来存放的是101,现在要接收110新数码,因寄存器没有复位,则在接收命令下,寄存器中存放的数码将是111,即F1位出错。

2.移位寄存器

具有移位逻辑功能的寄存器就是移位寄存器。移位是指每当来一个移位脉冲,触发器的状态便右移或左移一位,也就是指寄存的数码可以在移位脉冲的控制下,依次进行右(或左)移位。在进行二进制加法运算、乘法运算以及二-十进制数转换时,都需要这种移位功能。可见,移位是一种重要的逻辑功能。

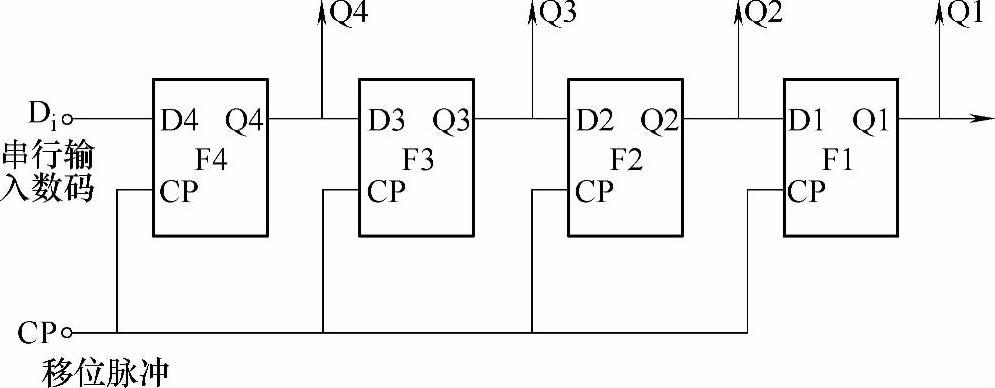

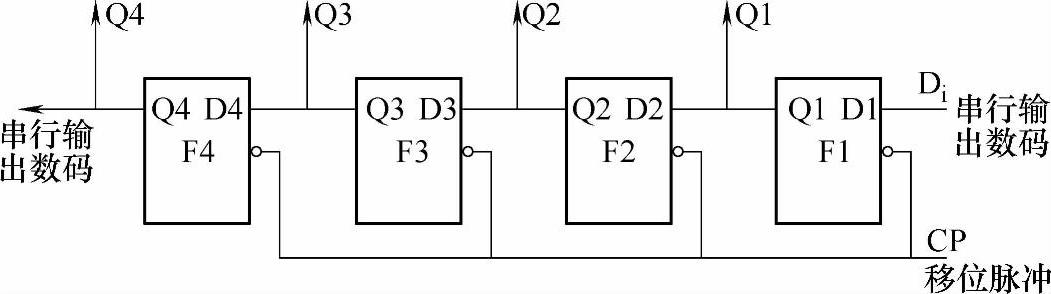

(1)单向移位寄存器 图8-10所示是由D触发器组成的四位右移寄存器的逻辑图。由图可见,输入数码加到最高位触发器的D端,每个触发器的Q端依次接到下一位触发器的D端。下面说明输入数码为1011时,数码从低位至高位依次串行送到寄存器的输入端Di时,移位寄存器的工作过程。

图8-10 四位右移寄存器

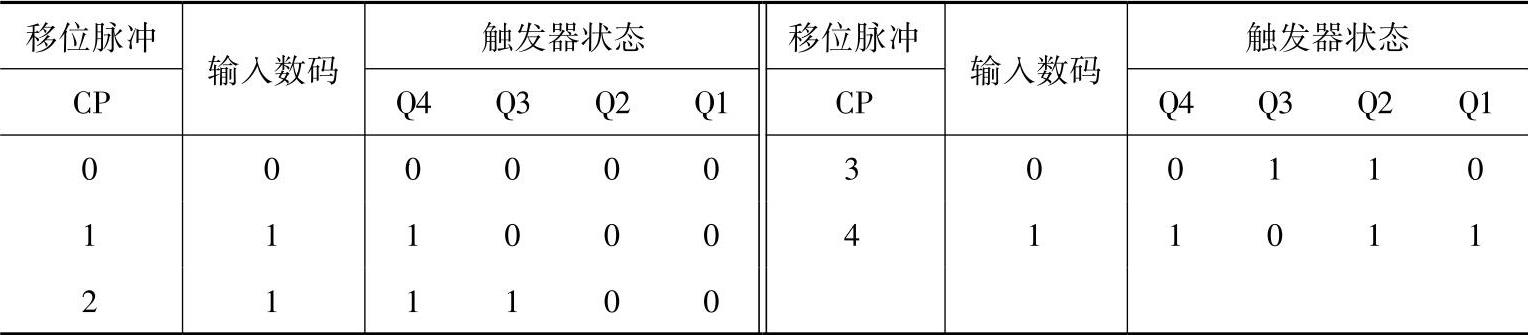

最低位输入数码1加到F4触发器的D4端,在第一个CP上升沿到来时,使F4置“1”,即Q4=1,经过一次移位后,移位寄存器为1000状态。随后的输入数码为1,故在移位脉冲的作用下,D4=1使F4置“1”,D3=Q4=1使F3也置“1”,则经过两次移位后,移位寄存器为1100状态。第三个输入数码为0,在CP作用下,Q4=0、Q3=1、Q2=1,则经过三次移位后,移位寄存器为0110状态。因第四个输入数码为1,则在CP作用下,Q4=1、Q3=0、Q2=1、Q1=1,经过四次移位后,移位寄存器为1011状态。四个触发器Q4Q3Q2Q1的状态与输入数码1011相对应。表8-5为四位右移寄存器状态变化表。(https://www.daowen.com)

表8-5 四位右移寄存器状态变化表

图8-11所示是用D触发器组成的四位左移寄存器逻辑图,其原理与右移寄存器类似,读者可自行分析。

图8-11 四位左移寄存器

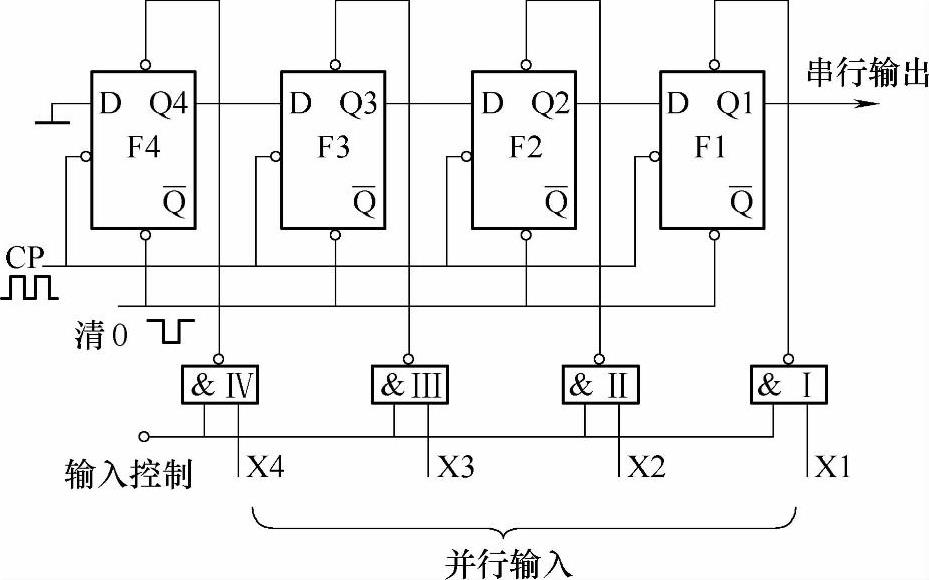

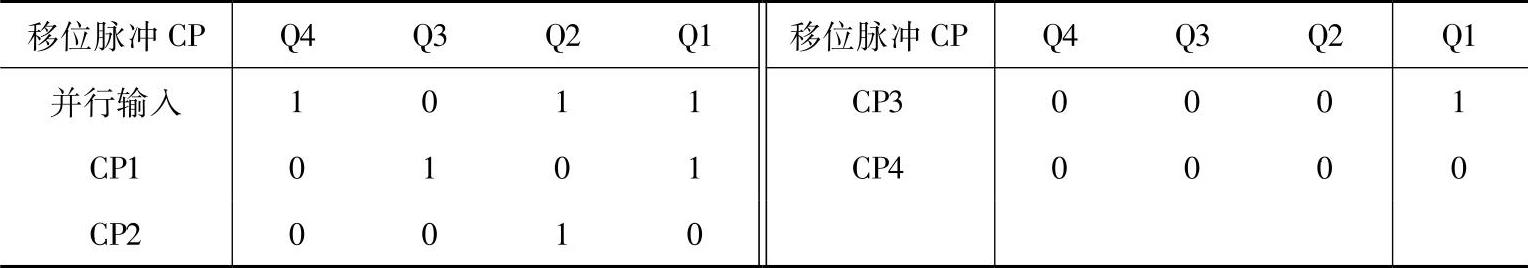

图8-12所示为并行输入-串行输出的四位右移寄存器的逻辑图。该电路由四个D触发器组成。输入数码X4X3X2X1通过输入控制信号,经四个与非门分别加到各触发器的直接置位端,F4触发器的D端直接接地。数码并行输入前,先将各触发器清0,随后输入控制信号“1”将四个与非门打开,并行输入数码X4、X3、X2、X1通过各自的与非门,从各个触发器的直接置“1”端存入寄存器。设输入数码为1011,即X1=1、X2=1、X3=0、X4=1,在输入控制信号“1”作用下,F4触发器的Q4=1,F3触发器的Q3=0,F2和F1两触发器的Q2=1、Q1=1,触发器F4F3F2F1的状态为1011,与并行输入数码一致。当第一个CP信号到来时,F4因D端接地而置成“0”态,同时F4的预置数码1传给F3,F3的预置数码传给F2……,F1的预置数码1从Q1端输出。以后,每来一个CP,数码就右移一位,直到全部数码串行移出寄存器。寄存器的工作情况见表8-6。

图8-12 并行输入-串行输出右移寄存器

表8-6 并行输入-串行输出移位寄存器状态表

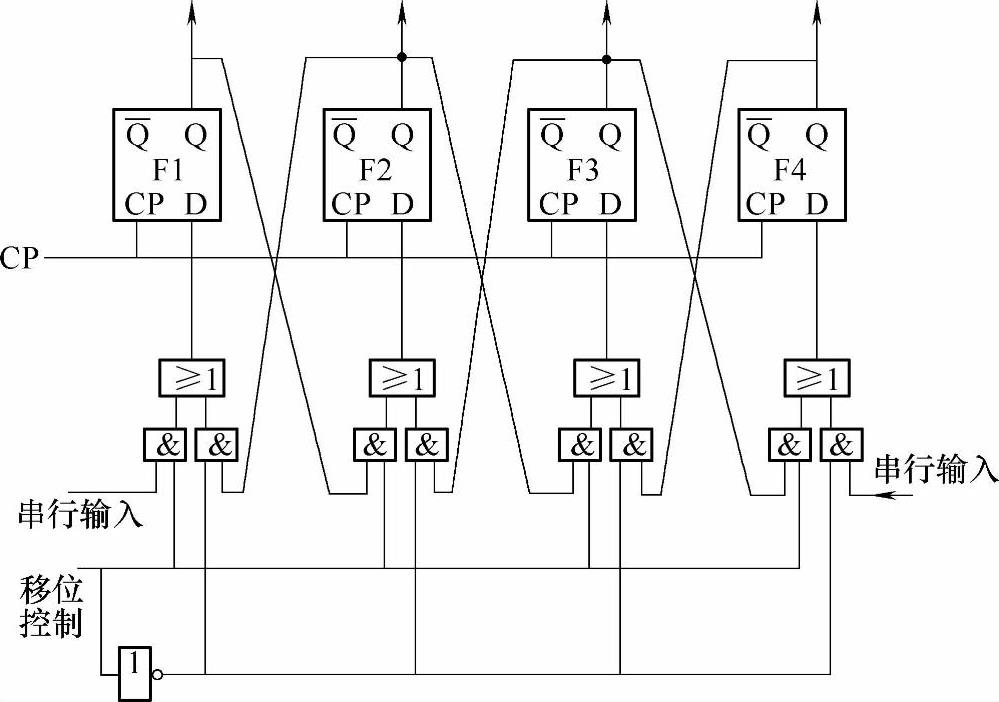

(2)双向移位寄存器 图8-13所示为由D触发器构成的四位双向移位寄存器的逻辑图。图中除了移位控制部分不同以外,其余部分与单向称位寄存器相同。双向移位寄存器的工作情况如下:

用移位控制信号来控制移位方向。当控制信号为1时,各触发器控制电路左侧的与门打开,右侧的与门封锁,串行输入数码通过或门加到F1的D端,而Q1、Q2、Q3分别通过或门加到F2、F3、F4的D端,在CP脉冲到来时,各触发器原寄存的数码向右移位。

图8-13 双向移位寄存器

当移位控制信号为0时,各触发器控制电路右侧的与门打开,左侧的与门封锁,串行输入数码通过或门加到F4的D端,而Q4、Q3、Q2分别通过或门加到F3、F2、F1触发器的D端,在CP脉冲到来时,各触发器原来所寄存的数码向左移位。