6.2.1 控制系统电路设计

本设计中控制系统硬件电路主要包括信号采样电路和锁相环电路,前文已对采样电路做了详细分析,所以本节将重点分析设计锁相环CD4046相关硬件电路。

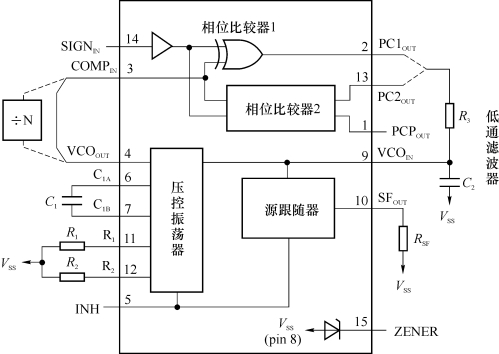

图6.5所示是锁相环CD4046内部结构图,主要由相位比较器1和相位比较器2、压控振荡器、源跟随器等部分组成。相位比较器1要求两比较信号的占空比均为0.5,而相位比较器2是一个由信号的上升沿控制的数字存储网络。相位比较器2对输入信号的占空比要求不高,允许输入非对称波形,具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐振,适合本书的信号特征。因此本书采用相位比较器2来完成对采样信号的鉴相。

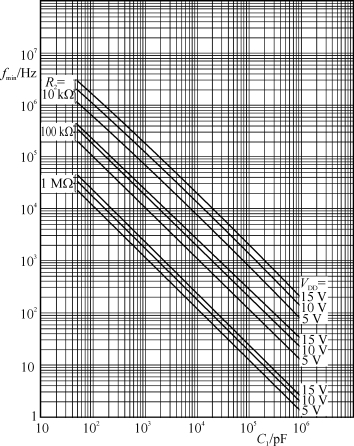

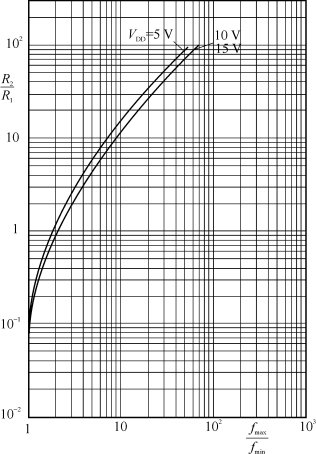

对于由CD4046构成的锁相环路,环路参数的计算主要是确定与压控振荡器输出频率有关的参数值R 1、R 2和C 1(如图6.5所示)以及低通滤波器(如图6.8所示)的参数值R 3、R 4和C 2。锁相环的捕获区间设置为压电变压器工作的最低频率和最高频率之间。记操作的中心频率为f o,那么f min=f o-Δf L,f max=f o+Δf L。这里取f o=79 k Hz,Δf L=2 k Hz。又因为外部参数一般取值范围需满足R 1,R 2>10 kΩ、C 1≥50 p F,所以依据锁相环数据手册给出的取值图(图6.6和图6.7)可得与输出频率有关的参数值分别为:R 2取100 kΩ,R 1取10 kΩ,C 1取0.1 n F。

图6.5 锁相环CD4046内部结构

图6.6 R 1不同取值下的最小频率与C 1

图6.7 R 2/R 1与f max/f min取值对照图(https://www.daowen.com)

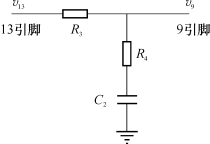

锁相环中低通滤波器的作用是滤除相位比较器输出的反映相位差电压值的高频成分,得到一个直流控制电压信号加至压控振荡器的输入端。其电路如图6.8所示,其参数的设计要满足使锁相环的输出频率值在锁定或捕获频率范围内。为此应该满足如下传递函数:

其中:

![]()

图6.8 低通滤波器电路图

低通滤波器的截止频率设置在系统的最高工作频率处。

通常R 4的阻值选为R 3的10%~30%,本书选择低通滤波器的参数分别为:C 2取10 n F,R 3取200Ω,R 4取20Ω。