3.3.4 技术特征

3.3.4.1 工作模式

SPARC微处理器支持用户模式和特权模式两种工作模式。用户可以通过设置程序状态寄存器(PSR)S位来切换这两种工作模式。在软件控制、外部中断或异常处理下,可引起处理器工作模式的改变。

一般来说,处理器是用某个控制寄存器中的一个方式位来提供某种模式,该寄存器描述了进程当前享有的权利。当设置方式位(PSR[S]=1),使处理器处于特权模式中,这样进程就可以执行指令集中的任何指令,并且可以访问系统中任何存储器位置和改变模式。

大多数用户程序运行在用户模式(PSR[S]=0)下,这时应用程序不能访问一些受操作系统保护的系统资源,也不能改变模式。应用程序既不能直接进行处理器模式的切换,也不允许执行特权指令,比如停止处理器,改变方位。任何这样的尝试都会导致致命的故障,除非异常发生,允许操作系统来控制系统资源的使用。

3.3.4.2 寄存器组织形式

SPARC架构中有32个通用寄存器、32个窗口寄存器和专用寄存器组。较少数量的寄存器使得访问速度大大提高,这对于提升程序的速度是很重要的。

1)通用寄存器(visible registers)

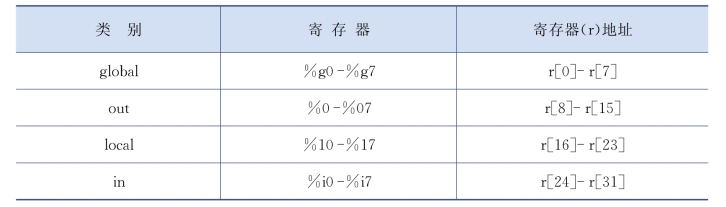

SPARC微处理器中有32个通用寄存器,这些寄存器对用户可见。其中,有8个寄存器是全局(global)寄存器,另外24个寄存器是窗口寄存器。SPARC微处理器中一个窗口包含3个寄存器组,每组里面有8个寄存器。3个寄存器组分别为out、local、in。大多数的SPARC微处理器有7或8个窗口,SPARC微处理器执行时将按照0~7的顺序依次切换窗口。SPARC通用寄存器地址分配见表3- 3。

表3-3 SPARC通用寄存器地址分配

2)窗口寄存器(windowed registers)

SPARC结构处理器具有可配置的通用寄存器组。在程序运行时,寄存器窗口中保存着当前进程的状态信息。在任一时刻,程序只使用一组寄存器窗口,当发生函数调用或返回时,处理器会在不同的寄存器窗口间移动,以保存当前环境。

3)专用寄存器组

SPARC微处理器有10个专用寄存器,其中PSR称为程序状态寄存器,其内容反映并控制处理器的运行状态,因为比较重要,因此读/写PSR的指令一般是特权指令。(https://www.daowen.com)

3.3.4.3 中断和异常管理

计算机通常用异常来处理在执行程序时发生的意外事件,如中断、存储器故障等,它需要停止程序的执行流程。在程序执行过程中通过控制跳转类指令,程序可跳转到特定的地址标号处执行,或者跳转到特定的子程序处执行。而当异常中断发生时,系统执行完当前指令,将跳转到相应的异常中断处理程序处执行异常处理,异常中断处理完成后,程序返回。

异常中断事件改变了程序正常执行的顺序,是程序执行的非正常状态。在进入异常中断处理程序时,要保存被中断程序的执行现场。在从异常中断处理程序退出时,要恢复被中断程序的执行现场。每种异常中断都具有各自的备份寄存器组。对异常中断的了解是处理器应用必须掌握的基本知识。下面将详细讨论SPARC体系中的异常中断类型和异常处理机制。

1)异常中断

在SPARC体系结构中,异常中断用来处理系统复位功能、指令访问错误和数据存储错误等,这些“不正常”事件都划为“异常”。SPARC异常中断请求可导致以下3种陷阱(traps):

(1)精确的trap。一个特殊的指令导致一个精确的trap,这个trap发生在任何程序状态被陷阱引导指令改变之前。当一个精确的trap发生的时候,如下条件保持不变:

①其中PC保存在r[17](本地寄存器1)并指向引起trap的指令,而n PC保存在r[18](本地寄存器2)并指向下一个将要运行的指令。

②在引起trap之前指令已经完成执行。

③在引起trap之后指令保持不执行。

(2)延时的trap。一个特殊的指令也同样会导致一个延时的trap,但是不像精确的trap,一个延时的trap可能发生在程序状态被改变之后。这个状态可能被trap本身指令改变,或者被一个或多个在它后面的指令改变。

(3)中断的trap。中断的trap既不是精确的trap也不是延时的trap。中断的trap是被PSR的处理器中断级别(PIL)和PSR的TrapEnable(ET)共同控制的。中断的trap可能是由于以下原因造成的:

①一个外部的中断请求不直接涉及之前运行的指令。

②一个异常不直接涉及之前运行的指令。

③异常由之前运行的指令引起。

2)中断优先级

当几个异常中断同时发生时,就必须要按照一定顺序来处理这些异常中断。在SPARC中通过给各个异常中断赋予一定的优先级来实现这种处理顺序。复位的优先级为1,复位是优先级最高的异常中断,这时因为复位从确定的状态启动微处理器,使得与所有其他未解决的异常无关。处理器执行某个特定异常中断的过程中,称处理器处于特定的中断模式。

3.3.4.4 SPARC并行处理

SPARC并行处理器支持实时嵌入式操作系统。操作系统将任务队列对称分布于多个CPU之上,从而极大地提高了整个系统的数据处理能力。所有处理器都可以平等地访问内存、I/O和外部中断。系统资源被系统中所有CPU共享,工作负载能够均匀分配到所有可用处理器之上,其运算速度快、数据处理量大、能耗低,性能和可靠性等都远高于单核处理器。珠海欧比特公司推出的SPARC并行处理器是基于SPARC V8架构的高性能的32位RISC嵌入式4核处理器。其采用“对称多核处理”技术,是在一个芯片中集成四个功能一样的处理器核心,各处理器核心之间共享内存子系统及总线结构,总线竞争和仲裁由硬件自动完成,不需要用户设置的处理器系统。它专为嵌入式应用而设计,具有高性能、低复杂度和低功耗的特点。