4.3.4 PCI-Express总线

4.3.4.1 PCI-Express总线简述

PCI(peripheral component interconnect)总线规范在20世纪90年代由Intel公司提出。在处理器体系结构中,PCI总线属于局部总线(local bus)。局部总线作为系统总线的延伸,主要功能是为了连接外部设备。

Intel公司于2001年提出PCIE(PCI-Express)总线技术,PCIE作为第三代IO总线标准,采用串行数据传输和点到点互连技术,由于点到点互连结构中各设备并不共享总线带宽,因而大大提高了总线传输带宽,满足了当时及现在以至将来一段时间高速设备对总线带宽的需求。

和PCI总线相比,PCIE具有以下几个特点:

(1)串行差分传输。PCIE采用串行差分传输模式,每条通路上有两对LVDS差分数据线,一对负责对外发送数据,另一对负责对内接收数据,每对差分数据线上数据传输率均为2.5 Gbit/s。在提供足够传输带宽的同时,大大减少了设备间的连线,方便实现设备互连。

(2)点到点互连。与PCI的共享总线式结构不同,PCIE采用了点到点互连的结构,意味着每个设备都有独立的链路与系统相连,因此系统可为所有设备分配独立的通道资源,保证每个设备真正占有的带宽,可实现各设备同时与系统进行高速数据传输。

(3)带宽灵活。一条PCIE链路可根据实际需要灵活配置成x1、x2、x4、x8、x12、x16、x32个并行的数据通路,每条通路在两个方向上都提供2.5 Gbit/s的带宽,满足不同设备的带宽需求。

(4)软件与PCI兼容。PCIE总线结构将一条链路视为一条总线,采用与PCI相同的使用模型和读写通信模型,从地址空间、配置机制及软件上保持与PCI总线的兼容,原有PCI总线系统的设备驱动程序可不经修改移植到PCIE总线系统中使用。

4.3.4.2 PCI-Express总线特性

1)总线结构

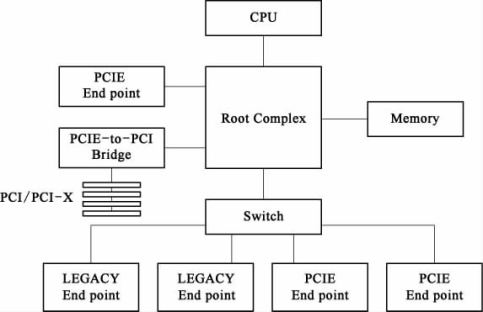

PCIE总线系统拓扑结构由一系列点到点链路设备互连组成,如图4-19所示。PCIE拓扑结构的基本元素包括根联合体(Root Complex)、与根联合体相连的CPU、主存储器(Memory)、交换器(Switch)、端点(End point)、PCIE到PCI的桥等。

根联合体是I/O层次结构的根设备,其将CPU和系统主存储器子系统连到I/O上,功能相当于PCI系统中的北桥。交换器相当于一个具有多个虚拟PCIE-PCI桥逻辑功能的设备集合,它可以将事务从任意一个端口路由到另一个端口。端口是一个具体的设备,在PCIE事务中充当请求者或完成者的角色。

图4-19 PCIE典型拓扑结构

2)总线协议(https://www.daowen.com)

PCIE到PCI的桥提供PCIE架构到PCI层次结构的连接,其中PCIE端口必须遵循PCIE协议,原来基于PCI总线的设备可以并入PCIE系统中。

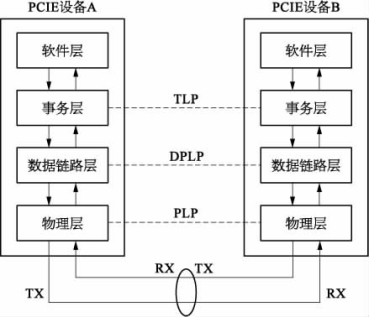

PCIE数据传输基于数据包,体系结构采用分层设计,类似于计算机网络通信中ISO/OSI七层结构,而PCIE的核心层次有三层,PCIE总线分层结构如图4- 20所示。

图4-20 PCIE总线分层结构

PCIE总线分层结构包括物理层、数据链路层、事务层和软件层。

(1)物理层。为最底层,是物理接口之间的连接,位于数据链路层与链路之间。物理层体现PCIE总线接口的物理特性,如通道数、LVDS驱动和点对点串行连接等。物理层的主要任务是:①接收物理层的报文并传送至数据链路层;②发送数据链路层的DLLP到物理层。通过8b/10b解码方式,时钟信息被编码成数据流形式,这种方式比单独采用并行时钟的方式更能提高传输效率和节省传输通道。该层提供了x1、x2、x4、x8、x12、x16和x32方式的信道带宽。

(2)数据链路层。为事务层和物理层的中间层,其主要职责是在链路中提供这两个层次之间交换TLPs的可靠机制。事务层向数据链路层传输数据包时,在报文中添加序列号和发送冗余校验码,数据链路层依靠ACK/NAK协议来保证报文的可靠传输,使用CRC校验检测DLLPs和TLPs数据包的数据完整性。该层对链路管理功能包括TLP确认、电源确认及流量控制(flow-control)信息交换等。

(3)事务层。事务层的职责是组装和拆解事务层数据包(TLPs),一端接收PCIE设备核心层的数据请求,形成事务,创建TLPs传输至数据链路层,另一端从数据链路层接收响应数据包。有些请求包需要读回一个响应包。事务层为该层提供四种事务类型:存储空间读取和存储空间写入事务、I/O空间读取和I/O空间写入事务、配置空间读取和写入事务、消息传递作为事件的信号告知用户事务。

(4)软件层。PCIE的软件层保持与PCI总线的兼容,因此被认为是最重要的部分。PCIE启动时,系统的初始化和运行就像在PCI环境下,不需要对系统中的资源和硬件设备进行任何改动。在软件响应时间模式上,PCIE支持PCI的共享内存模式和本地存储。事实上,在PCIE平台中,完全可以实现PCIE总线到PCI总线软件上的平稳过渡。

在PCIE总线中数据包的生成必须通过若干个协议层,其中比较有代表性的包括应用层、物理层等;应用层生成数据包,之后经过多个层级,其中比较有典型意义的包括事务层、物理层等,最后传输至指定设备。此外,在获取数据的过程中,数据包会按照秩序经过多个层级,其中比较有代表性的包括物理层、事务层等,最后到达应用层完成数据包分析。

这种机制的数据传送是基于事务的,端点设备能够发起指向根联合体或另一个端点设备的事务,根联合体也能够发起指向端点设备的事务。PCIE事务层数据交易是建立在请求者(requester)和完成者(completer)之间的数据传递上。前面曾提到过PCIE的数据交易类型可概括为I/O事务、存储器事务、消息事务和配置事务。事务的传递实际上是对TLPs数据包进行组装和拆解,然后传递的过程。

4.3.4.3 PCI-Express总线设计

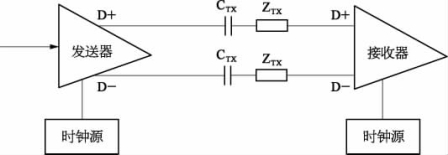

由于差分信号摆幅较小,可使电路在高频工作状态下保持较低功率;差分信号同时传送,发射噪声抵消,获得良好的EMI性能;差分数据线相离较近,传输条件较一致,使信号对环境噪声不敏感;同时还可有逻辑1、逻辑0和电气闲等多种传输状态,PCIE规定在链路两端的驱动器和接收器采用高速LVDS传送数据。LVDS链路上一条通路沿一个方向的差分驱动器(输出)和差分接收器(输入)如图4- 21所示。

图4-21 LVDS总线电路原理图