3.6.2 MIPS体系架构简介

2026年01月15日

3.6.2 MIPS体系架构简介

32位MIPS处理器采用五级流水线结构,支持中断处理,提供可选的配置,观察并控制系统缓存或时钟、虚实地址转换等操作,指令执行速度接近每个时钟周期执行一条指令,是RISC架构中的经典之作。

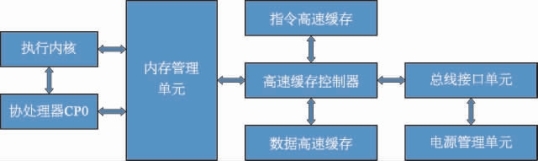

MIPS处理器中与内存管理单元(MMU)有关的各功能模块的连接如图3-15所示,其中包括执行内核、协处理器CP0、高速缓存Cache。执行内核的作用是执行指令,采用load-store结构,在运算过程中,需要将存储器上的数据提前读取到其内部的寄存器堆中,而其内部的寄存器堆包括32个32位的通用寄存器。通常执行内核需要MMU进行虚实地址转换后,使用转换得来的物理地址访问缓存或内存,然后与外部的功能单元进行交互。协处理器CP0用作系统控制,通过配置内部的一系列寄存器来完成配置CPU的工作状态、高速缓存控制、异常控制和MMU控制等工作。总线接口单元负责将经过MMU转换后的地址送到内存中进行指令或数据访问。电源管理单元负责为整个系统供电。MIPS是业界最典型的RISC架构,其指令格式十分简单,按照指令格式可划分为三类,即寄存器类型(R-type)指令、立即数类型(I-type)指令和跳转类型(J-type)指令。(https://www.daowen.com)

图3-15 MIPS处理器系统框图