3.4.4 技术特征

1)超标量技术(https://www.daowen.com)

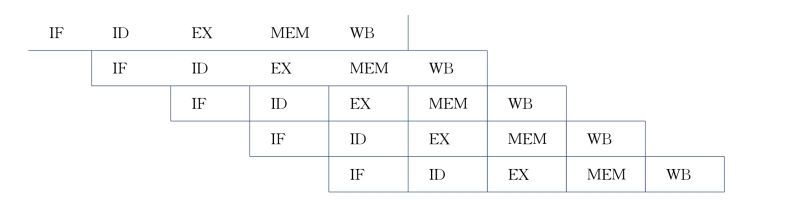

并行计算机体系结构可以显著提高微处理器的性能,这包括指令级并行性(ILP17)、数据级并行性(DLP18)及线程/进程级并行性(TLP19)。指令级并行最简易的实现方法是使用流水线,指令流水线技术可以使两个以上的指令同时被执行。相比已被淘汰的单指令单周期(single instruction single period)技术和单指令多周期(single instruction multiple period)技术,指令流水线技术使CPU不必等候上一条指令执行完成,即可执行下一条指令。基本流水线有时间重叠性能,见图3- 8。

图3-8 基本流水线(时间重叠):经典五级流水线

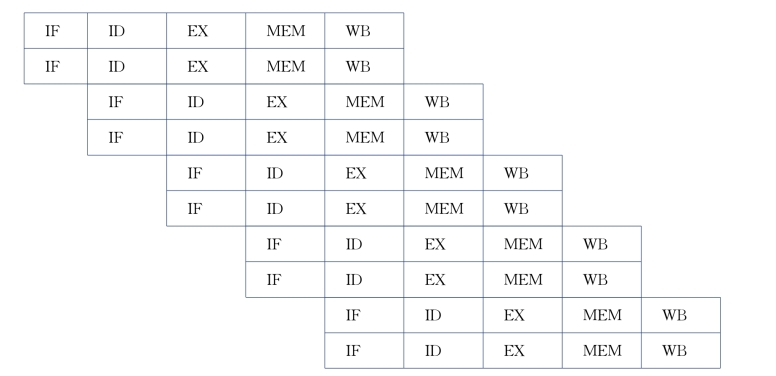

PowerPC具备超标量计算能力,使用超标量流水线,较经典流水线复杂程度高。超标量流水线(superscalar pipeline)是一种在同一时钟周期发射多条指令的技术,同时具有时间重叠和空间重叠功能。超标量流水线每个时钟并行执行两条以上的指令,发射器用于读取指令并检测各指令之间的相互依赖性,以决定指令是否能够并行执行,然后发指令到执行单元。在超标量CPU结构的设计中,难点在于设计一个高效的发射器,这包括指令发射策略和检测指令依赖的逻辑。通常,指令层并行(integral life practice,ILP)同时发射的指令数在2~10之间,单纯通过硬件进一步开发ILP已经非常困难,因为并发执行的指令越多,硬件复杂度越高。超标量流水线见图3- 9。

2)工作模式

通常PowerPC内核有两种运行模式,即用户模式(user mode)和超级用户模式(supervisor mode)。分别对应两组寄存器:用户模式寄存器(user-level register,ULR)与超级用户模式寄存器(supervisor-level register,SLR)。

PowerPC处理器在用户模式或超级用户模式下可以访问用户模式寄存器(ULR)。

图3-9 超标量流水线(时间重叠和空间重叠)

用户可以通过修改内核的处理器状态寄存器(machine state register,MSR)的PR位进行用户模式和超级用户模式的切换。

3)寄存器组织形式

PowerPC体系结构为多数计算机指令定义了寄存器到寄存器操作。寄存器指令的源操作数作为嵌入指令操作码的立即数。寄存器指令允许一个目标寄存器区分两个源操作数。加载存储指令在寄存器和存储器之间传输数据。

该单元处理器有两级权限——超级用户模式操作(用于操作系统)以及用户模式操作(用于应用软件)。访问特权指令、寄存器及其他资源,允许操作系统控制应用环境(提供虚拟存储器、保护操作系统和关键机器资源)。控制处理器状态、地址传输机制以及超级用户寄存器的指令,只可以在处理器运行于超级用户模式下执行。

4)中断和异常管理

PowerPC支持16种中断异常处理,所以对应有16个中断源,但是PowerPC的内核仅支持Critical Input和Extend两种外部输入中断。在中断请求的处理响应无法满足实际需求时,引入中断控制器(interrupt controller,INTC)这个概念,通过软件的方法,对有限的硬件中断资源进行扩展。每一个中断控制器有32个中断输入接口、1个中断信号输出接口。当一个或多个输入端有中断输入信号发生时,输出端就输出中断信号。而中断控制器包含一个32位的寄存器,其每一位对应一个输入中断。当有输入中断发生时,中断控制器对应的标志位便被置1。中断响应处理过程是从低到高对寄存器中的标志位进行轮询,来判断外部中断的来源。因此,其寄存器标志位位置顺序决定了中断响应优先级的高低。