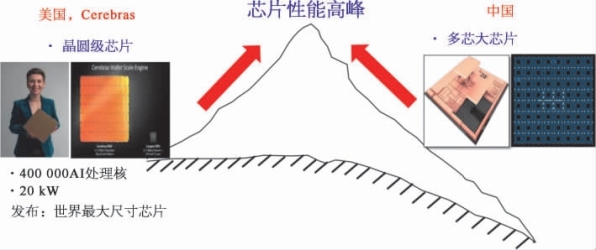

10.2.1 多芯并行

从系统端出发,首先将复杂功能进行分解,然后开发出多种具有单一特定功能、可相互进行模块化组装的裸芯片,如实现数据存储、计算、信号处理和数据流管理等功能,并最终以此为基础,建立一个Chiplet的芯片网络。多芯并行技术路线如图10- 3所示。

图10-3 多芯并行技术路线

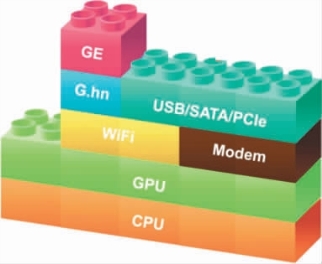

搭积木造芯片的模式名叫Chiplet,它是一类满足特定功能的die,被称为模块芯片。Chiplet模式是通过die-to-die内部互连技术将多个模块芯片与底层基础芯片封装在一起,构成多功能的异构芯片的模式(图10-4)。理论上讲,这是一种短周期、低成本的集成第三方芯片(例如I/O、存储芯片、NPU等)的技术。

图10-4 Chiplet模块芯片示意图

2018年,在美国航空航天局(NASA)“高性能科学计算”(HPSC)项目支持下,ARM公司与密歇根大学合作开发一种基于ARM的新型航天器处理器技术,该技术被称为HPSC Chiplet。

1)HPSC项目目标

在太空中,辐射会干扰甚至损害电子电路,这使得抗辐射加固、多处理器、高可靠计算系统对深空探测至关重要。2011年,NASA启动了HPSC项目,以应对现有空间计算能力不能满足现阶段和未来NASA任务所需处理能力的要求。

2)HPSC项目管理(https://www.daowen.com)

HPSC项目由NASA空间技术任务局和科学任务局内的“游戏改变发展”计划提供资金支持,由波音公司牵头,密歇根大学和ARM公司参与其中。整个HPSC项目由喷气推进实验室管理,Chiplet的采购由戈达德空间飞行中心管理。此外,空军研究实验室、空间飞行器局也在该项目上进行了密切合作,以确保Chiplet与他们的任务要求相关。

3)HPSC Chiplet

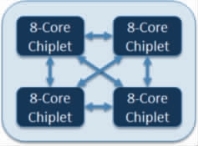

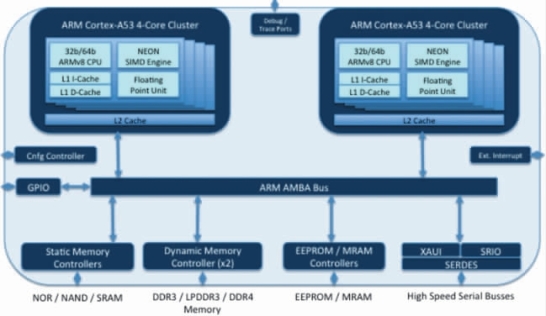

该SoC系统包含一个用于处理高吞吐量计算的高性能子系统,一个用于时序关键应用的实时处理子系统,以及一系列可用于创建多芯片系统或与传感器和执行器的互连,如图10- 5、图10- 6所示。

图10-5 多芯并行配置

图10-6 HPSC多芯并行架构

ARM公司提供了一个强大的实时处理器(Cortex-R级处理器),可用于硬件实时计算,在低功耗设计中的优势将促进节能且实现高性能科学计算(Cortex-A级处理器),服务质量能力(QoS/QVN)提供了一种管理片上资源需求的机制,TrustZone技术则为空军部署提供了子系统的隔离和安全性。

尽管当今航天器的运行系统都经过了抗辐射加固,但是并不具备现代处理器的性能。HPSC Chiplet的抗辐射加固设计将在更小、更轻的封装中提供与当前系统相当的可靠性,极大地提高了计算能力和能效。HPSC Chiplet驱动的系统将采用现代高能效的ARM系统级芯片设计取代数十年前的处理器技术,并将提供比当今航天器中更大数量级的计算机处理能力。这将使机载自主性、宇航员辅助和高带宽传感器数据处理等功能得到增强,并可为日益智能化的航天器提供一条前进的道路。