6.5.1 电磁兼容性设计

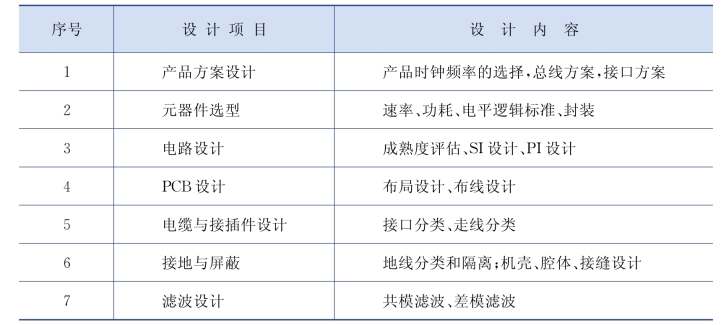

星载嵌入式计算机产品的电磁兼容性设计主要包括产品方案设计、元器件选型、电路设计、PCB设计、电缆与接插件设计、接地与屏蔽、滤波设计等方面,见表6- 2。

表6-2 星载嵌入式计算机产品的电磁兼容性设计主要内容

1)产品方案设计

星载嵌入式计算机数字电路部分是在特定时钟频率下按设计好的时序工作,方波时钟及其控制的所有信号可以衍生出宽带谐波,时钟频率的设计很重要。合理选择产品时钟频率,其基波和谐波频率应避免与敏感产品的频点重合;在满足性能指标的前提下,应尽量降低工作主频,可采用内部倍频方式提升运算性能。

在满足适用可靠度要求的前提下尽量简化系统设计,降低系统的功能密度,去除非必要的兼容设计、冗余设计,降低PCB密度。

星载嵌入式计算机一般包含多种功能模块,内总线信号丰富,产品内模块互连应多用差分形式,除需要瞬时大吞吐量的高速存储总线外,少用单端并行总线。优先选用低摆幅串行差分传输,如LVDS等。

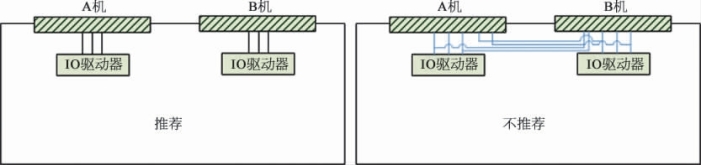

驱动和接收芯片的速率应尽量保持一致,慎用高速器件驱动低速器件的方案,降低地弹共模噪声。接口信号的交叉备份延长了接口芯片到外接插件的距离,容易耦合噪声,如图6-19所示。应慎选A/B机交叉备份方案,外总线接口器件(IO驱动器)应紧挨接插件,并远离其他高速器件。

图6-19 一对一备份、一对二交叉备份接口形式

2)元器件选型

尽量选择低电压、低功耗的元器件,降低元器件的信号辐射强度,降低模块内部的信号干扰和产品对其他系统的电磁影响。优选SoC、SiP等片上系统,可提高数字系统的集成度,降低功耗和PCB密度,简化匹配方案,降低寄生参数。

信号边沿速率越快,高频分量幅度越大,因此在满足时序性能要求的前提下,尽量选用慢边沿低速器件。推荐选用I/O接口可调整的器件,比如大部分FPGA的I/O边沿斜率和驱动电流可调,在满足时序要求的前提下可以配置成慢边沿、小电流模式的元器件。

优先选用寄生参数小的器件封装,比如TSOP、CSP、BGA,尽量避免使用插件封装。

电容对信号质量和噪声控制的作用很大,钽电容适用于低频终端,主要是存储器和低频滤波领域。在中频范围内,陶瓷电容比较适合,用于去耦和滤波。去耦电容主要功能是提供一个局部电源给有源器件,以减小开关噪声在印制板上的传播和将噪声引导到地,电容值须依据要滤除信号的上升时间和下降时间进行选取。选用的电容应具有较低的等效串联电阻值。

3)电路设计(https://www.daowen.com)

星载嵌入式计算机电路尽量继承已有成熟可靠、得到飞行验证的电路,对于采用的新电路设计应进行充分论证。快边沿的驱动器,建议加源端串联匹配电阻,防止信号反射使得高次谐波分量的幅度增大。总线接插件应多定义地管脚,并且在整个接插件上相对均匀分布。建议每个单端信号和电源都有一个靠近的地管脚。对外接口信号尽量避免非差分信号,沿接口进行放缓处理,尽量选用LVDS。

电源完整性方面,低频去耦大电容(一般为固体钽电容)去耦半径大,大功率器件建议每个器件一组(防止钽电容短路失效,一组为两个串联),小功率器件可以多个器件合用一组。高频去耦小电容(如陶瓷电容)去耦半径小,建议每个电源管脚配置一个;电容的谐振频率(由电容值与寄生电感决定)应与需要去耦的频率对应。

4)PCB设计

星载嵌入式计算机的高速数字模块建议采用多层板设计,加入多层电源和地平面,一般建议长距离走线布在内层,使得平面层对信号具有一定的屏蔽作用。电源平面应相对于地平面内缩,在板边打一圈缝合地孔。

根据电路的特点进行模块化布局,将强电信号和弱电信号分开。根据单元电路对电磁兼容性敏感程度不同进行分组,将电路中易受干扰的元器件尽量远离干扰源。数模混合板做数模地分割处理,在数字信号跨越数模地的位置应放置连接电阻或磁珠,减小数字信号跨平面分割产生的共模电流。高频小电容紧靠芯片管脚放置,控制电源高频纹波,控制共模电流。非接口高速器件不靠近外总线接口,噪声电流尽量远离接口;外总线接口器件应紧靠对外接插件放置,到接插件的走线尽量短。与开关电源配对的EMI滤波器应靠近电源输入接口,保证隔离效果。

根据信号的重要程度分级布线,优先保证时钟信号、高速串行差分信号、模拟信号等重要或敏感信号。与非完整平面(如一个平面层分割成多个电源)相邻的信号层,信号走线尽量少跨越平面分割,防止共模电流的产生。时钟等重要信号走线应尽量短,建议单负载;多负载时采用菊花链等拓扑结构控制信号反射,走线尽量短,以降低天线效应,防止意外的发射或接收电磁干扰。差分信号用差分走线规则,紧耦合走线,保持对称性,降低产生的共模噪声。线路避免布设过密,平行走线间距尽量大于差分走线宽度的3倍(3 W规则),降低信号间的串扰。常规信号一般控制在单端阻抗50Ω、差分阻抗100Ω,并保持阻抗连续。

5)电缆与接插件设计

接口信号应按类型和功能划分,不同类型的信号走线分开并有独立的接插件。功率电缆与信号电缆分开走线。对外接插件排点应尽量确保地线充足,单端信号线与地线数量比例建议为1∶1。对于装星载计算机不再使用的产品对外空接插件,应做好空插头保护,无用管脚接地并完整屏蔽包覆。接口差分信号的传输电缆建议用双层屏蔽电缆,其中,内层屏蔽层接数字地,为差分信号转共模产生的噪声提供回流路径;外屏蔽层接机壳地且与接插件完整连接。有条件时,建议在所有电缆两端接铁氧体共模扼流圈,衰减流经电缆的共模电流。

6)接地与屏蔽

将地线分类和隔离,产品内部信号多点接地或接平面地。对于印制板上的局部强干扰源可以设置屏蔽块或金属网层。对于强干扰模块,在重量与散热允许的情况下,可以考虑设置整板整面屏蔽或配置独立屏蔽盒,有效控制对外辐射。产品壳体对其内部电路形成全包围性金属屏蔽,产品外部接地、搭接依靠安装面,安装螺钉和接地桩。机箱盖板、侧板接缝处按楔形设计,尽可能使接缝造成曲折的设计,增加电磁波通过的损耗。另外,如果条件允许时还应在接缝处设计导电衬垫,确保接缝处的电连续性。导电衬垫应选用不带背胶的型号,可在局部点胶以便固定。产品对外的高频接口和低频接口连接处均采用无缝连接,可具有良好的对外屏蔽效果。

高电压小电流干扰源以电场干扰为主,采用高电导率金属屏蔽体并采取接地措施。低电压大电流干扰源以磁场干扰为主,采用高磁导率材料实现磁屏蔽或提供磁旁路,增加屏蔽体厚度或采用多层屏蔽,屏蔽体无须接地。在频率很高的情况下,远场电磁屏蔽可采用高电导率材料制成的屏蔽体,并良好接地。如果需要屏蔽的磁场强度很强,可考虑多层屏蔽。金属材料作为屏蔽材料,其电导率、磁导率会随外加电磁场、频率、温度等变化而变化,屏蔽体在经过机械加工后,必须经过热处理以恢复其导磁性。

7)滤波设计

电源输入滤波器一般选择DC/DC厂家研制生产的与DC/DC型号相匹配的输入滤波器。建议选用不带瞬态抑制二极管的滤波器。电源输出差模噪声滤波应选用高质量、低等效串联电阻(ESR)的电容,靠近电源芯片管脚放置;输出共模噪声滤波可采用共模扼流圈。

8)电磁兼容仿真

可以通过Mentor、Ansys、Cadence等仿真软件进行电磁兼容仿真,通过仿真可以得到印制板上具体信号的时域波形及频域频谱,进行干扰源和干扰强度分析。通过对匹配方式、拓扑结构、走线长度和过孔等进行设计优化,反复迭代,最终达到降低特定频点辐射强度的目的。