4.3.5 RapidIO总线

4.3.5.1 RapidIO总线简述

RapidIO是由Motorola和Mercury等公司率先倡导的一种高性能、低引脚数、基于数据包交换的互连体系结构,是为满足未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板之间的通信。下面以RapidIO Specification(Rev.2.1)协议为基准,介绍Serial RapidIO(简称“SRIO”)的接口要求。

4.3.5.2 RapidIO总线特性

1)总线结构

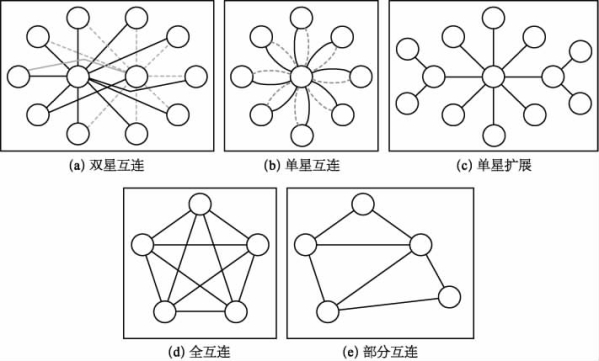

SRIO支持的基础网络拓扑结构包括双星互连拓扑、单星互连拓扑、单星扩展拓扑、全互连拓扑、部分互连拓扑五种,具体实例如图4- 22所示。

图4-22 拓扑示意图

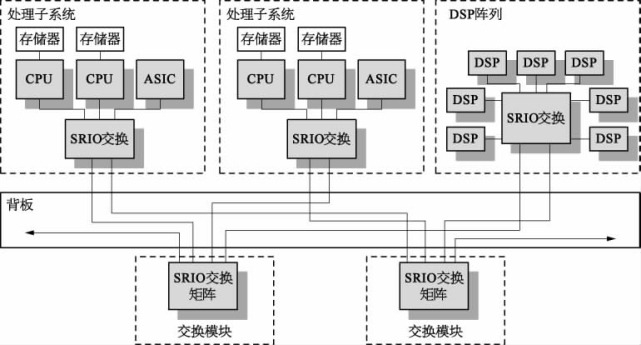

基于双星拓扑网络的空间子系统结构如图4-23所示,系统内各个模块均引出两路SRIO分别接入两个SRIO交换模块,从而组成双星型网络。数据传输方式默认为DMA形式,系统内部各个子模块可在模块内部采用一块RapidIO互连芯片用于处理单元互连;也可以直接将模块内处理器直接接入SRIO交换。通常可接入RapidIO互连网络的模块,包括但不限于:存储模块,支持DMA的计算-存储模块,实时采集模块(高速AD)、DSP阵列等。

图4-23 基于双星拓扑网络的空间子系统结构

2)总线协议

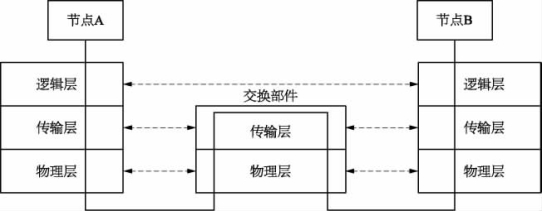

RapidIO是一种基于Serdes接口的高速串行传输技术。SRIO支持6.25 Gbit/s、5 Gbit/s、3.125 Gbit/s、2.5 Gbit/s和1.25 Gbit/s五种接口速率,支持1x、2x、4x三种位宽模式。SRIO协议分为三层:逻辑层、传输层和物理层。逻辑层定义了操作协议和包格式;传输层定义了包交换、路由和寻址机制;物理层定义了电气特性、接口形式、链路控制和错误管理机制等。SRIO通信模型如图4- 24所示。

图4-24 SRIO通信模型

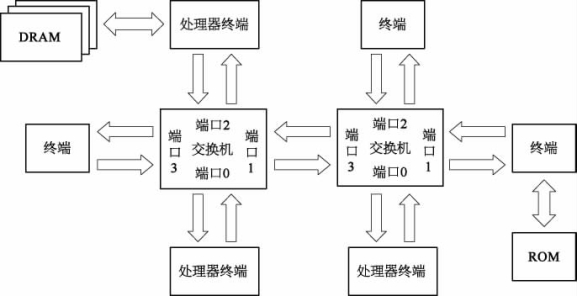

SRIO传输层是基于包交换的互连技术,网络主要由终端器件(End point)和交换器件(Switch)组成。终端器件是数据包的源或目的地,不同的终端器件以器件ID来区分。交换器实现数据包在各个端点间的路由和传送,且不对数据包做解释。基于交换的SRIO系统组成如图4- 25所示。

图4-25 基于交换的SRIO系统组成(https://www.daowen.com)

SRIO物理层基于Serdes技术实现,采用差分交流耦合信号传送数据。差分交流耦合信号具有抗干扰强、速率高、传输距离较远等优点。

为了支持全双工传输,SRIO收发信号是独立的,所以每一个串行SRIO端口由4根差分线组成。一组标准的SRIO接口由4个端口组成,共16根信号线。这4个端口可被用作独立的接口,传输不同的数据;也可合并在一起当作一个接口使用,以提高单一接口的吞吐量。发送时,逻辑层和传输层将组好的包经过CRC编码后被送到物理层缓存,“8b/10b编码”模块将每8位数据编码成10位数据,“并/串转换”模块将10位并行数据转换成串行位,发送模块把数字位转换成差分交流耦合信号在信号线上发送出去;接收的过程则正好相反。

4.3.5.3 RapidIO总线设计

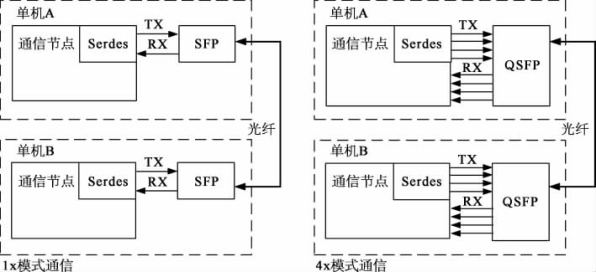

1)单机间通信设计

考虑到Serdes接口电路中接收端和发送端间只有一个低容值的AC耦合电容,目前市面上没有专用的SRIO电接口芯片,因此,为避免不同单机的收发接口形成无防护直连,采用光接通信方案实现单机间高速互连。光纤通信具有高速率、抗干扰、传输距离长的优点,非常适合传输高速串行数据,而且市面上有多款SFP(1x)、QSFP(4x)光模块与GTX接口兼容,可与RapidIO接口直连完成数据收发的光电转换。常见的互连方案如图4- 26所示。

图4-26 基于RapidIO和光电传输的单机高速互连

光电通信的光模块和Serdes电接口可以构成光电通信接口模块,为单机提供长距离、高速率的高速串行通信,根据设计需求选用的光纤和光模块即可实现空间信息系统的机间高速互连。

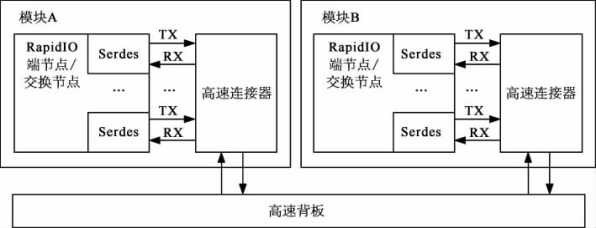

2)板间通信典型设计

单机内部模块间的高速互连可以通过两个Serdes直连实现,板间传输的传输线长度通常不超过0.5 m,根据传输损耗Acond计算,确保传输线损耗不超过3 dB的情况下,板间的高速串行通信可通过高速背板直连的方式实现。

通常高速板间通信链路由高速背板和高速内总线连接器组成,板间高速串行通信链路如图4-27所示,高速背板可采用高速板材、特殊工艺等方式提高高速串行信号传输的信号完整性。

图4-27 板间高速串行通信链路

3)板内通信典型设计

单板内部具有多个高速运算单元,并且高速运算单元间具有高速通信需求时,根据传输损耗Acond(单位为dB)计算,确保传输线损耗不超过3 dB的情况下,可以采用高速串行通信实现高速运算单元的高速互连架构。板内高速串行通信链路如图4- 28所示。

图4-28 板内高速串行通信链路