7.3.2 FPGA硬件设计

7.3.2.1 供电设计

FPGA供电设计应考虑芯片各挡电源的正确性及稳定性、各挡电源间的上电时间要求、FPGA器件的上电和掉电顺序、电源功耗及启动电流等设计。FPGA供电设计包括如下方面:

(1)额定电压。供电电压设计应依据FPGA芯片手册进行,须满足芯片实际运行要求,包括电压稳定范围、电源负载裕度等。

(2)启动电流瞬变。其受以下因素影响:开关电源周期、温度、电源爬升率、累积辐照时间、加电顺序等。对某些器件来说,这种电流可以相当大,常常高达几安培。在这种情况下,如果电源系统不给电流设置足够的稳定容限会很危险,因为启动期间如果电流不够,就会造成初始化失败、电源器件停机、陷入无限循环、系统锁定或死锁。

(3)上电/掉电顺序。一般意义上,为了实现接口信号的冷备份或避免上电时I/O信号的异常,建议VCCA与VCCI同时上电或VCCA先于VCCI上电。尽量避免使用具有供电顺序要求的器件,如果存在供电顺序要求,则应标出这些要求。由于FPGA上电过程中管脚上会存在毛刺信号,将会影响系统功能的重要输出信号如指令驱动信号,这时必须采用隔离手段,一般做法是使用164245芯片进行隔离,并设计164245芯片使能的复位延时电路,延时复位时间至少大于2倍VCCA上电时间。

(4)电压上升时间。VCCA的上升时间决定了反熔丝型FPGA接口的激活时间。一般来说,I/O管脚属性只有在VCCA即将达到额定值时才会被激活为用户定义的I/O属性,因此缩短VCCA的上升时间可以快速激活FPGA的I/O管脚。

(5)功耗估算及热计算。FPGA的芯片总功耗主要由静态功耗及动态功耗构成。动态功耗与资源使用、时钟频率及输入输出相关,可根据实际设计情况来估算。同时在宇航应用中应考虑FPGA芯片的热设计,根据估算的芯片功耗可计算出芯片的结温,并确定能否满足热设计要求。若计算出来的芯片结温无法满足热设计要求,则需要采取相应散热措施,如增加金属导热片等。

7.3.2.2 上电复位设计

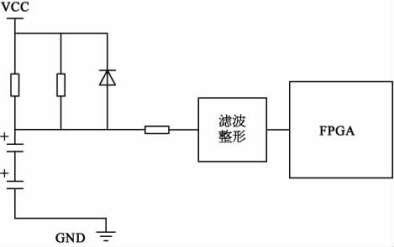

FPGA器件初始加电时需要经过一个上电过程,上电复位才能够起作用,因为FPGA器件上电时间受到上电速度影响较大,所以上电复位时间表必须有设计余量。复位信号宽度必须覆盖FPGA的上电时间、加载时间、产生该FPGA系统时钟的任何振荡器或其他电路的上电时间。采用复位设计时,必须保证FPGA上电稳定后复位信号才能消失,否则复位无效。一般做法是在硬件上加入RC延时复位电路,建议延时时间不少于200 ms,并对该信号进行滤波和整形后接入FPGA的普通I/O管脚,FPGA内部逻辑使用该信号作为复位信号。反熔丝型FPGA上电复位的典型电路设计如图7- 8所示。

7.3.2.3 I/O接口设计

1)设计原则

FPGA一般通过接口电路作为内部逻辑与应用环境之间的耦合逻辑使用,设计师应注意接口的输入和输出。必须遵守FPGA输入的电平标准,以及输入信号的上升和下降时间要求。FPGA启动期间,由于各种原因会在输出上产生毛刺信号,作为一条原则,必须保证正常工作期间任何输出不会产生毛刺信号。因此,建议所有输出直接由触发器驱动,或者由在工作阶段控制信号稳定的多路选择器来驱动。

图7-8 反熔丝型FPGA上电复位的典型电路设计

应当指出的是,三模冗余触发器的组合表决器经常会导致毛刺信号,可以通过接收端的滤波器,减轻毛刺信号的影响,但这样的设计会妨碍设计的可重用性。必须保证FPGA内外都不会出现总线竞争。上电和复位期间尤其要格外注意。此外,让总线节点悬空会增加功耗,应当避免。

2)特殊管脚的处理

在电路板设计过程中需要仔细考虑FPGA的特殊管脚,必须确保所有未用管脚严格遵守FPGA制造商指南,并进行正确端接。具体包括如下:

(1)未用用户管脚或I/O。其应保持不与内部逻辑连接,任何未用管脚都可以通过布局与布线软件被编程为输出。标记为未连接(或NC)的管脚应保持不连接。除非特殊情况,不允许将I/O或NC管脚直接接电源或接地。要正确记录未用管脚的状态,并纳入设计报告中。

(2)JTAG接口。许多现代数字集成器件具有JTAG接口,JTAG管脚与用户I/O之间不存在共用。TCK、TDI、TMS和TRSTB输入在不用时应通过一个电阻接地,TDO输出应保持不连接。

(3)同步切换输出(SSO)。设计时应限制可以同时切换的输出引脚数量。对于切换速度快、引脚数量大、交流和直流噪声容限低的器件,地噪声可能是一个严重问题。需要考虑减小地弹的若干因素和采取相应的解决措施。(https://www.daowen.com)

(4)测试接口。根据具体情况处理,由于它们与测试设备相连,必须严格遵守厂家说明。

(5)配置引脚。严格按照数据手册仔细检查每个配置引脚。某些引脚的内部上拉电阻非常高,可能会被板级高速信号翻转,需要采用保护性设计以确保这些引脚的电平是可靠的。某些配置引脚可能会偶尔漂移导致器件处于错误状态,设计中应考虑编程类特殊引脚必须适当端接。

(6)信号端接。包括以下要求:①保证信号妥善端接;②对于时钟信号必须保证在阈值上平滑跃迁;③多数厂家对于信号的走线间距有严格限制;④提前对端接电阻进行规划;⑤在原理图设计中确保接口端接正确。

(7)三态总线。在主动驱动三态中不能存在任何重叠,这会浪费功率、产生不必要的噪声并增大元件应力。保证最坏情况下总线驱动器之间的关闭时间,不要让总线浮空或跃迁时间较慢,否则会增加功率和噪声,并对可靠性产生不利影响。

(8)输入跃迁时间。部分高速或现代器件对输入跃迁时间有十分严格的限制,如果不能满足这些要求,就会产生波动、多时钟或损坏。对于具有跃迁时间的数百毫微秒的现代元件,不能采用简单上拉电阻或下拉电阻;使用总线保持或软锁电路,有助于降低功率。

(9)短接输出。不能为了增加板上驱动而短接输出。因为若开关速度不匹配,则会损坏元件。如果短接输出,那么两个输出应来自同一集成电路。

(10)引脚分配。引脚分配应谨慎和认真规划。注意考虑针对同步开关输出、抗噪和静音的设计。时钟和关键信号可以按最短线路在电路板上布线,使串扰最小,并可将其包围或安排在接地引脚附近。

(11)混合电压界面、直流兼容性和噪声容限。当不同种器件甚至同一厂家不同族器件混用时,一定要保证这些器件可靠运行,并具有足够的噪声容限。目前元件一般可以具有多个输入电压,如1.5 V、1.8 V、2.5 V、3.3 V、5.0 V。最新器件也兼容各种I/O标准,编程能力极强,但是由于其特点不明显,因此应对器件的I/O兼容性仔细验证。

(12)电源切换与冷备份。设计具有单独供电模块的系统时,无论对于冗余模式还是节电模式,都要相当小心。许多CMOS器件在掉电时,通过其固有二极管或ESD保护二极管的阻抗较低;而其他一些具有冷备份输入的器件可能具有适合工作的较高阻抗。对于可编程器件而言,例如选择3.3 V PCI兼容性,因为钳位二极管的启用,所以造成冷备份器件不再具有较高的阻抗。虽然许多双极器件兼容冷备份结构,但是某些器件通过输出造成到VCC的潜通路。

7.3.2.4 工艺设计

FPGA的电装工艺设计分为手工电装和回流焊两种方法,其中手工电装按照《静电放电敏感器件安装工艺技术要求》(QJ 2711A—2014)的规定进行,回流焊工艺的关键是控制温度曲线,最优化的参数才能得到最好的焊接效果。设置回流焊温度曲线的依据如下:

(1)根据使用焊锡膏的温度曲线。不同金属含量的焊锡膏有不同的温度曲线,应按照焊锡膏生产厂商提供的温度曲线设置具体产品的回流焊温度曲线。

(2)根据PCB的材料、厚度、是否多层板和尺寸大小等。

(3)根据表面组装板搭载元器件的密度、元器件的大小及有无BGA等特殊元器件。

(4)根据设备的具体情况,如加热区的长度、加热源的材料、回流焊炉的构造和热传导方式等。

回流焊设置温度曲线中需要注意以下几点:

(1)器件本身最高的温度220℃,而引线和管脚的最低温度应为205℃。

(2)预热烘干阶段的温度爬升速度为2~4℃/s。

(3)预热后应该在95~180℃温度下保持120~180 s。

对于扁平封装的反熔丝型FPGA,必须在程序烧录后才能进行芯片管脚成型和焊接。不同封装的反熔丝型FPGA芯片都应该进行工艺加固设计,包括扁平封装芯片的加固工艺及BGA(或CCGA)封装芯片的加固工艺等。