3.6.4 技术特征

1)寄存器组织形式

MIPS寄存器主要包括通用寄存器、特殊寄存器、浮点寄存器。MIPS 32体系结构实现了32个32位的通用寄存器,为第0号寄存器到第31号寄存器,这些寄存器可供指令使用,其中两个寄存器较为特殊:第0号通用寄存器不论指令向里面写入什么值,读出的总是0;而第31号通用寄存器通常被子程序调用指令用来存储返回地址。

尽管除了第0号寄存器外,硬件并没有对寄存器的使用方法进行规定,但是在实际应用时还是需要约定一些规则。硬件并不关心这些规则,不过,如果需要移植其他子程序、编译器或操作系统,那么最好遵循这些惯例。

MIPS体系结构定义了以下3个特殊寄存器:

(1)PC:程序计数器,保存当前执行程序的地址。

(2)LO:保存乘法指令低位结果或除法指令的商。

(3)HI:保存乘法指令高位结果或除法指令的余数。

MIPS体系结构还定义了以下3种浮点寄存器:

(1)32个32位浮点寄存器(FPR)。

(2)5个FPU控制寄存器,用于识别和控制FPU。(https://www.daowen.com)

(3)8个浮点条件代码,它们是FCSR寄存器中的一部分。

除了32个通用寄存器、3个特殊寄存器、45个浮点寄存器外,在系统控制协处理器中也有很多特权寄存器,用于高速缓存、例外中断情况处理等方面。

2)存储系统组织形式

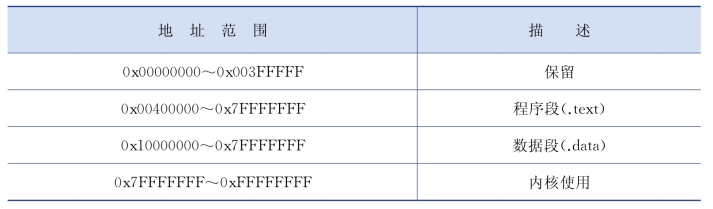

MIPS 32TM支持数据在存储器中可以小端格式或大端格式进行存储,在MIPS 32TM体系结构中,用户可访问的存储空间地址范围从0x00000000~0x7FFFFFFF,共计2 GB。0x7FFFFFFF向下增长至0x10000000,可作为堆栈段。具体见表3- 5。

表3-5 MIPS 32TM地址空间划分

数据段又分为静态存储区和动态存储区,分别用于存储全局变量和动态分配的变量。一般而言,取$gp=0x10008000,位于0x1000000~0x10007FFF的一段32 KB空间用作静态存储区,动态存储区从0x10008000向上增长,最高可达0x7FFFFFFF。当以$gp为基地址时,lw和sw指令可向上或向下各寻址32 KB的空间,共计64 KB。堆栈段从0x7FFFFFFF开始向下增长,最低可增长至0x10000000,用于存储。对于MIPS而言,使用Havard架构,默认程序总是0x00000000启动,数据总是从0x00040000开始存储,而且所有外设(如串口)均映射在数据存储空间,即使用存储器映射IO的形式。配置程序段和数据段的地址是通过设置链接器(linker)的脚本(script)完成的。

3)中断和异常管理

(1)MIPS的异常机制。MIPS对异常处理的方法是给异常分配一些类型,由软件给它们定义一些优先级,然后由同一个入口进入异常分配程序,在分配程序中根据类型及优先级确定该执行哪个对应的函数。这种机制对两个或几个异常同时出现的情况也是适合的。

异常处理函数执行完成后,会回到异常分配函数那里。异常分配函数中有一个eret指令,用于回归原来被中断的程序继续执行;eret指令会把中断响应打开,并把状态级由kernel转到user级,并返回原地址继续执行。

(2)中断。MIPS CPU有8个独立的中断位(在Cause寄存器中),其中,6个为外部中断、2个为内部中断(可由软件访问)。一般来说,片上的时钟计数/定时器,会连接到一个硬件位上去。在软件中实现中断优先级的方案,给各种中断定优先级;CPU在运行时总是处于某个优先级(即定义一个全局变量);中断发生时,只有等于高于CPU优先级的中断优先级才能执行(如果CPU优先级处于最低,那么所有的中断都可以执行);同时有多个中断发生时,优先执行优先级最高的那个中断程序。