7.2.3 选型参考

各类宇航型号的FPGA芯片应根据具体情况进行选型。由于宇航产品具有长寿命、不可维修、抗辐射等高可靠性要求,对FPGA芯片的选型需要约束。在对FPGA芯片选型前,需要进行设计需求分析、设计预估、选型参考、辐射能力确认和开发软件选择等,最后形成芯片选型结论。

7.2.3.1 一般选用原则

FPGA芯片的选型,应根据设计需求分析和设计预估的结果,并综合考虑宇航器件的厂商、供货渠道、芯片主要参数、外围器件和成本等因素后完成。

1)芯片选型原则

宇航型号用FPGA芯片的类型主要有反熔丝型、SRAM型和Flash型三大类,一般来说,选择芯片类型时参照以下原则:

(1)在满足需求的情况下优先选用小容量器件,优先选用反熔丝器件,加载芯片优先选用PROM芯片;实现安全等级较高的关键功能,建议选用反熔丝型FPGA芯片。

(2)优先选用经在轨运行考核稳定的FPGA芯片。

(3)反熔丝型FPGA芯片和配置PROM芯片的选型,必须同步考虑烧录设备和烧录软件的支持。

(4)SRAM型FPGA建议采取一定的抗单粒子翻转措施,如三模冗余设计、全局/局部刷新。

(5)建议采用货源充足的供应商和产品系列,以提高产品的生命周期:反熔丝型FPGA推荐使用ACTEL公司的SX-A系列、AX系列,SRAM型FPGA推荐使用Xilinx公司的Virtex系列。

(6)在产品定型和批量生产时,考虑将FPGA芯片设计更改为ASIC芯片。

2)芯片资源选型原则

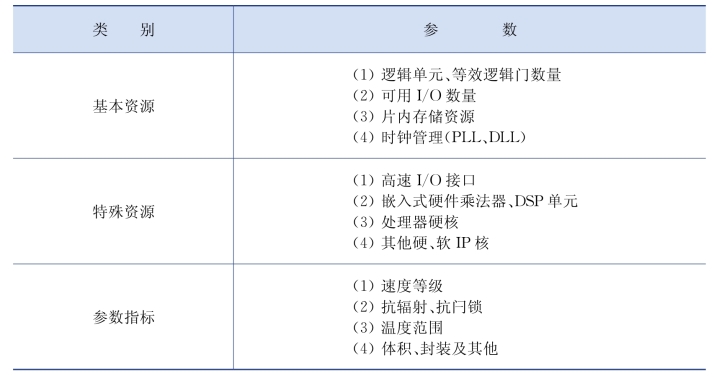

FPGA芯片选型时,须根据设计预估的结果,综合考虑FPGA芯片的基本资源、附加资源、速度及封装等其他指标。FPGA芯片的主要参数及指标见表7- 4。

表7-4 FPGA芯片的主要参数及指标

芯片资源选型原则如下:

(1)一般降额要求:逻辑资源70%,I/O资源80%,布线资源70%,速度80%。

(2)输入输出(I/O)支持多种电气接口标准。

(3)在满足应用需求的情况下,优先选用速度等级低的器件。

(4)芯片封装优先选用低密度的CQFP封装器件,若产品的输入输出引脚需求超出CQFP封装数量时,则优先选用CCGA封装器件。

3)外围器件配置原则

SRAM型FPGA芯片需要根据资源特性选择合适的配置信息存储芯片,基本原则如下:

(1)优先选择FPGA芯片手册上推荐的配置存储芯片。

(2)设计开发阶段应选择与正样PROM配置芯片封装兼容的EEPROM配置芯片。

(3)初样产品采用转接设计,采用军级的PROM配置芯片进行验证。

(4)正样产品选择具有抗辐射指标的PROM配置芯片。

7.2.3.2 反熔丝型FPGA器件一般选型原则

反熔丝型FPGA器件一般选型原则如下:(https://www.daowen.com)

(1)宇航用反熔丝型FPGA在满足逻辑资源使用需求的情况下优先选用SX-A系列器件。

(2)在满足I/O资源使用情况下优先选择QFP封装器件。

(3)在满足运行速度要求的情况下优先选用速度等级低的器件。

(4)优先选用在轨运行稳定的FPGA器件,如A54SX32A-CQ208B、A54SX72A-1CQ208B、AX500-1CQ208M、AX2000-1CQ352M、AX2000-1CQ624M。

7.2.3.3 SRAM型FPGA一般选型原则

根据型号任务的需求,SRAM型FPGA一般选型原则如下:

(1)当国产SARM型FPGA满足使用要求时,应优先选择国产FPGA。

(2)根据应用要求选择相应质量等级的器件。

(3)根据宇航任务选择抗电离总剂量能力和抗单粒子效应能力满足宇航型号任务需要的器件。

(4)根据器件研制情况,选择具有稳定生产、制造工艺成熟、具有持续供货能力的器件。

(5)应加强FPGA的品种和生产厂点压缩,尽量选用以前具有使用经历的产品。

(6)选型时要考虑开发软件的支持情况。

(7)根据应用需求确定硬件资源,硬件资源一般包括逻辑资源、I/O资源、布线资源、DSP资源、存储器资源、锁相环资源、串行收发器资源和硬核微处理器资源等。

(8)根据应用需求选取相应的速度等级。

(9)根据应用选择适应的封装形式。

7.2.3.4 Flash型FPGA一般选型原则

Flash型FPGA在航天领域应用经验较少,后续应用时,选型原则参考7.2.3.1节一般选用原则。

7.2.3.5 兼容性验证

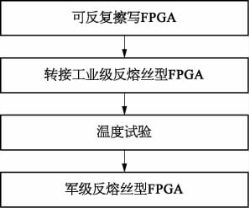

宇航星载计算机正样产品应选用有抗辐射能力的宇航级FPGA芯片,而设计开发阶段考虑降级使用。对于经飞行验证的FPGA型号可以参考成熟电路,可不在初样阶段进行验证。对于首次采用的FPGA芯片,则必须在初样阶段完成正样产品状态的兼容性验证。而对于反熔丝型FPGA芯片的产品,在设计开发阶段可选择管脚兼容的SRAM型(或Flash型)FPGA芯片替代,完成功能验证。初样产品建议使用与正样产品一致的高等级反熔丝型FPGA芯片进行功能、性能考核。反熔丝型FPGA产品硬件设计流程如图7- 6所示。

图7-6 反熔丝型FPGA产品硬件设计流程

FPGA产品硬件设计建议如下:

(1)建议调试时选用同一公司可反复擦写的FPGA。

(2)代码编写建议采用HDL代码,以利用不同FPGA平台的移植。

(3)两种不同类型的FPGA布线延时参数不同,对利用器件延时参数的设计应进行适应性论证。一般情况下,反熔丝型FPGA延时略大。

(4)可反复擦写的FPGA寄存器、计数器等上电初态为0,而反熔丝型FPGA上电初态为随机数,应注意初态设计。

(5)不同类型的FPGA上电或配置时,配置时间和配置期间IO状态等各不相同,设计应均能适应。