2.3.2 组合逻辑电路的设计

组合逻辑电路的设计是其电路分析的逆过程。设计问题的已知条件是给出了欲实现的逻辑功能,设计的目的是确定实现所给逻辑功能的具体组合逻辑电路。

组合逻辑电路设计的基本步骤如下:

(1)列出真值表。分析欲实现的逻辑功能的因果关系,把引起事件的原因作为输入逻辑变量,把事件的结果作为输出逻辑变量,并把输入/输出变量分别用字母表示,每个输入变量可以取值1或者0,根据输入/输出的因果关系列出真值表。

(2)写出逻辑函数表达式。依据已经列出的真值表写出对应的逻辑函数表达式。

(3)简化或变换逻辑函数表达式。

(4)画出逻辑电路图。根据化简或变换后的逻辑函数表达式以及所选用的逻辑器件画出逻辑电路图。

对于一个特定的逻辑函数,实现其逻辑功能的电路不是唯一的。当实现途径有多种选择时,设计者应考虑在保证逻辑功能的前提下,在多种可能的实现途径中,选择较好的电路实现形式。比如说所选用的逻辑器件数量及种类最少,而且器件之间的连线最简单;以确保提高其电路的工作稳定性,功耗较低。

【例2.18】 设计一个三人表决器,结果为少数服从多数。

解:①根据设计要求建立该逻辑函数的真值表。

设三人的意见为变量A、B、C,表决结果为函数L。对变量及函数进行如下状态赋值:对于变量A、B、C,设同意为逻辑1,不同意为逻辑0;对于函数L,设事件通过表决则逻辑值为1,没通过则设定逻辑值为0。

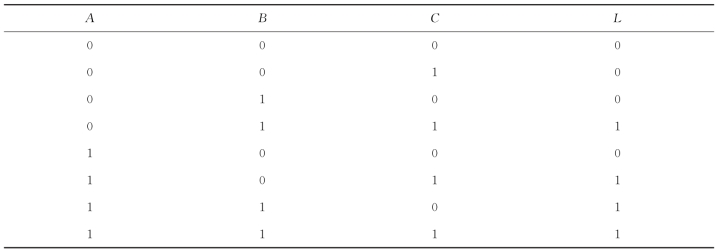

列出真值表,如表2.16所示。

表2.16 真值表

②由真值表写出逻辑表达式并化简:

![]()

但该表达式并不是最简逻辑表达式。

经过逻辑化简后得到:

L=AB+AC+BC

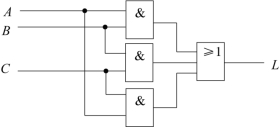

③画出逻辑电路图。

根据逻辑表达式L=AB+AC+BC,绘制逻辑电路图,如图2.23所示。

图2.23 逻辑电路图

至此,逻辑电路设计完成。

【例2.19】 设计一个交通信号灯工作状态检测电路。

分析:在正常工作状态下,任何时刻点亮的只能是红、黄、绿中的一种。当出现其他五种点亮状态时,电路发生故障,要求电路发出故障信号,以提醒维护人员前去修复。

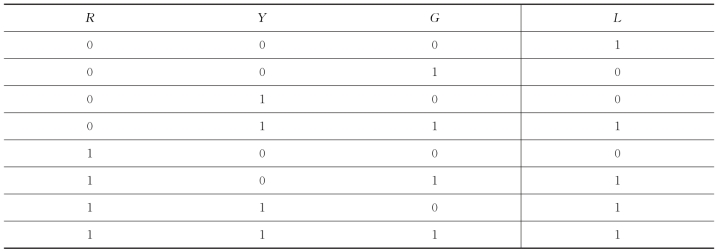

解:①根据设计要求,列出真值表,如表2.17所示。

表2.17 真值表

②写出逻辑函数表达式:

③化简逻辑函数表达式:

![]()

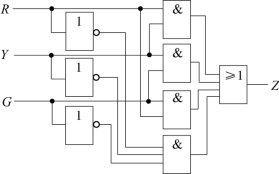

④画出逻辑电路图,如图2.24所示。

图2.24 交通信号灯逻辑电路图

【例2.20】 设计一个电话机信号控制电路。电路有I 0(火警)、I 1(盗警)、I 2(日常业务)三种输入信号,通过排队电路分别从L 0、L 1、L 2输出,在同一时间只有一个信号通过。如果同时有两个以上信号出现时,应首先接通火警信号,其次为盗警信号,最后是日常业务信号。试按照上述轻重缓急设计该信号控制电路(要求用与非门实现)。

解:①列真值表。

对于输入,设有信号为逻辑“1”;没信号为逻辑“0”。

对于输出,设允许通过为逻辑“1”;不允许通过为逻辑“0”。

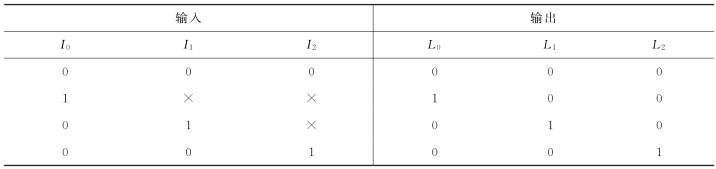

列出真值表,如表2.18所示。

表2.18 真值表

说明:在有些逻辑函数中,输入变量的某些取值组合不会出现,或者一旦出现,逻辑值可以是任意的。这样的取值组合所对应的最小项称为无关项、任意项或约束项。在化简时根据需要取值可以为1也可以为0;在真值表中用X 表示。

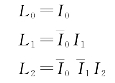

②由真值表写出各输出的逻辑表达式:

(https://www.daowen.com)

(https://www.daowen.com)

这三个表达式已是最简,无须化简。但需要用非门和与门实现,且L 2需用输入端与门才能实现,故不符合设计要求。

③根据要求,将上式转换为与非表达式:

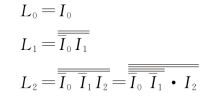

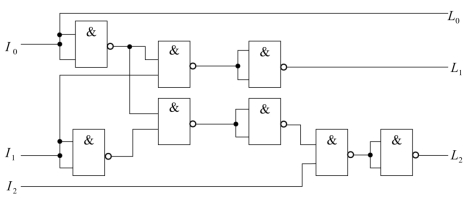

④画出逻辑电路图,如图2.25所示。

图2.25 逻辑电路图

可见,在实际设计逻辑电路时,有时并不是逻辑表达式最简单就能满足设计要求,还应考虑所使用集成器件的种类,将表达式转换为能用所要求的集成器件实现的形式,并尽量使所用集成器件最少,就是设计步骤框架中所说的最合理表达式了。

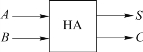

【例2.21】 设计一个半加器。所谓半加器,是指不考虑低位有无向本位的进位,只将两个本位数相加的运算。其中A、B表示两个加数,S 表示相加后的和,C 表示相加后高位产生的进位。半加器逻辑框图如图2.26所示。

图2.26 半加器逻辑框图

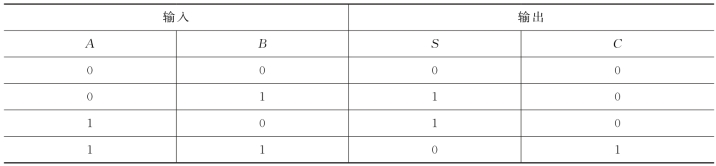

①列真值表如表2.19所示。

表2.19 真值表

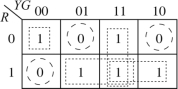

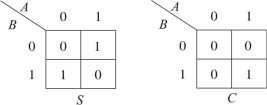

图2.27 卡诺图

②简函数。

根据真值表画S 和C 的卡诺图,如图2.27所示。

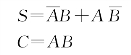

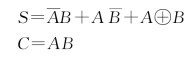

由卡诺图得:

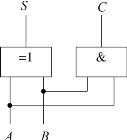

③根据给定的逻辑门写出表达式。

用异或门和与门:

④画逻辑电路图,如图2.28所示。

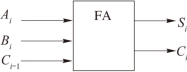

【例2.22】 设计一个全加器。所谓全加器,就是能对两个一位二进制数相加,并加上低位来的进位,形成“和”及“进位”的逻辑电路。它的逻辑框图如图2.29所示。

图2.28 逻辑电路图

图2.29 全加器的逻辑框图

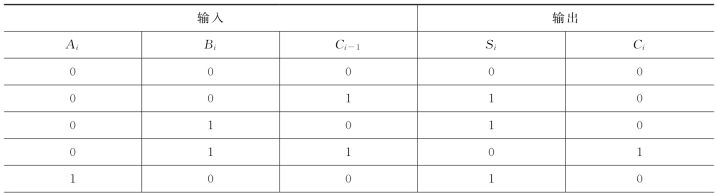

①列真值表,如表2.20所示。

表2.20 真值表

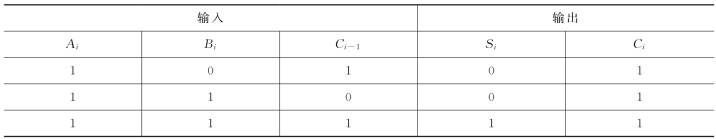

续表

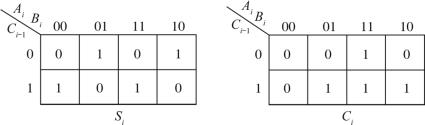

②化简函数。

根据真值表画Si和C i的卡诺图,如图2.30所示。

图2.30 卡诺图

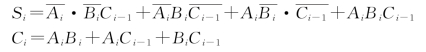

由卡诺图得:

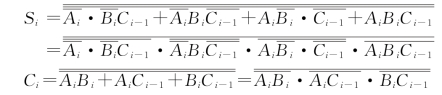

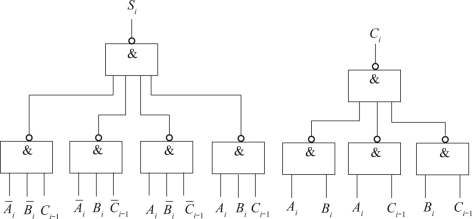

③根据给定的逻辑门写出表达式:用与非门实现全加器。将Si和C i由“与或”式变成“与非”式:

④逻辑电路图(与非门实现)如图2.31所示。

图2.31 逻辑电路图