6.3.3 半导体随机存储器

用大量的位存储单元构成存储阵列,存储大量的信息,再通过读写电路、地址译码电路和控制电路实现对这些信息的访问,这样就构成了存储器芯片。半导体RAM 存储器芯片主要有静态存储器芯片和动态存储器芯片两种。静态存储器芯片的速度较高,但它的单位价格(即每字节的价格)较高;动态存储器芯片的容量较高,但速度比静态存储器慢。

1.静态存储器芯片(SRAM)的结构和工作原理

静态存储器芯片由存储体、读写电路、地址译码和控制电路等部分组成。

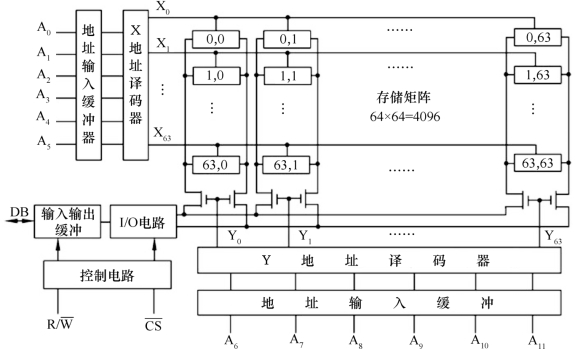

(1)储体(存储矩阵):由大量的存储位单元构成的阵列组成。阵列中包含很多行,每行由多列存储单元构成。阵列中用行选通线选择一行中的存储单元,再用列选通线选择一行中的某一个存储单元将数据读出。4096字节静态RAM 芯片结构如图6.8所示,4096个存储单元排成64×64的矩阵,由行选通线(X)和列选通线(Y)来选择所需用的单元。

图6.8 4096字节静态RAM 芯片结构

(2)地址译码器:地址译码器的输入信号线是访问存储器的地址编码,地址译码器把用二进制表示的地址转换成驱动读写操作的选择信号。地址译码有两种方式:一种是单译码方式,适用于小容量存储器;另一种是双译码方式,适用于容量较大的存储器。

在单译码方式下,地址译码器只有一个,其输出选中某个地址对应的字节或字单元。当地址位数较多时,单译码结构的输出线数目较多。如4096字节的存储器,地址位数为12,则单译码结构要求译码器具有4096根输出线,这在实现上是有困难的。

在双译码方式下,地址译码器分为X 和Y 两个译码器,分别用于产生一个有效的行选通信号和一个有效的列选通信号,行选通线和列选通线都有效的存储单被选中。这种方式每个译码器都比较简单,可减少数据单元选通线的数量。如存储器地址位数为12,分成6位行地址送入X译码器,6位列地址送入Y 译码器。2个译码器的输出线总数为128根。

(3)驱动器:由于选通信号线要驱动存储阵列中的大量单元,因此需要在译码器输出后加一个驱动器,用驱动输出的信号去驱动连接在各条选通线上的各存储单元。

(4)I/O 电路:I/O 电路(输入/输出电路)处于数据总线和被选中的单元之间,用以控制被选中的单元读出或写入,并具有放大数据信号的作用。数据驱动电路对读写的数据进行读写放大,增加信号的强度,然后输出到芯片外部。

(5)片选控制:产生片选控制信号,选中芯片。

(6)读/写控制:根据CPU 给出的信号,控制被选中存储单元做读操作还是写操作。

以上介绍的是存储器芯片的物理结构。在逻辑上,存储芯片的容量经常用字数M×位数N 表示。字数M 表示存储芯片中的存储阵列的行数,位数N 表示存储阵列的列数,即数据宽度。存储器芯片的字数影响到芯片所需的地址线数量,数据宽度则对应着芯片的数据线数量。如1024×4的存储芯片,有10条地址线(210=1024)和4条数据线。

静态存储器芯片的引脚接口信号通常有如下几种:

Address:地址信号,一般表示为A 0、A 1、A 2…

Data:数据信号,一般表示为D0、D1、D2…

![]() :芯片选择信号,低电平时说明该芯片被选中。

:芯片选择信号,低电平时说明该芯片被选中。

![]() :写允许信号,低电平表示写操作。(https://www.daowen.com)

:写允许信号,低电平表示写操作。(https://www.daowen.com)

![]() :读允许信号,低电平表示读操作。

:读允许信号,低电平表示读操作。

不同的存储芯片产品控制信号名称会有差别,信号的有效电平也有差别。如有的芯片上片选信号常表示为CS(高电平有效)或者![]() (芯片许可,Chip Enable)。有些芯片上读写信号合并为

(芯片许可,Chip Enable)。有些芯片上读写信号合并为![]() ,低电平表示写操作,高电平表示读操作。有些芯片上数据线是单向的,用Din表示数据输入信号线,用Dout表示数据输出信号线。

,低电平表示写操作,高电平表示读操作。有些芯片上数据线是单向的,用Din表示数据输入信号线,用Dout表示数据输出信号线。

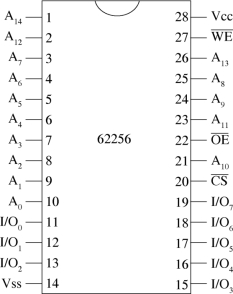

如静态MOS存储器芯片62256,芯片引脚如图6.9所示。62256容量为32 KB,即32 K个存储字单元,每个字单元8位数据宽度。芯片地址引脚为A0~A14;数据引脚为I/O0~I/O7;片选信号为![]() ,低电平有效;读/写控制信号为

,低电平有效;读/写控制信号为![]() ,低电平为写操作,高电平为读操作。

,低电平为写操作,高电平为读操作。

图6.9 静态MOS存储器芯片62256芯片引脚

2.动态存储器DRAM 芯片的结构和工作原理

用动态存储单元构成阵列,加上控制电路制作成动态存储器DRAM 芯片。但是由于动态RAM 芯片容量一般比较大,所以地址线数量较多。为了减少地址线数量,将地址分成行地址和列地址,分成两次输入芯片。两次地址的输入分别由芯片的地址选通信号![]() 和

和![]() 控制,其中

控制,其中![]() 是行地址选通信号,低电平有效,用于选中存储阵列中的一行;

是行地址选通信号,低电平有效,用于选中存储阵列中的一行;![]() 是列地址选通信号,低电平有效,用于选中存储阵中的一列。另外,DRAM 芯片也具有读/写控制信号。

是列地址选通信号,低电平有效,用于选中存储阵中的一列。另外,DRAM 芯片也具有读/写控制信号。

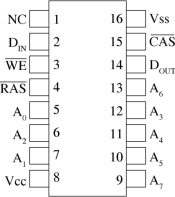

动态存储芯片4164芯片引脚如图6.10所示。

4164的容量为64 K×1位。芯片地址引脚为A 0~A 7;数据输入引脚为Din,数据输出引脚为Dout;行地址选通信号是![]() ,列地址选通信号是

,列地址选通信号是![]() ,低电平有效;读/写控制信号为

,低电平有效;读/写控制信号为![]() ,低电平为写操作,高电平为读操作。

,低电平为写操作,高电平为读操作。

图6.10 动态存储芯片4164芯片引脚

行地址在![]() 有效前到达芯片的地址输入端,经过一段访问时间后,将行地址输入到芯片内;然后列地址到达,使

有效前到达芯片的地址输入端,经过一段访问时间后,将行地址输入到芯片内;然后列地址到达,使![]() 有效一段延时时间,将列地址输入到芯片内,这时启动芯片内部的读/写操作。在

有效一段延时时间,将列地址输入到芯片内,这时启动芯片内部的读/写操作。在![]() 有效时根据

有效时根据![]() 的电平状态,进行读操作或者写操作。若为读操作,数据将从数据线上输出;若为写操作,外部提供的写入数据输入到芯片中。不论是读操作还是写操作,

的电平状态,进行读操作或者写操作。若为读操作,数据将从数据线上输出;若为写操作,外部提供的写入数据输入到芯片中。不论是读操作还是写操作,![]() 和

和![]() 的有效时间都必须保持一定的长度,并且在撤销后到下一次有效必须经过一段时间。

的有效时间都必须保持一定的长度,并且在撤销后到下一次有效必须经过一段时间。

3.大容量芯片简介

现在计算机中使用的都是大容量的动态芯片,所以除了介绍以上小容量的芯片外,简单介绍一下大容量的芯片,以三星的8 GB DDR4 B-die为例。它属于SDRAM(SDRAM 是Synchronous Dynamic Random Access Memory 同步动态随机存储器的简称)。有型号K4A8G045WB(芯片组织为128 Mbit×4)和型号K4A8G085WB(芯片组织为64 Mbit×8)两种。该同步器件可实现高达2666 MB/s/pin(DDR4-2666)的高速双数据传输速率,适用于一般应用。

该芯片设计符合关键的DDR4 SDRAM 功能,如CAS,可编程CWL,内部(自)校准,使用ODT 引脚和异步复位的芯片终端。

所有的控制和地址输入都与一对外部提供的差分时钟同步。输入在差分时钟的交叉点锁存(CK 上升沿和![]() 下降沿)。所有I/O 以源同步方式与一对双向故障码(DQS和

下降沿)。所有I/O 以源同步方式与一对双向故障码(DQS和![]() 同步)。地址总线用于以

同步)。地址总线用于以![]() /

/![]() 复用方式传送行、列和页地址信息。DDR4器件采用单个1.2 V(1.14 V~1.26 V)电源和1.2 V(1.14 V~1.26 V)工作。

复用方式传送行、列和页地址信息。DDR4器件采用单个1.2 V(1.14 V~1.26 V)电源和1.2 V(1.14 V~1.26 V)工作。

8 GB B-die DDR4 SDRAM 1×4封装引脚排列如图6.11所示,顶视图如图6.12所示,78ball FBGA(78点细间距球栅阵列)封装。

8 GB B-die DDR4 SDRAM 1×4封装引脚排列如图6.13所示,顶视图如图6.14所示,78ball FBGA(78点细间距球栅阵列)封装。