5.2 CPU的基本功能和组成

CPU 中主要包含运算器、控制器以及一系列寄存器。

1.运算器

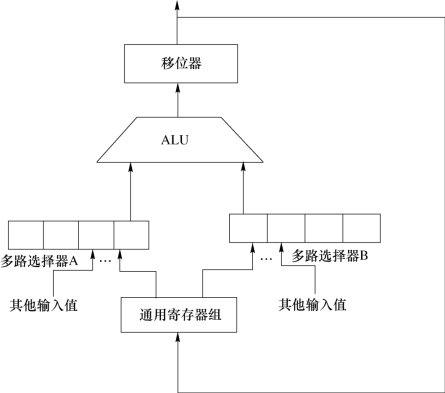

运算器的主要功能是对数据进行加工处理,包括通用寄存器组、算术逻辑单元(Arithmetic Logic Unit,ALU)、多路选择器及移位器。

其中运算器的核心部件是ALU。因为ALU 能完成整数的加、减、乘、除等算术运算,与、或、非、异或等逻辑运算,以及数据的移位运算等。浮点数据的运算是由专门的浮点运算器完成的,它有可能包含在CPU 中,也有可能作为单独的协处理器。

运算器内设有若干通用寄存器,构成通用寄存器组,用于暂时存放参加运算的数据和某些中间结果。通用寄存器组对用户是开放的,用户可以通过指令去使用这些寄存器。在运算器中用来提供一个操作数并存放运算结果的通用寄存器称为累加器。多路选择器可以接收通用寄存器组提供的数据,也可以接收其他的数据,如外部送入的数据等。移位器对ALU 的运算结果进行输出控制。如可以将运算结果左移一位(相当于乘以2)、右移一位(相当于除以2)等,如图5.1所示。

图5.1 运算器的组成

2.CPU 中的寄存器

寄存器组是指CPU 在运算或控制的过程中需要暂时存储信息的存储器集合。CPU 中的寄存器主要可分为三类:处理寄存器、控制寄存器及主存接口寄存器。

(1)处理寄存器

①通用寄存器:这是一组提供给用户访问的、具有多种功能的寄存器。在指令系统中为这些寄存器编了编号,用户可以利用这些寄存器编号编写程序。本书在第4章已经介绍过,这里不再赘述。

②暂存器:用来暂存操作数或中间结果,与通用寄存器的区别是在指令系统中没有给这些暂存器编写编号,因此对用户是透明的,不能访问。(https://www.daowen.com)

(2)控制和状态寄存器

①程序计数器PC:程序计数器又称指令计数器或指令指针IP,该寄存器的作用是保存下一条即将执行指令的地址,以保证CPU 在当前指令执行完成后,能自动确定下一条指令的地址。

②指令寄存器:指令寄存器存放的是现行指令,CPU 从内存中取出指令送到指令寄存器中,然后进行指令的译码和执行工作。

③程序状态字寄存器(Program Status Word,PSW):程序状态字寄存器用来记录数据运算结果的状态,例如,有无进位,有无溢出,运算结果的符号是正还是负,结果是否为零等。这些运算结果的状态信息称为标志(Flag)或条件码(Condition Code),它们合并起来保存到程序状态字PSW 中。

(3)主存接口寄存器

这是指与主存进行数据交换使用的两个寄存器。

①存储器地址寄存器MAR:当CPU 需要从主存读取指令、操作数或者向主存写入数据时,需要将指令地址(PC内容)、操作数地址或运算结果的地址送入MAR,再根据MAR提供的地址找到对应的操作数。

②存储器数据寄存器MDR:有时也称为数据缓冲寄存器MBR。写入主存的数据一般先送至MDR,再送入主存。从主存读出的数据一般也要先送入MDR,再送入指定的CPU中指定的寄存器。

3.控制器

控制器就是计算机系统的指挥中心,这一部件控制着计算机系统的各个功能部件,保证其能协同工作,自动执行计算机程序。例如,这一部件将控制信号发给寄存器,控制寄存器自动加1,清0,输出寄存器的内容;也能控制运算器完成指定的加减乘除运算等;控制器也能通过以恰当的顺序发出相应的内部或外部控制信号,使CPU 和计算机其他存储器、总线、输入和输出部件完成取指、译码、执行指令所需要的操作。

为了提高CPU 性能,现代CPU 还采取了指令流水线技术,即把原来串行的指令执行改为并行执行,从而提高CPU 的效率。例如一条指令要执行要经过3个阶段:取指令、译码、执行,每个阶段都要花费一个机器周期,如果没有采用流水线技术,即串行执行,那么这条指令执行需要3个机器周期;如果采用了指令流水线技术,那么当这条指令完成“取指”后进入“译码”的同时,下一条指令就可以进行“取指”了,即并行执行,这样就提高了指令的执行效率。