5.5.1 单总线数据通路

2026年01月15日

5.5.1 单总线数据通路

数据通路中的部件之间都连接到同一条总线上,使用总线进行数据传送要保证在同一时刻只有一个部件在总线上发送数据。如图5.10所示,可以使用缓冲门来控制各个部件向总线发送数据,只要保证同一时刻只有一个缓冲门是打开的,就可以确定只有一个部件在总线上发送数据。其中R0、R1 以及R n-1均为通用寄存器,Y 与Z是运算器中的暂存器。

通常在寄存器与总线之间有Rin和Rout两个控制信号,当Rin=1时,控制将总线上的信息存到寄存器R 中,当Rout=1时,控制寄存器R 将信息送到总线上去。

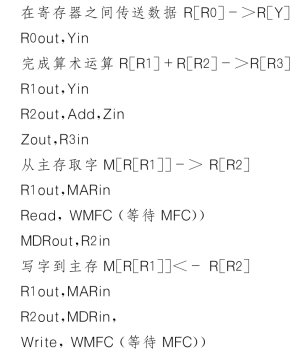

四种基本操作的时序控制信号如下,R 表示取寄存器中的内容,M 表示取存储器中的内容:(https://www.daowen.com)

说明:CPU 访存储器有两种通信方式:早期采用异步方式直接访问存储器,即用MFC等待应答信号,现在多用同步方式,无须等待应答信号。