2.4.1 触发器

在数字电子系统中,不但需要对二进制信号进行算术运算和逻辑运算,很多时候还需要把所用到的信号及运算结果保存下来,所以设计逻辑电路时需要具有存储功能相关元器件来完成电路设计功能的诸多要求。

触发器是具有记忆功能的基本逻辑单元,是能存储一位二进制数码的基本单元电路。触发器的电路结构有多种形式,它们的触发方式和逻辑功能也各不相同。触发器具有两个稳定状态,分别表示0和1两种状态;在输入控制信号的作用下,可以在0与1两个状态之间进行转换。

触发器的基本逻辑电路是由门电路引入适当的反馈而构成的。根据电路结构形式不同,可以将触发器分为基本RS触发器、同步触发器、主从触发器、边沿触发器等多种类型。不同的电路结构在状态变化过程中也会有不同的动作特点,掌握其动作特点对于正确使用这些触发器是十分必要的。由于信号的输入方式以及触发器状态随输入信号变化的规律不同,触发器又可分为RS触发器、D 触发器、JK 触发器、T 触发器等几种类型。描述触发器逻辑功能的方式有特性表、特性方程、状态转换图等。熟悉各类触发器的描述方法是分析和设计时序逻辑电路的基础。

1.基本RS触发器

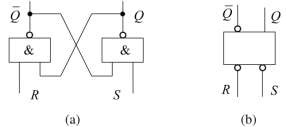

最简单的触发器是基本RS触发器。组合逻辑电路的基本特点是电路中没有反馈,如果在此电路中引入反馈,如图2.35(a)所示,电路的性质就发生了变化,即它已不属于组合逻辑电路,通常称其为基本RS触发器。基本RS触发器是各种改进型触发器的基本单元电路。

图2.35 基本RS触发器逻辑电路及基本符号

从电路图得到逻辑表达式:

![]()

基本RS触发器可以由两个与非门构成。基本RS触发器由电平触发,并且有一个重要的约束条件,R 和S 不能同时为零,即约束条件为:S+R=1。

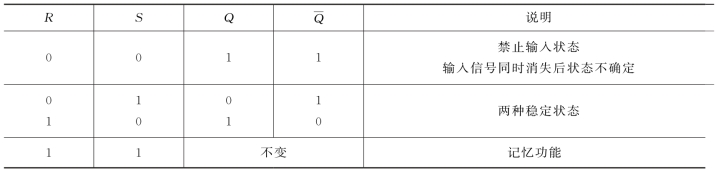

分析得到状态表,如表2.21所示。

表2.21 状态表

当触发器正常工作时,Q 和Q端的状态总是互补的。

2.同步RS触发器

在数字系统中,很多时候,希望触发器只有在时钟来临时,输出状态改变,其他时候,触发器维持原状态。这样就可以让多个触发器在同一时刻动作。所以,在触发器的基础上又引入了同步控制时钟脉冲信号CP,则称这种触发器为同步触发器。

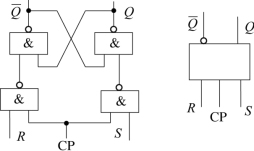

将基本RS触发器的输入端分别经过一个与非门作为时钟控制信号,就成为同步RS触发器,如图2.36所示。

图2.36 同步RS触发器逻辑电路图及基本符号

当CP=0时控制门封锁,Q 不变。

当CP=1时,R、S 的信号可被接受,进而影响Q 的状态。

状态表如表2.22所示。

表2.22 状态表

时间反映在状态表,用现态和次态区别。

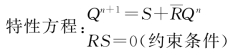

特性方程:Qn+1=S+ Q n

Q n

约束方程:RS=0

同步RS触发器与基本RS触发器的不同之处在于,只有在时钟CP=1的时候,输出状态才能被改变。但是发现同步RS触发器还有一个不足之处:当CP=1时,R 和S 若多次改变,每次改变都会影响输出。这种现象,称为空翻现象。

空翻的危害性:降低了电路的抗干扰能力,并意味着失去了Q 端的状态变化与CP脉冲同步的特点。

3.主从RS触发器

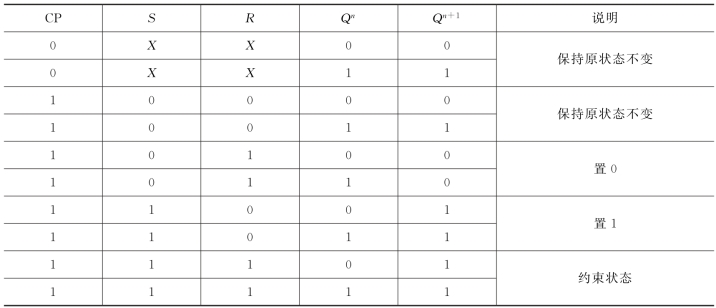

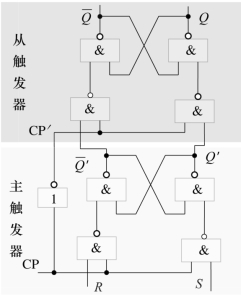

为解决空翻问题,将两个同步RS触发器串联,电路如图2.37所示,构成了主从RS触发器。主从触发器由主触发器和从触发器组成,时钟信号CP经由非门,变成CP′控制从触发器。

图2.37 主从RS触发器逻辑电路

主从触发器的触发翻转分为两个节拍:

(1)当CP=1时,CP′=0,从触发器被封锁,保持原状态不变;主触发器工作,接收R 和S 端的输入信号;当CP=0时,CP′=1,主触发器被封锁,从触发器动作。

(2)当CP由于跳变到0时,主从触发器有效触发,从而克服了同步RS触发器多次翻转和空翻问题。

当CP=1时,主触发器接收输入信号。

特点:在CP=1期间,Q′可随着R、S 的状态多次变化,但Q 的状态仅由CP由1变0前的Q′决定。

(https://www.daowen.com)

(https://www.daowen.com)

主从触发器的输出改变仅取决于时钟信号的下降沿时刻,有效地解决了空翻问题。但是,主从RS触发器仍然存在约束条件:R、S 不能同时为1。

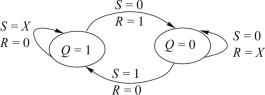

4.主从JK 触发器

如图2.38所示,在时钟脉冲CP的作用下,可以看到在CP=1时,从触发器被封锁,输出状态不变化。

图2.38 主从JK 触发器的逻辑电路图及基本符号

此时主触发器输入门打开,接收J、K 输入信号;当CP=0时,主触发器被封锁,禁止接收J、K 信号,主触发器维持原态;从触发器输入门被打开,从触发器按照主触发器的状态翻转。

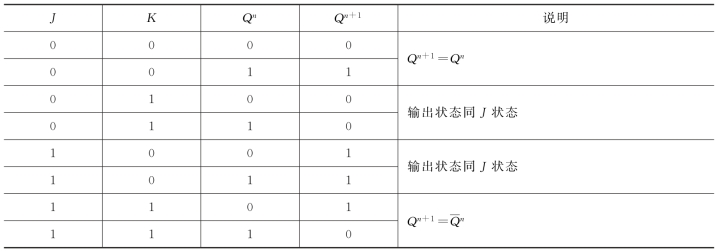

JK 触发器逻辑功能状态表如表2.23所示。

表2.23 JK 触发器逻辑功能状态表

特性方程:Qn+1=J +

+ Q n

Q n

状态转换图如图2.39所示。

5.D 触发器

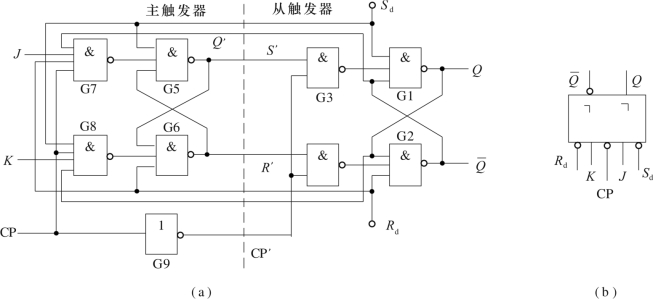

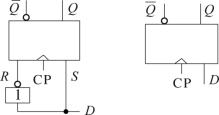

无论是RS触发器还是JK 触发器,都具有两个输入控制端,而D 触发器(图2.40)只有一个输入控制端,可以满足某些应用场合的需要。

图2.39 状态转换图

图2.40 D 触发器基本符号

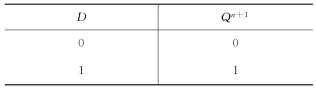

特性方程:Qn+1=D

特性表如表2.24所示。

表2.24 特性表

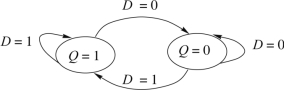

状态转换图,如图2.41所示。

图2.41 D 触发器状态转换图

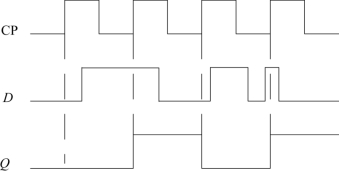

时序图如图2.42所示。

6.T 触发器

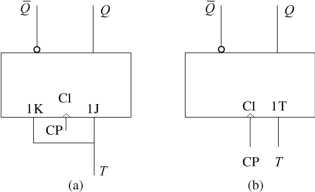

D 触发器虽然满足了仅有1个输入端的要求,但输出状态由D 决定,在时钟的作用下,还想保持输出状态不变还是不易实现。如果把JK 触发器的J、K 输入端连接在一起并标记为T,则构成T 触发器,如图2.43所示。

图2.42 D 触发器时序图

图2.43 电路图及逻辑符号

把J=K=T 代入式中可得T 触发器的特性方程:

![]()

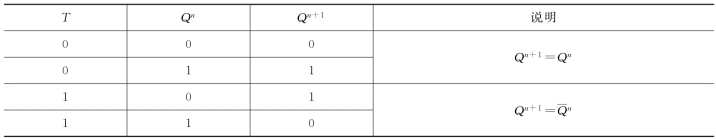

T 触发器的特性表如表2.25所示。

表2.25 T触发器的特性表

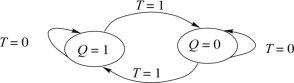

T 触发器的状态转换图如图2.44所示。

图2.44 T 触发器的状态转换图