6.2 主存与CPU的连接

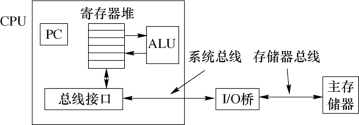

CPU 通过芯片内的总线接口部件连接到系统总线,然后通过I/O 桥接器、存储器总线连接到主存,如图6.3所示。

图6.3 主存与CPU 的连接

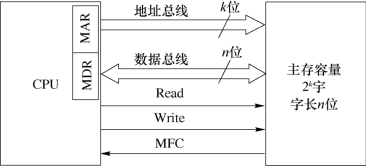

CPU 对存储器进行读写操作,首先由地址总线给出地址信号,然后发出读操作或写操作的控制信号,最后在数据总线上进行信息交流。如果将由若干存储芯片构成的存储器和CPU 看成两个黑盒子,通过地址总线(AB)、数据总线(DB)、控制总线(CB)相联的结构如图6.4所示。

图6.4 主存和CPU 的硬连接

存储器地址寄存器(MAR)和存储器数据寄存器(MDR)是主存和CPU 之间的接口。MAR 可以接受来自程序计数器的指令地址或来自地址形成部件的操作数地址,以确定要访问的单元。MDR 是向主存写入数据或从主存读出数据的缓冲部件。MAR 和MDR 从功能上看属于主存,但在小型计算机、微型计算机中常放在CPU 内。

从系统的观点看,主存储器和中央处理器是两个功能模块,两个大模块之间既有硬连接又有软连接。硬连接包括地址线、数据线和控制线。其中k 位宽的地址线是单向的,n 位宽的数据线是双向的。控制线有若干条,各有各的功能,读/写命令由CPU 发出传送给存储器,当存储器操作完成后再向CPU 回送完成信号(MFC)。通常将这三组连线统称为存储总线(MBUS)。而把MAR 和MDR 看作存储器与CPU 之间的接口。所谓软连接,这里指的是访问存储器的指令。基本指令有读指令READ 和写指令WRITE。读、写指令都由CPU 发出。硬连接是两大模块之间联系的物理基础,软连接是使两大模块有效工作的关键。

读写的基本操作如下:

(1)读。读操作是指从CPU 送来的地址所指定的存储单元中取出信息,再送给CPU,其操作过程如下:

①地址→MAR→AB:CPU 将地址信号送至地址总线。(https://www.daowen.com)

②Read:CPU 发出读命令。

③Wait for MFC:等待存储器工作完成信号。

④M(MAR)→DB→MDR:读出信息经数据总线送至CPU。

(2)写。写操作是指将要写入的信息存入CPU 所指定的存储单元中,其操作过程如下:

①地址→MAR→AB:CPU 将地址信号送至地址总线。

②数据→MDR→DB:CPU 将要写入的数据送至数据总线。

③Write:CPU 发出写命令。

④Wait for MFC:等待存储器工作完成信号。

由于CPU 和主存的速度存在着差距,所以两者之间的速度匹配是很关键的。通常有两种匹配方式:同步存储器读取和异步存储器读取。上面给出的读写基本操作是以异步存储器读取来考虑的,CPU 和主存之间没有统一的时钟,由主存工作完成信号(MFC)通知CPU“主存工作已完成”。

对于同步存储器读取,CPU 和主存采用统一时钟,同步工作,因为主存速度较慢,所以CPU 与之配合必须放慢速度。在这种方式中,不需要主存工作完成信号。