4.3.5 IA-32汇编语言实例

例如,假设(EAX)=000000B4 H,(EBX)=00000011 H,[000000F8 H]=000000A0 H,执行指令“MULB%BL”后,哪些寄存器的内容会发生变化?

因为(EAX)=000000B4H,(EBX)=00000011H,所以(AL)=B4H,(BL)=11H,指令“MULB%BL”中指出的操作数为8位,故指令的功能为“(AX)=(AL)(BL)”,因此,改变内容的寄存器是AX,指令执行后(AX)=0BF4H。

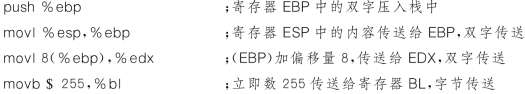

例如,说明每条指令的含义:

MMX与SSE(https://www.daowen.com)

MMX:是MultiMedia eXtensions(多媒体扩展)的缩写,是第六代CPU 芯片的重要特点。MMX 技术是在CPU 中加入了特地为视频信号(Video Signal),音频信号(Audio Signal)以及图像处理(Graphical Manipulation)而设计的57条指令,目的是提高计算机的多媒体(如立体声、视频、三维动画等)处理功能。在MMX 指令集中,借用了浮点处理器的8个寄存器,这样导致了浮点运算速度降低。

由于MMX 指令并没有带来3D 游戏性能的显著提升,1999年Intel公司在Pentium IIICPU 产品中推出了数据流单指令序列扩展指令(SSE)。SSE 兼容MMX 指令,它包括70条指令,其中包含单指令多数据浮点计算、额外的SIMD(单指令多数据技术)整数和高速缓存控制指令。其优势包括:更高分辨率的图像浏览和处理、高质量音频、MPEG2 视频、MPEG2加解密;语音识别占用更少CPU 资源;更高精度和更快响应速度。

SSE2是Intel在P4的最初版本中引入的,这个指令集添加了对64位双精度浮点数的支持。这个指令集还增加了对CPU 的缓存的控制指令。

SSE3是Intel在P4的Prescott版中引入的指令集。SSE3新增了13条指令,其中一条用于视频解码,两条用于线程同步,其余的用于复杂的数学运算、浮点数与整数之间的转换及SIMD 浮点运算,使处理器对DSP及3D 处理的性能大为提升。2005年,作为SSE3指令集的补充版本,SSSE3出现在酷睿微架构处理器中,新增16条指令,进一步增强CPU 在多媒体、图形图像和Internet等方面的处理能力。

2008年,SSE4指令集发布。这是英特尔自SSE2之后对ISA 扩展指令集最大的一次升级扩展。新指令集增强了从多媒体应用到高性能计算应用领域的性能,同时还利用一些专用电路实现对于特定应用加速。SSE4分为4.1和4.2两个版本。SSE 4.1版本的指令集新增加了47条指令,主要针对向量绘图运算、3D 游戏加速、视频编码加速及协同处理的加速。此外SSE4.1还加入了6条浮点型运算指令,支援单、双精度的浮点运算及浮点产生操作。SSE4.1指令集还加入了串流式负载指令,可提高图形帧缓冲区的读取数据频宽,理论上可获取完整的缓存行,即单次性读取64位而非原来的8位,并可保持在临时缓冲区内让指令最多带来8倍的读取频宽效能提升。SSE4.2包含7条指令,主要针对字符串和文本处理。例如,对XML应用进行调整查找和对比等。