5.4.6 控制信号的设置

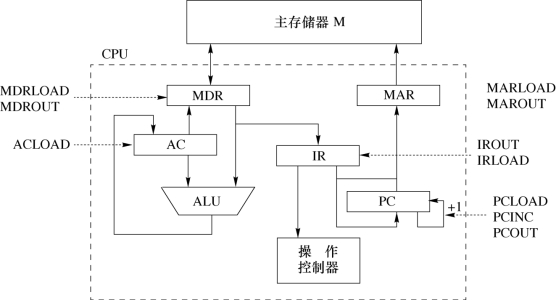

现在设计控制信号产生电路发向五个部件的控制信号。如图5.7所示,每个部件对应的控制信号如下:MAR 的装载信号为MARLOAD,MAR 的输出信号为MAROUT,PC 的装载信号为PCLOAD,PC 的自增信号为PCINC,PC 输出信号为PCOUT,MDR 的装载信号为MDRLOAD,输出信号为MDROUT,AC 的装载信号为ACLOAD,IR 的装载信号为IRLOAD,IR 的地址字段输出信号为IROUT。

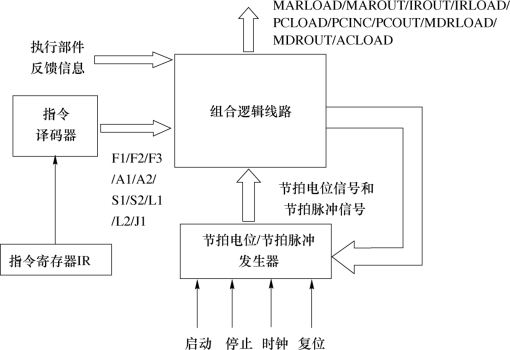

硬布线控制设计使用时序逻辑电路和组合逻辑电路来产生控制信号。如图5.8所示,主要包括指令译码器,即根据IR 的操作码字段译码出对应的控制信号,由于本例的状态有10个,因此采用4-16译码器。节拍电位/节拍脉冲发生器产生同步时钟,控制所有微操作在同一时钟周期内完成。组合逻辑线路即根据译码器得到的状态,设计出每个微操作控制信号的逻辑表达式,并进行化简;最后按此逻辑表达式,用与门、或门和非门等逻辑门电路及触发器来生成对应的控制信号。

图5.7 模型机控制信号设置

图5.8 控制信号产生

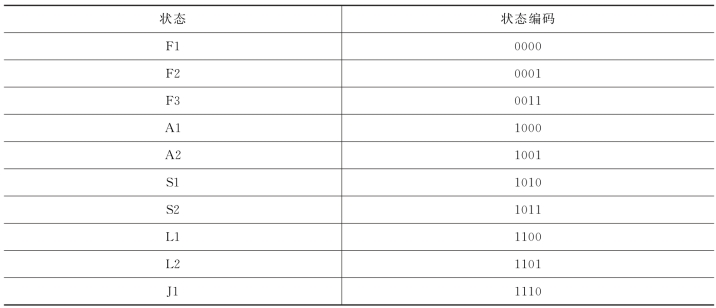

状态的编码如表5.2所示。

表5.2 状态编码表

我们说过,译码器应该是根据指令寄存器IR 的操作码字段转向不同的状态,本例中是将指令操作码进行转换得到不同的状态编码的,它们的关系如下:

即执行子周期的A1、S1、L1、J1的状态编码正好是两位IR 操作码的前面加上1,后边加上一个0,变成四位状态编码。这样的好处是,当执行完成取指阶段,到F3时,只需要取出IR 的操作码部分,前面加上一个1,后边加上一个0,就得到了执行子周期的第一个状态。

指令译码器产生的状态信号可以进入组合逻辑线路模块,从而组合成控制MAR、PC、MDR、IR、ALU 及存储器的控制信号。例如,地址寄存器MAR 是在状态F1(MAR←PC)和F3(MAR←IR[5,4,…,0])期间装载的,通过将这两个状态信号进行逻辑或操作,可以生成MARLOAD 信号。以下用v表示逻辑或的关系:

MARLOAD=F1 v F3;

同理,其他部件的控制信号为:

PCLOAD=JMP1;(https://www.daowen.com)

PCINC=F2;

PCOUT=F1;

MDRLOAD=F1 v A1 vs1 v L1;

MDROUT=F3v A2 vS2 v L2

IRLOAD=F3;

IROUT=F3;

ACLOAD=S1v L1;

ACOUT=F3v A2vS2v L2vJ 1;

当然,我们例子中的模型机是非常简单的,实际微操作控制信号的逻辑表达式有的简单,有的复杂,则对应的逻辑电路有的简单,有的复杂,一台计算机往往有几十个至几百个微操作控制信号,这些控制信号的逻辑电路组合在一起构成的控制单元就是一个多输入和多输出的无规则的树形网络。微操作控制信号越多,线路就越复杂。

早期的组合逻辑控制器是以使用最少器件数和取得最高速度为设计目标,它的最大优点是速度快,但结构不规整,设计、调试和维修都比较困难。而且,控制部件一旦用硬布线固定下来,就很难修改与扩展。

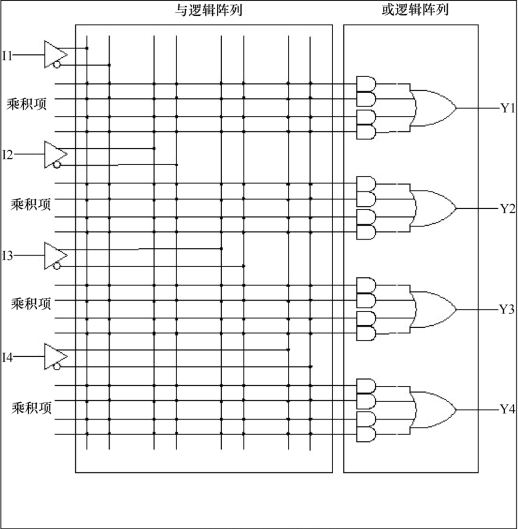

因此随着大规模集成电路的发展,在20世纪70年代出现了PLA(可编程逻辑阵列,Programmable Logic Array)实现组合逻辑设计的方法。PLA 由一级“与”门和一级“或”门组成,其输出为输入项的与或式。因此,我们可以根据指令码,时序信号及其他状态等,写出微操作控制信号的逻辑表达式后,由外部写入编码图案,决定哪些矩阵交点应该相连,输出即为微操作的控制信号。PLA 控制能简化设计,有利于大规模集成电路的生产。

随着时代的发展,20世纪70年代末,AMD 推出了可编程阵列逻辑PAL(Programmable Array Logic);80年代,Lattice公司推出了通用阵列逻辑GAL(Generic Array Logic);80年代中期,Xilinx公司推出了现场可编程门阵列FPGA (Field Programmable Gate Array)。Altera公司推出了可擦除的可编程逻辑器件EPLD(Erase Programmable LogicDevice),集成度高,设计灵活,可多次反复编程;90年代初,Lattice公司又推出了在系统可编程概念ISP及其在系统可编程大规模集成器件isp LSI);现以Xilinx、Altera、Lattice为主要厂商,生产的FPGA 单片可达上千万门,速度可实现550 MHz,采用65nm 甚至更高的光刻技术。可编程与阵列及可编程或阵型如图5.9所示。

图5.9 可编程与阵列及可编程或阵型列