6.4.5 现代计算机的高速缓存结构

在现代计算机系统中几乎都使用Cache机制,以下以Intel公司微处理器中的Cache为例来说明具体的Cache结构。

Pentium 微处理器在芯片内集成了一个代码Cache和一个数据Cache。片内Cache采用两路组相联(即每组两个数据块)结构,共128组。片内Cache采用LRU 替换策略,每组有一个LRU 位,用来表示该组哪一路中的Cache行被替。Pentium 处理器有两条单独的指令来清除或回写Cache。

Pentium 处理器采用片外二级Cache,可配置为256 KB或512 KB,也采用两路组相联方式,每行数据有32字节、64字节或128字节。

Pentium 4 处理器芯片内集成了一个L2Cache 和两个L1Cache。L2Cache 是联合Cache,数据和指令存放在一起,所有从主存获取的指令和数据都先送到L2Cache中。它有三个端口,一个对外,两个对内。对外的端口通过预取控制逻辑和总线接口部件,与处理器总线相连,用来和主存交换信息。在对内的端口中,一个以256位位宽与L1数据Cache相连;另一个以64位位宽与指令预取都件相连,由指令预取部件取出指令,送指令译码器,指令译码器再将指令转换为微操作序列,送到指令Cache中。Intel称该指令Cache为踪迹高速缓存(Trace Cache,TC),其中存放的并不是指令,而是指令对应的微操作序列。(https://www.daowen.com)

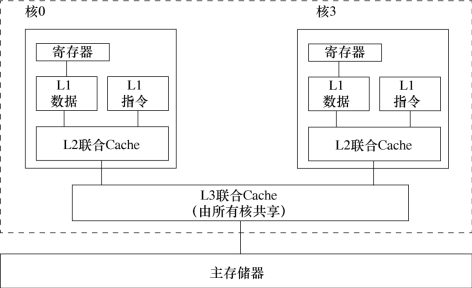

Intel Core i7采用的Cache结构如图6.30所示,每个核内有各自私有的L1Cache和L2Cache。其中,L1指令Cache和数据Cache都是32 KB数据区,皆为8路组相联,存取时间都是4个时钟周期;L2Cache是联合Cache,共有256 KB数据区,8路组相联,存取时间是11个时钟周期。在该多核处理器中还有一个供所有核共享的L3Cache,其数据区大小为8 MB,16路组相联,存取时间是30~40个时钟周期。Intel Core i7中所有Cache的块大小都是64 B。

图6.30 Intel Core i7处理器的Cache结构