6.3.4 半导体存储器的扩展

存储器和CPU 之间的连接包括地址线、数据线和控制线的连接,CPU 访问存储器的时候通过地址线提供要访问的存储器单元字的地址信息;CPU 的![]() (高电平表示读,低电平表示写)提供对存储器的读写控制信号;CPU 的数据线可以直接和存储器连接。

(高电平表示读,低电平表示写)提供对存储器的读写控制信号;CPU 的数据线可以直接和存储器连接。

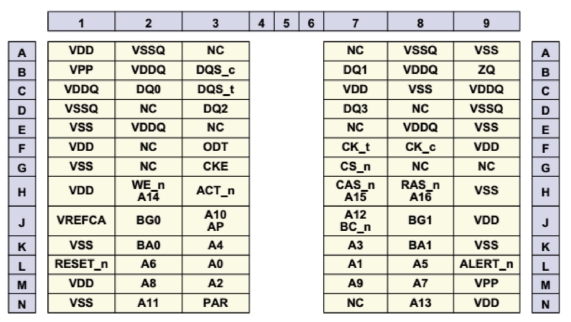

图6.11 1×4封装引脚排列图

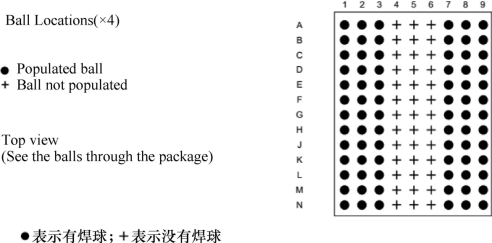

图6.12 1×4焊球位置顶视图

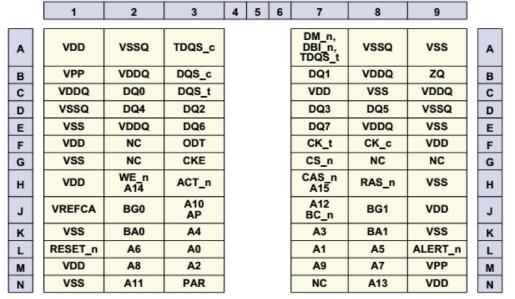

图6.13 1×8封装引脚排列

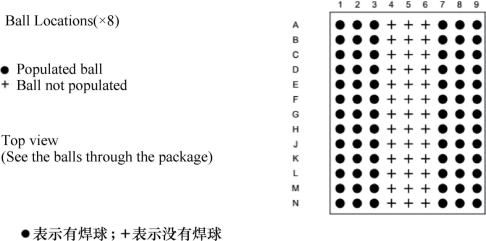

图6.14 1×8焊球位置顶视图

通常一个存储器芯片不能满足计算机存储器的字数要求和数据宽度的要求,需要用许多存储器芯片构成所需的主存储器。具体构成主存储器时,首先要选择存储芯片的类型,是SRAM 还是DRAM,还要考虑容量扩展的技术。用若干存储芯片构成一个存储系统的方法主要有位扩展法、字扩展法和字位扩展法。

1.位扩展

位扩展法用于增加存储器的数据位,即是用若干片位数较少的存储器芯片构成具有给定字长的存储器,而存储器的字数与存储芯片上的字数相同。位扩展时,各存储芯片上的地址线及读/写控制线对应相接,而数据线单独引出。

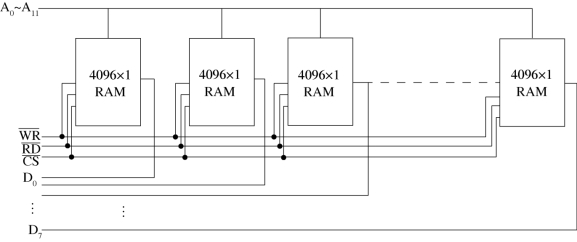

【例6.1】 用4096×1的芯片构成4 KB存储器。

解:存储器芯片容量4096×1,需要的存储器容量4 KB,则(4 KB×8)/(4096×1)=8,共需要8片存储器芯片。芯片连接如图6.15所示。

图6.15 用4096×1的芯片构成4 KB存储器逻辑

每块芯片的A0~A11地址线连接在一起,接收来自CPU 地址线提供的地址信息,选定芯片内部的一个字单元。

每块芯片的![]() 片选信号连接在一起,与CPU 提供的控制信号或者高位的地址线连接,用于选择所有存储芯片。

片选信号连接在一起,与CPU 提供的控制信号或者高位的地址线连接,用于选择所有存储芯片。

每块芯片的![]() 连接在一起,与CPU 提供的读信号连接。每块芯片的WR信号连接在一起,与CPU 提供的写信号连接。当CPU 发出读写信号时,所有芯片可以同时进行读写操作。

连接在一起,与CPU 提供的读信号连接。每块芯片的WR信号连接在一起,与CPU 提供的写信号连接。当CPU 发出读写信号时,所有芯片可以同时进行读写操作。

CPU 对存储器读写操作时,每块存储器芯片的一位数据线可以和CPU 的8位数据线进行数据交流,从而实现CPU 访问一次存储器,可以有8位数据操作。

2.字扩展

当存储芯片中每个单元的位数与CPU 字长相同时,如果所要求的存储器容量大于一片芯片的容量,就要采用字扩展法,在字方向上进行扩充,而位数不变。字扩展时,各存储芯片的低位地址线连接在一起,高位地址译码后连接各芯片的片选信号![]() 。每个存储芯片均提供CPU 需要的多位数据。

。每个存储芯片均提供CPU 需要的多位数据。

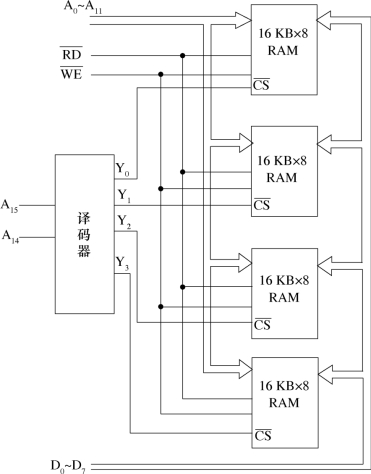

【例6.2】 用16 KB×8芯片构成64 KB×8存储器。

解:用所需的存储器总容量除以每个芯片容量,则(64 KB×8)/(16 KB×8)=4,一共需要4片存储器芯片。连接如图6.16所示。

图6.16 用16 KB×8构成64 KB×8存储器逻辑

每块芯片的A0~A13地址线连接在一起,与CPU 提供的低位地址线A0~A13连接,用于选定存储芯片内部的字单元。

CPU 提供的高位地址线A 14、A 15连接到译码器的输入端,在输出端产生各存储芯片的片选信号。

CPU 的读写信号和各存储芯片的读写信号相连接,提供芯片的读写控制信号。

各存储芯片的数据线并联,某片芯片在被选中进行读写操作时,能和CPU 进行8位数据的操作。

3.混合扩展

当选用的存储芯片容量和每个单元的位数都不能满足所需要的存储器要求时,就需要进行字位同时扩展,称为字位扩展,即混合扩展。

当混合扩展时,将各存储芯片的地址线与CPU 提供的低位地址线相连,CPU 提供的高位地址通过译码后连接各存储芯片的片选信号,有些存储芯片的片选会同时被选中。每个芯片提供选中的字单元中多位数据,同时被选中的多块芯片一起提供CPU 需要的多个字。(https://www.daowen.com)

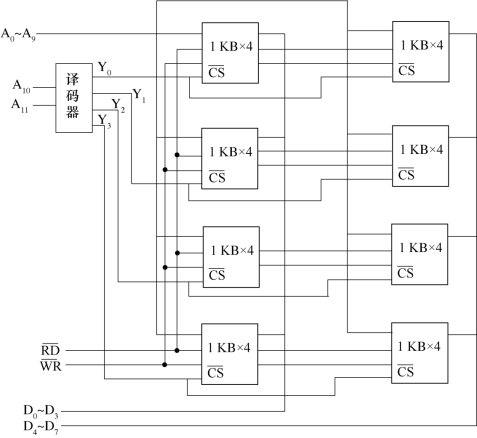

【例6.3】 用1 KB×4的芯片构成4 KB×8的存储器。

解:根据所需存储器容量和存储芯片容量,计算所需芯片数量:(4 KB×8)/(1 KB×4)=8片。芯片连接如图6.17所示。

图6.17 用1 KB×4的芯片构成4 KB×8的存储器逻辑

各存储芯片上的A 0~A 9 地址线连接到CPU 的低位地址线。CPU 提供的高位地址线A 10、A 11连接到译码器,产生存储器芯片所需要的片选信号。由于一块存储芯片选中时只能向CPU 提供4位数据线,所以,需要将两块存储芯片的片选连接在一起。片选连在一起的两块存储芯片,4位数据线分别连接CPU 的4位数据线,可以给CPU 提供8位数据。

4.用DRAM 芯片构成主存储器

为了保持数据,DRAM 使用MOS管的栅极电容存储数据,但是由于栅极漏电会造成数据丢失,因此隔一段时间就要对数据重写,对DRAM 定期重写称为刷新。如果存储单元没有被刷新,存储的信息就会丢失。上次对整个存储器刷新结束到下次对整个存储器全部刷新一遍为止的时间间隔称为刷新周期,一般为2 ms。

常用的刷新方式有四种:集中刷新方式、分散刷新方式、异步刷新方式、透明刷新方式。

(1)集中刷新方式

在整个刷新间隔内集中对每一行进行刷新,刷新时读/写操作停止。每行的刷新周期一般与一次的读/写周期相等。集中刷新方式的主要缺点是,在刷新时期内不能进行存取操作(这个时间段称为死区),影响了存储系统的效率。

(2)分散刷新方式

把每行存储元的刷新分散安排在各个读写周期内,即把读写周期分为两段,前段用来进行读/写,后段为刷新时间。这种方式虽然没有充分利用2 ms时间,但也不存在存储器“死”时间。

(3)异步刷新方式

将前两种刷新方式结合起来即可构成异步刷新方式。每行刷新的时间是行数对2 ms的分割。当行地址为7位时,行数是128,每隔15.5μs刷新一行。这种方式充分地利用了2 ms时间,适用于高速存储系统。

(4)透明刷新方式

CPU 在指令译码阶段,存储器是空闲的,可以利用这段空闲时间进行刷新操作,而不占用CPU 时间。因为这种刷新方式对CPU 是透明的操作,所以称为透明刷新。这时设有单独的刷新控制器,刷新由单独的时钟、行计数器和译码独立完成,目前高档微机中大部分采用这种刷新方式。

如果选用DRAM 芯片构成存储器,DRAM 芯片的地址分行地址和列地址,增加了![]() 和

和![]() ,而CPU 访问存储器时,地址信息是同时提供的,这就需要一个控制电路,以生成储器需要的控制信号,并且将地址信息分成行地址和列地址,并按读写工作时序送出。另外,DRAM的刷新操作一般也在存储器控制电路的控制下进行。存储器控制电路用一个计数器提供一个刷新的行地址,对存储阵列中的一行数据读出,经过信号放大后再写回,就完成了一次刷新操作。这个控制电路就是DRAM 控制器,它是CPU 和DRAM 芯片之间的接口电路。

,而CPU 访问存储器时,地址信息是同时提供的,这就需要一个控制电路,以生成储器需要的控制信号,并且将地址信息分成行地址和列地址,并按读写工作时序送出。另外,DRAM的刷新操作一般也在存储器控制电路的控制下进行。存储器控制电路用一个计数器提供一个刷新的行地址,对存储阵列中的一行数据读出,经过信号放大后再写回,就完成了一次刷新操作。这个控制电路就是DRAM 控制器,它是CPU 和DRAM 芯片之间的接口电路。

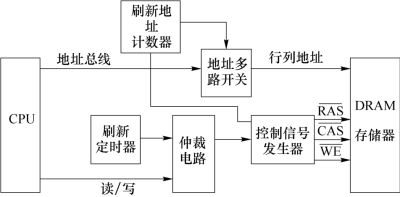

DRAM 控制器的主要组成结构如图6.18所示,组成部分包括:

①地址多路开关:将CPU 送来的地址转换为分时向DRAM 芯片送出的行地址和列地址。

②刷新定时器:定时产生DRAM 芯片的刷新请求信号。

③刷新地址计数器:DRAM 芯片是按行进行刷新的,需要一个计数器提供刷新行地址。

④仲裁电路:如果来自CPU 的访存请求和来自刷新定时器的刷新请求同时产生,由仲裁电路进行优先权仲裁。

⑤控制信号发生器:提供![]() 、

、![]() 和

和![]() 控制信号,用户读/写操作和刷新操作。

控制信号,用户读/写操作和刷新操作。

【例6.4】 在128×128 矩阵的动态存储芯片中,设每个读写周期和刷新操作都为0.5μs,刷新间隔为2 ms,比较计算3种刷新方式(集中式刷新、分布式刷新、异步刷新)的刷新次数、读写次数和效率。

解:①集中式刷新:刷新操作集中在一段时间内,次数为全部刷新一遍的操作次数。

存储阵列有128行,所以刷新次数为128次。刷新时间为128×0.5μs=64μs。可以进行的读写次数为(2000-64)/0.5μs=3872次。刷新周期中存在64μs死区。

图6.18 DRAM 控制器

②分布式刷新:在存储读写周期中完成刷新操作。

在存储周期中,进行读写和刷新需0.5+0.5=1μs,那么在刷新周期里读写和刷新次数为2000/1=2000次,其中读写次数2000次,刷新次数2000次。这种方式没有死区,但读写次数少,刷新次数多。

③异步刷新:将刷新次数平均分配到刷新周期中,则2 ms内必须对每一行刷新一次。

刷新次数为128 次,则刷新间隔:2000/128=15.5μs。每个15.5μs中15μs读写,0.5μs刷新,则读写次数15/0.5=30,总的读写次数为30×128=3 840次。这种方式没有死区,并且读写次数也较高。

在现在的动态存储器产品中,刷新控制电路都包括在存储器芯片中,芯片外部只需要给出启动刷新操作的控制信号。