5.4.4 控制器的设计

CPU 的控制器的设计其实就是实现指令周期的控制,即产生各个指令周期微操作所需的控制信号。下面确定出每个阶段微操作的状态。

(1)取指阶段微操作确定

由上述指令微操作分析,所有指令的第一步都是取指,CPU 通过执行如下的微操作序列完成这个任务。

①将PC 的地址复制到MAR 中,由地址寄存器MAR 驱动并送到CPU 的地址引脚A 0,A 1,…,A 5上,然后把地址送到存储器。确定第一状态F1为:

F1:MAR←PC

②CPU 发出READ 信号,该信号从CPU 输出给存储器,通知存储器从指定的地址取出数据并发送到数据总线上。由于数据总线与CPU 的D0,D1,…,D7引脚相连,CPU 的D0,D1,…,D7引脚与MDR 相连,因此从存储器取得的数据会送到MDR 中。确定第二个状态F2为:

F2:MDR←M,PC←PC+1

F2的两个微操作可以同时进行,是因为两个微操作的部件一个是在存储器,另一个是在PC。另外,之所以在这一步更改PC 的值,是因为PC 保存选取指令的地址,那么PC 在再次执行F1之前就应该再改变。如果是顺序执行,PC的值只需要递增即可,实现PC递增有两种方法:一是在执行子周期递增,二是在取指子周期递增。在本例中,我们选择后一种方案,因此更容易实现。即将PC递增放到F2这一步。

③然后将数据寄存器MDR 送到指令寄存器IR 中。将IR 的高2位即操作码进行译码;IR 的低6位复制到地址寄存器MAR 中准备取操作数。确定第三个状态F3为

F3:IR←MDR,MAR←IR[5,4,…,0]

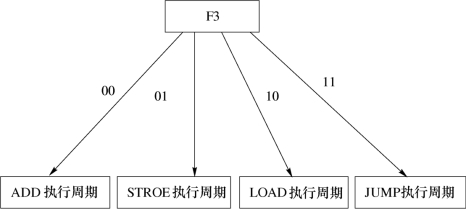

④当IR 的高2位进行译码后,必须判断所取的是哪种指令,从而可以转向正确的执行子周期。对于本例中的简单CPU 来说有四条指令,因此有4个对应的执行子周期,根据操作码00、01、10、11转向对应的执行子周期,如图5.5所示。

图5.5 F3执行子周期

(2)执行阶段微操作状态确定

ADD 指令:

为了从存储器中取出操作数,在F3阶段,需要取的操作数的地址已经送到地址寄存器MAR,因此到ADD 指令的执行子周期,CPU 只需要读取存储器输出的数据即可。因此确定ADD 指令的第一个状态A1是:(https://www.daowen.com)

A1:MDR←M

接着将MDR 的内容与AC的内容相加,因此ADD 指令的第二个状态A2是:

A2:AC←AC+MDR

STORE指令:

该条指令是将AC的内容存储到存储器中,同样,在F3阶段,需要存储的地址已经送到地址寄存器MAR,因此在STORE指令的执行子周期,CPU 需要将AC 的内容存入存储器中,那么需要先将AC的值送到MDR 中,然后将MDR 的内容送到存储器中,因此STORE指令的两个状态S1和S2是:

S1:MDR←AC

S2:M←MDR

LOAD 指令:

该条指令正好与STORE 指令相反,是将存储器中的内容装载到AC 中。同样,在F3阶段,需要提取存储器中的数据地址已经送到MAR 中,因此在LOAD 指令的执行子周期中,需要将存储器中的数据送到MDR 中,并将MDR 中的内容送到AC中。因此LOAD 指令的两个状态L1和L2是:

L1:MDR←M

L2:AC←MDR

JUMP指令:

该条指令是指CPU 必须跳转到目标地址开始执行,那可以通过把目标地址复制到程序计数器PC中实现。由于F3已经把地址存储到数据寄存器的MDR 中,因此只需要将这个值复制到PC中,因此JUMP指令的状态J1是:

J1:PC←MDR

当然,由于目标地址在F3阶段已经复制到MAR 中,因此也可以使用PC←MAR。两种方法都是可行的。