2.4.2 同步时序逻辑电路的分析

同步时序逻辑电路的主要特点:在同步时序逻辑电路中,由于所有触发器都由同一个时钟脉冲信号CP来触发,它只控制触发器的翻转时刻,而对触发器翻转到何种状态并无影响,所以,在分析同步时序逻辑电路时,可不考虑时钟条件。

时序逻辑电路分析的目的,是找出电路状态和输出状态在输入信号和时钟脉冲信号作用下的变化规律,确定该电路的逻辑功能。

时序逻辑电路分析的一般步骤如下:

(1)依据所分析的时序电路逻辑图,写出下列各方程式:

①输出方程:时序逻辑电路的输出逻辑表达式,它通常为现态和输入信号的函数。

②驱动方程:各触发器输入端的逻辑表达式;

③状态方程:将驱动方程代入相应触发器的特性方程中,便得到该触发器的状态方程。

(2)列出状态转换表。

将逻辑电路现态的各种取值情况代入方程和输出方程中进行计算,求出相应的次态和输出,从而列出状态转换真值表。如现态的起始值已给定,则从给定值开始计算;如没有给定,则可设定一个现态起始值依次进行计算。

(3)逻辑功能的说明。

根据状态转换真值表来说明电路的逻辑功能。

(4)画状态转换图和时序图。

状态转换图:是指电路由现态转换到次态的示意图。

时序图:是在时钟脉冲CP作用下,各触发器状态变化的波形图。

(5)检验电路能否自启动。

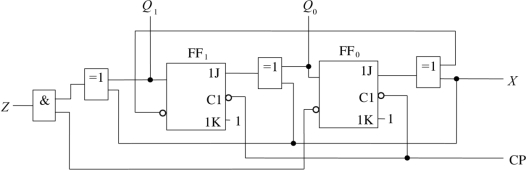

【例2.23】 试分析图2.45所示的时序逻辑电路,写出状态方程并分析功能。

图2.45 时序逻辑电路图

解:该电路为同步时序逻辑电路,时钟方程可以不写。

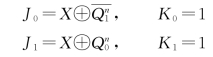

①写出输出方程:

![]()

②驱动方程:

③JK 触发器的特性方程,然后将各驱动方程代入JK 触发器的特性方程,得各触发器的次态方程:

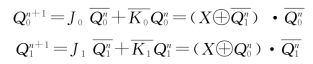

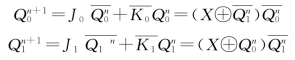

④状态转换表及状态图。

当X=0时,触发器的次态方程简化为:![]()

输出方程简化为:![]()

做出X=0的状态表(表2.26):![]() (https://www.daowen.com)

(https://www.daowen.com)

表2.26 状态表

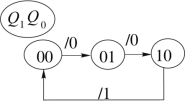

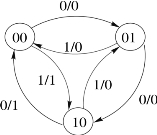

X=0时的状态图如图2.46所示。

图2.46 X=0时的状态转换图

在图2.46中:初态次态用圆圈圈住,中间用箭头表示方向,斜线上方显示的为输入值,斜线下方显示的为输出值。

各触发器的次态方程如下:

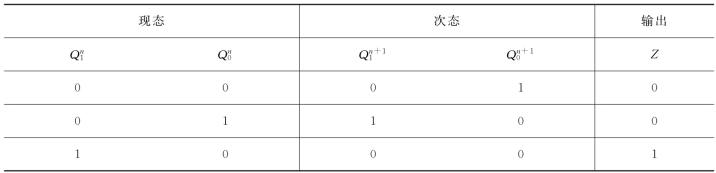

当X=1时,触发器的次态方程简化为

![]()

输出方程简化为![]()

做出X=1的状态表(表2.27):![]()

表2.27 状态表

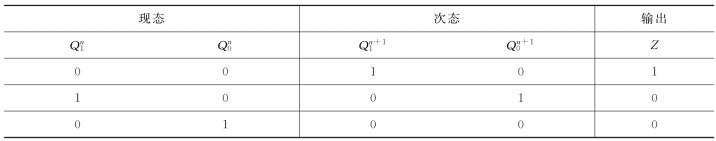

X=1时的状态图如图2.47所示。

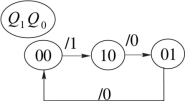

将X=0与X=1的状态图合并起来得完整的状态图,如图2.48所示。

图2.47 X=1时的状态转换图

图2.48 状态转换图

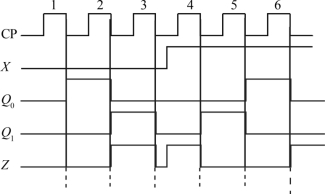

根据状态表或状态图可画出在CP脉冲作用下电路的时序图,如图2.49所示。

图2.49 波形图

逻辑功能分析:

该电路一共有00、01、10 3个状态。

当X=0时,按照加1规律从00→01→10→00循环变化,并每当转换为10状态(最大数)时,输出Z=1。

当X=1时,按照减1规律从10→01→00→10循环变化,并每当转换为00状态(最小数)时,输出Z=1。

所以该电路是一个可控的三进制计数器。