6.4.1 高速缓存的工作原理

在Cache存储系统中,把Cache和主存各分成若干个块(block)。主存中和Cache中块的数目不同,但块的大小相同。主存中含有B块,Cache中含有b块(B>b)。主存中块内地址用W 表示,Cache中用w 表示(W =w)。因此主存地址由块号B和W 组成,Cache地址由b和w 组成。

Cache与主存之间以块为单位进行数据交换。块的大小通常以在主存的一个读/写周期中能访问的数据长度为限,每个块的大小可能是4字节、8字节、16字节或其他值,不同的CPU 不尽相同。Cache存储器中存储内容是主存一部分内容的副本。这一部分内容就是CPU 最近最常访问的内容。

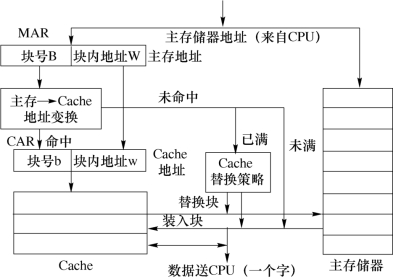

Cache的工作原理如图6.22所示。

图6.22 Cache的工作原理

当CPU 要访问Cache时,CPU 将通过总线送来的主存地址存于主存地址寄存器MAR中(B和W)。W 经过主存-Cache地址变换得到w,B 和w 进入Cache地址寄存器CAR中的b和w(b和B相同)。如果命中(即CPU 所访问的信息在Cache中)则用CAR 地址去访问Cache,从Cache中取出数据送往CPU。如未命中,则用MAR 中的地址去访问主存,从主存中取出一个数据送往CPU,同时把包括被访问地址在内的一(整)块数据调(装)入Cache,以备后用。如果此时Cache已存满,无空闲,则需要根据某种替换策略,淘汰(替换)一块不常用的Cache空间,以便存入从主存中新调入的块。(https://www.daowen.com)

在这里有两个比较重要的参数:命中率和平均访问时间。

命中率是指被访问数据在Cache的次数占访问的总次数的比例,用H 表示。

H=被访问数据在Cache的次数/访问的总次数

平均访问时间示指CPU 访问数据需要的平均时间,用T e 表示。

T e=H×T c+(1-H)×T m

式中,T c是指Cache访问时间,T m是指主存访问时间。

【例6.5】 CPU 执行一段程序时,Cache完成存取的次数为1900次,主存完成存取的次数为100次,已知Cache存取周期为50 ns,主存存取周期为250 ns,求Cache的命中率和平均访问时间。

解:

①命中率:

H=N c/(N c+N m)=1900/(1900+100)=0.95

②平均访问时间:

T a=H×T c+(1-H)×T m=0.95×50 ns+(1-0.95)×250 ns=60 ns