1.采样保持窗口

2026年01月15日

1.采样保持窗口

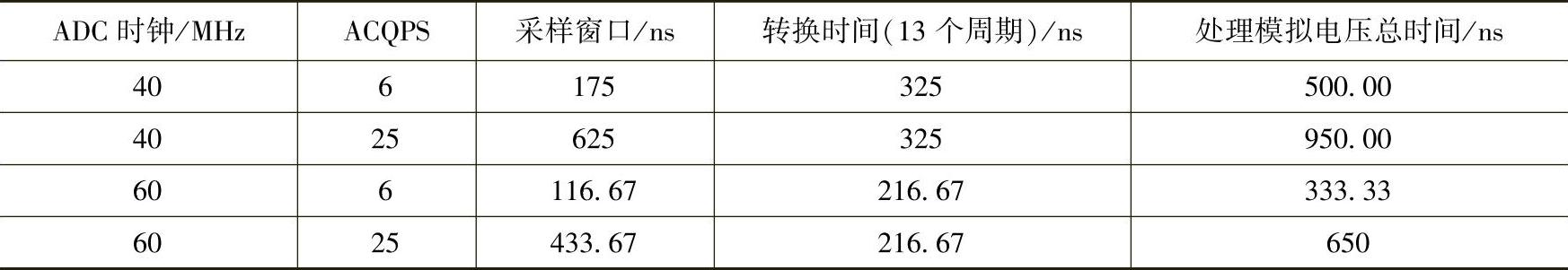

外部驱动器驱动模拟信号的速度和效率不同。一些电路需要更长时间传送到ADC的采样电容。为了满足这个需求,ADC支持控制每个单独的SOC配置的采样窗口的大小。每个ADCSOCxCTL寄存器有6位的ACQPS,该位域决定采样保持窗口的大小。写进该位域的值比SOC需要的采样窗口的周期数小1,也就是说,一个值是15的ACQPS表示16个时钟周期的采样时间。允许的最小的采样周期值是7(ACQPS=6)。将采样时间和ADC的转换时间(13个ADC时钟)加起来得到整个采样时间。表5-1给出了几个采样时间的例子。

表5-1 具有不同ACQPS值的采样时间

(https://www.daowen.com)

(https://www.daowen.com)

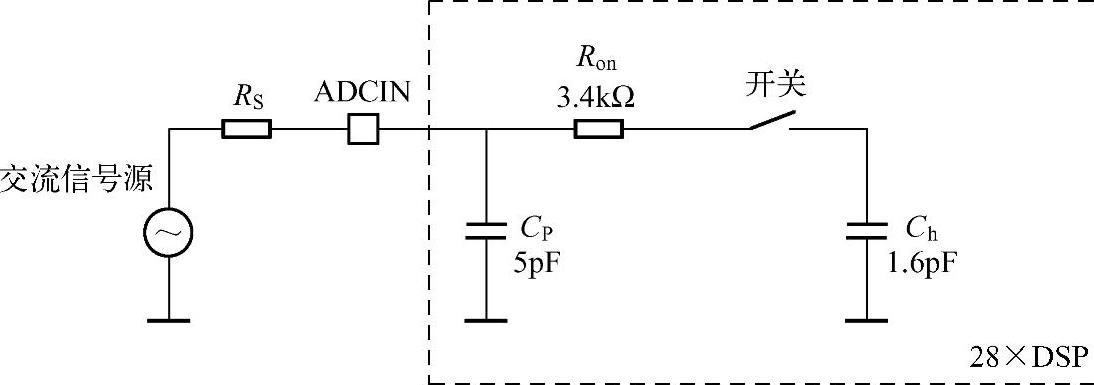

如图5-3所示,ADCIN引脚可以用RC电路模型表示。将VREFLO接地,ADCIN引脚上的变化范围在0~3.3V的电压需要典型的2ns的RC时间常数。图中电路元件的典型参数为开关电阻Ron=3.4kΩ;采样电容Ch=1.6pF;寄生电容Cp=5pF;电源电阻Rs=50Ω。

图5-3 ADCINx输入电路模型