13.2.7 时钟同步

2026年01月15日

13.2.7 时钟同步

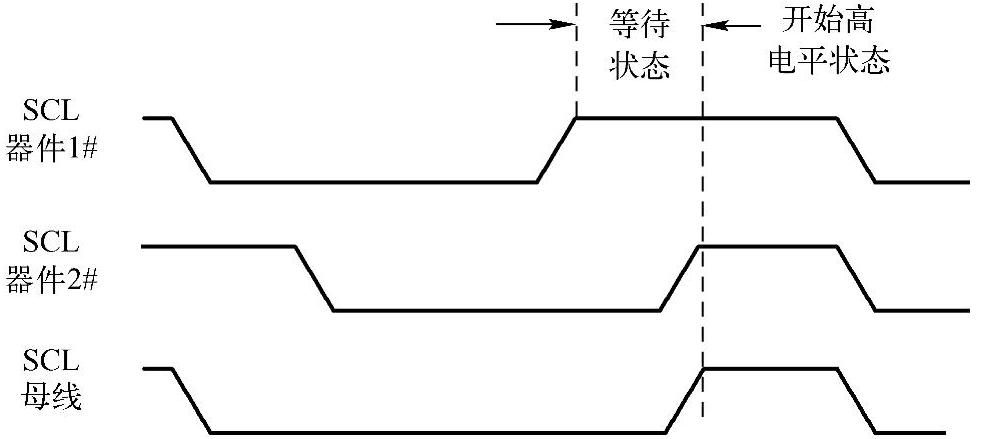

在通常情况下,只有一个主器件产生时钟信号SCL,而在仲裁程序中可以有两个或多个主器件。为了使输出数据具有比较性,时钟必须保持同步。图13-11给出了时钟同步时序图。SCL的线与意味着一旦有一个器件在SCL产生低电平信号,则其他器件也被强制为低电平,即在这个由高电平到低电平的过程中,其他器件产生的时钟强制置低电平,并且只要有器件的时钟信号为低则SCL一直保持低电平。只有总线SCL的低电平状态结束,其他器件时钟的低电平状态才可以结束。在变换为高电平状态之前,首先获得一个SCL的同步信号。该同步信号低电平状态的长度由最慢的器件时钟信号决定,高电平状态的长度由最快的器件时钟信号决定。

(https://www.daowen.com)

(https://www.daowen.com)

图13-11 仲裁过程中两个I2C模块时钟的同步

如果有器件需要将时钟信号强制拉低并保持一个较长的时间,那么其他时钟发生器都进入等待状态。在这种工作状态下,从器件将主器件的工作时钟变慢,并为储存接收的字节或发送字节创造了足够的时间。