死区生成子模块的控制和操作

2026年01月15日

2.死区生成子模块的控制和操作

死区生成子模块的控制寄存器有死区控制寄存器DBCTL、死区上升沿延迟寄存器DBRED和死区下降沿延迟寄存器DBFED。

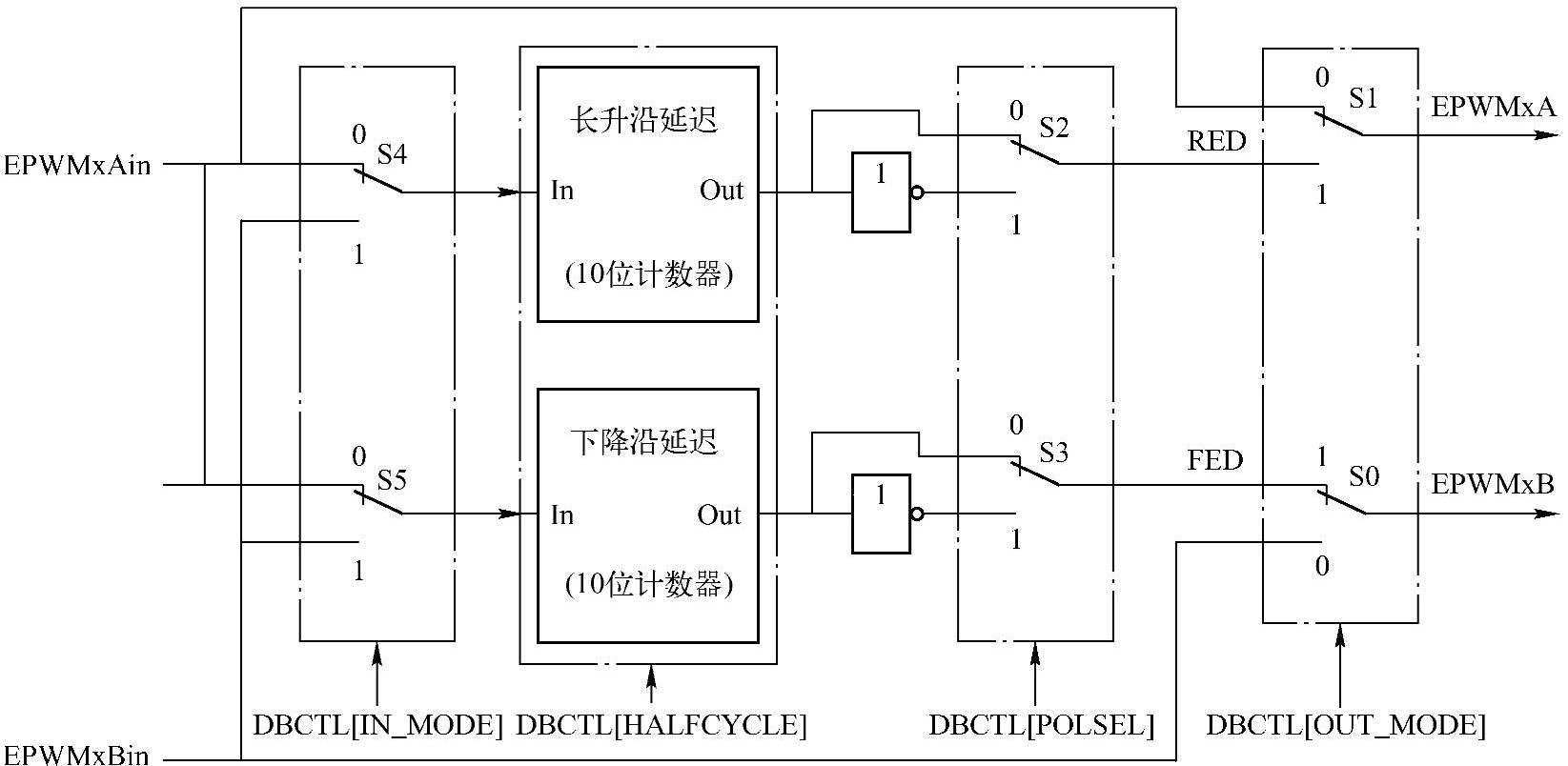

死区生成子模块有两组独立的开关S4、S5和S2、S3,如图7-8所示。

图7-8 死区生成子模块配置选择

●输入信号源选择。死区生成子模块的输入信号来自动作限定子模块输出的ePWMxA和ePWMxB信号,在此将指定哪个信号作为死区生成子模块的输入信号。通过DBCTL[IN_MODE]控制位,可以选择输入信号的延迟、上升沿(RED)、下降沿(FED):

ePWMxA输入信号为上升沿或下降沿延迟输入,这是系统复位时的默认模式。

ePWMxA输入信号为上升沿或下降沿延迟输入,这是系统复位时的默认模式。

ePWMxA输入信号为下降沿延迟输入,ePWMxB输入信号为上升沿延迟输入。

ePWMxA输入信号为下降沿延迟输入,ePWMxB输入信号为上升沿延迟输入。

ePWMxA输入信号为上升沿延迟输入,ePWMxB输入信号为下降沿延迟输入。

ePWMxA输入信号为上升沿延迟输入,ePWMxB输入信号为下降沿延迟输入。

ePWMxB输入信号为上升沿或下降沿延迟输入均可。(https://www.daowen.com)

ePWMxB输入信号为上升沿或下降沿延迟输入均可。(https://www.daowen.com)

●输出模式控制。输出模式控制位DBCTL[OUT_MODE]确定上升沿延迟、下降沿延迟,还是不延迟。

●极性控制。极性控制位DBCTL[POLSEL]确定上升沿延迟或下降沿延迟信号在送出死区生成子模块前是否取反。

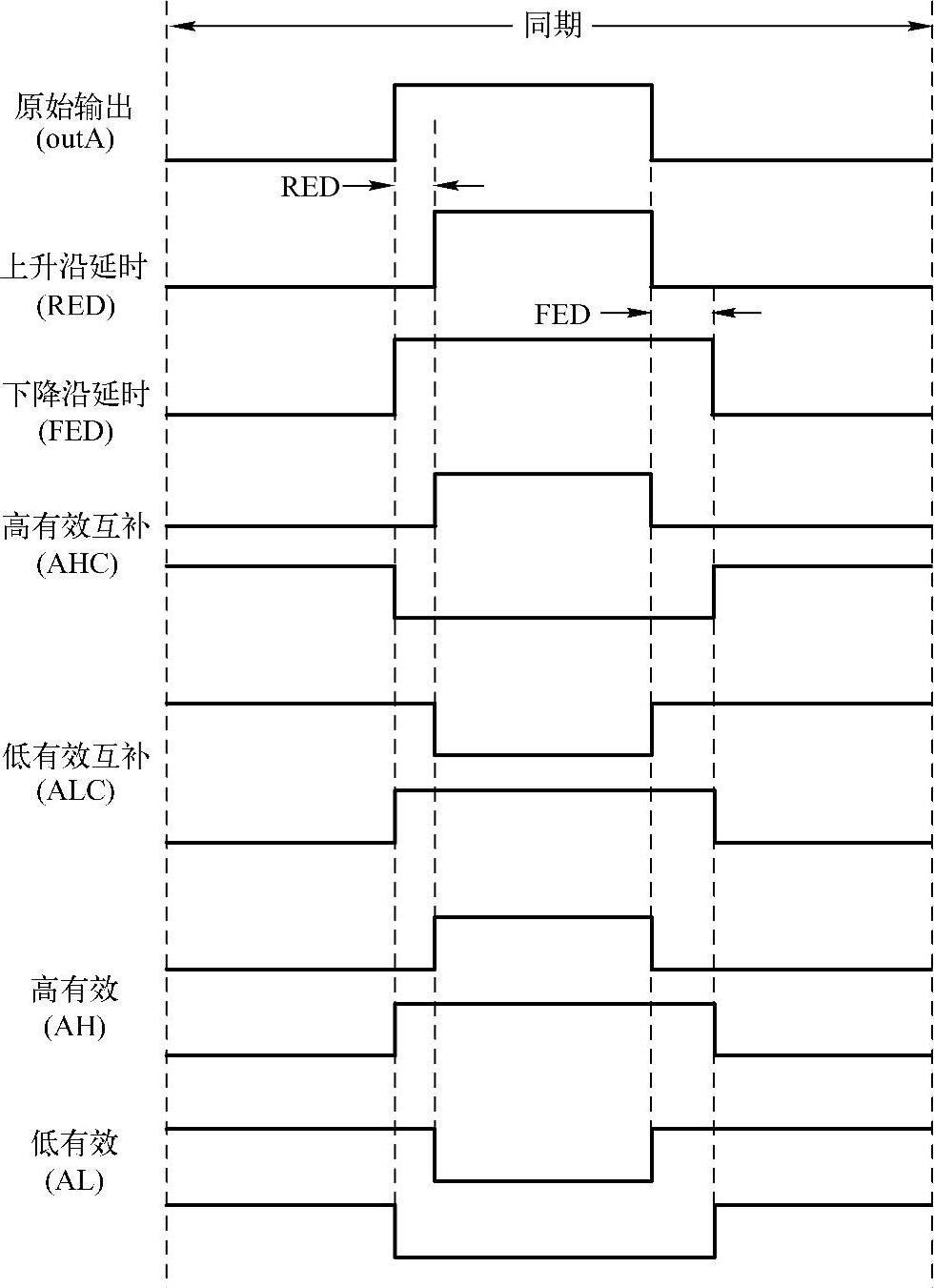

死区波形如图7-9所示。

死区生成子模块支持独立的上升沿和下降沿延迟。其延迟时间由DBRED寄存器和DBFED寄存器的值确定,这两个寄存器为10位宽度,其值表示时基时钟的个数,上升沿和下降延迟时间的计算公式分别为

FED=DBFED×TTBCLK

RED=DBRED×TTBCLK

式中,TTBCLK是时基时钟TBCLK的周期值,由系统时钟分频得到。

图7-9 典型的死区波形(0%<占空比<100%)