工程案例——函数信号发生器

设计函数信号发生器一共需要编写12个VHDL程序(*.vhd)、1个数据存储器文件(*.coe)、1个引脚约束文件(*.ucf)(如表1所示)。

表1 函数信号发生器中的相关文件及所涉及的理论知识

续表

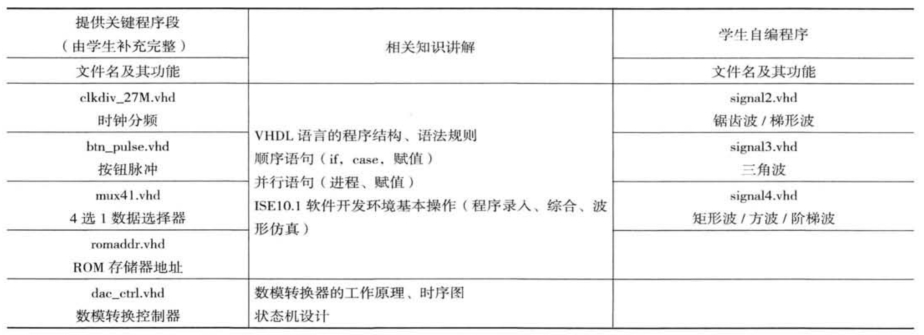

在前期录入功能模块的VHDL程序时,学生已经了解了每个模块的功能。将romaddr与romip两个模块按图1的关系连接起来,生成模块signal l,实现了在时钟clk__ s的作用下从romaddr的地址addr中读取romip中的正弦波数据dout,产生正弦信号,输出给sout。

图1 正弦信号发生器

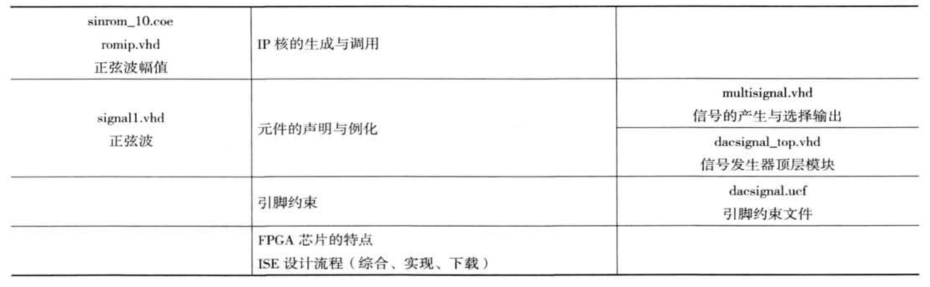

将btn_pulse、signall、signal2、signal3、signal4与mux41这6个模块按图2的关系连接起来,生成模块multisignal,实现信号的产生与选择输出。signall 、signal2、signal3、signal4分别产生四种不同的信号。当按钮btn被按下,btn_pulse产生脉冲信号pout,在pout的控制下,由mux4l选择四路信号中的一路输出给dout。

图2 信号的产生与选择输出模块

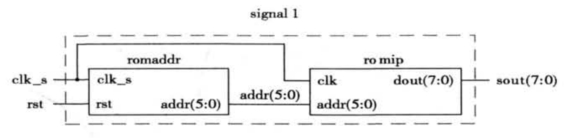

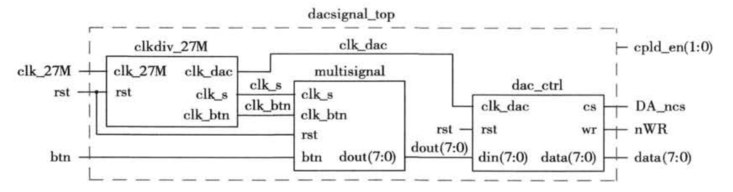

将clkdiv_27M、multisignal、dac_ctrl这3个模块按图3的关系连接起来,生成模块dacsignal_top,实现函数信号发生器。时钟分频模块clkdiv_27M为其他模块提供所需频率的时钟。数模转换控制器dac_ctrl的输出端cs、wr、data与实验平台上的数模转换芯片相连,控制该芯片将数字量转换成模拟量输出。

图3 函数信号发生器顶层文件

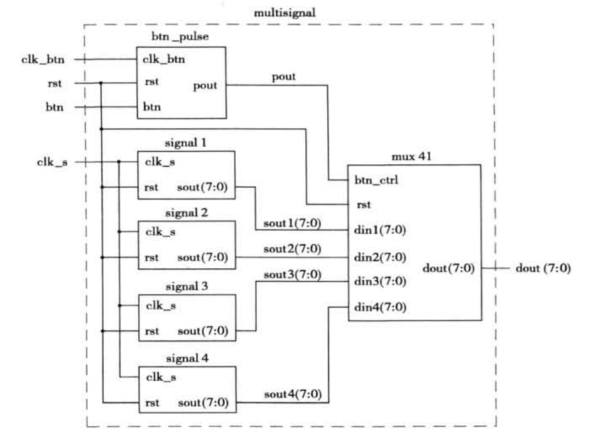

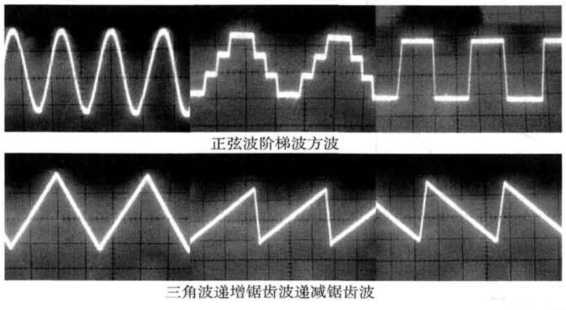

根据dacsignal_top的端口信息编写引脚约束文件dacsignal.ucf,使FPGA芯片与相应的外设相连。把电脑、实验平台、示波器连接好,按照ISE设计流程将文件下载到FPGA中,从而可以用示波器显示出信号的波形(如图4所示)。

图4 各种信号的示波器显示效果